简介

随着这几年AI应用和AI芯片的发展,AI已经成为市场的的热点,各个芯片公司均逐步推出具备特色的AI芯片以对市场进行争夺。当前的AI芯片快速发展,芯片设计复杂性呈现指数级增长。为了快速应对市场需求,并获得很好的PPA,使用AI辅助设计芯片已经成为主流趋势。今天我们盘点一下市场上的AI EDA工具。

Synopsys AI EDA

VSO

由于设计,约束,覆盖等在整个设计流程中,可能出现多次变换,而手动的regress可能在某些情况下很难提升覆盖,甚至无法提升覆盖率。case中也可能存在大量冗余的覆盖,这些都是存在的问题。仅靠人工去分析并尝试收敛覆盖,不仅消耗大量时间,面临巨大困难,而且结果却不一定能达到预期。

传统的覆盖率检查需要大量的人力反复的做一些重复的工作,不太容易在困难点实现覆盖率的提升。

Synopsys VSO.ai™(验证空间优化)提供业界首个人工智能驱动的验证解决方案,帮助验证团队更快、更高质量地实现覆盖收敛。该系统自主工作,以尽可能快、尽可能低成本地达到覆盖目标,并获得最高质量的结果。机器学习技术用于识别和消除回归中的冗余,自动进行覆盖率根本原因分析,并从 RTL 和激励中推断覆盖率,以识别覆盖率差距并提供覆盖率指导。

DSO

伴随着当前IC市场窗口的缩小,以及当前设计变得更为复杂的背景。为了实现最佳功耗、性能和面积 (PPA) 目标,相对简单的人工优化已经无法适应当前的IC设计流程快速以及高质量的要求。

Synopsys DSO.ai 是业界首款用于芯片设计的自主人工智能应用,可在芯片设计的超大解决方案空间中搜索优化目标,利用强化学习优化功耗、性能和面积(PPA)。RTL-to-GDSII 全流程优化可释放逻辑域和物理域的 PPA 潜力。突破性的强化学习引擎可以探索数万亿个设计方案。这些模型在整个设计周期中持续训练并加速收敛,从而影响迭代设计的效率和生产力。

TSO

设计的复杂性和规模不断增加,也给硅测试流程带来了压力。在评估自动测试模式生成 (ATPG) 工具的结果时,缺陷覆盖率、模式数(直接与测试成本相关)和运行时间是需要考虑的三个关键指标。

传统上,优化其中一个指标(通常是手工操作)会对其他指标产生负面影响。刚接触 ATPG 的人可能不太清楚如何调整工具以生成所需的程序结果。相反,经验丰富的人可能会有偏差,导致工具设置达到某种结果,而这种结果对于新设计来说可能并不是最佳的。

Synopsys TSO.ai 是业界首个用于半导体测试的自主人工智能应用,可最大限度地降低测试成本,缩短当今复杂设计的上市时间。TSO.ai 可在大型测试搜索空间中自动搜索最佳解决方案,以最大限度地减少模式(pattern)数量和 ATPG 的周转(turn-around)时间,从而大幅降低测试成本并减少取得成果的时间。

ASO

传统的模拟工作流程是高度手动和迭代式的,而数字工作流程通常是自动化的,两者相比,生产率存在巨大差距。Synopsys ASO.ai 带来了一套丰富的人工智能模拟自动化功能和解决方案,以提高模拟设计、仿真、验证和实现工作流程的生产率。这些新的基于人工智能的自动化功能可帮助模拟设计团队重新利用数十年的知识和经验来开发最先进的模拟 IP。

模拟设计迁移-跨技术节点快速迁移分层模拟 IP,包括原理图自动迁移和基于知识学习的自动布局迁移。

布局感知设计优化-多目标优化代理可在运行过程中学习,帮助工程师同时在数百个 PVT 角落和多个测试中优化模拟设计。基于人工智能的优化器可用于布局前和布局后寄生网表,以快速收敛并满足设计规范。

智能仿真分析--帮助工程师快速理解海量角落和多测试台仿真数据中错综复杂的信号级行为,而这些行为在基于表达式的仿真分析中是无法捕捉到的,也很难通过查看波形来识别。

这里的模拟设计迁移技术据我了解应该是模拟行业关注的关键技术之一,如果ASO真的像Synopsys表述的那样优秀,这对加速模拟芯片的上市具有非常重要的意义。而布局和仿真的优化同样能够减少大量人工以及减少时间成本。

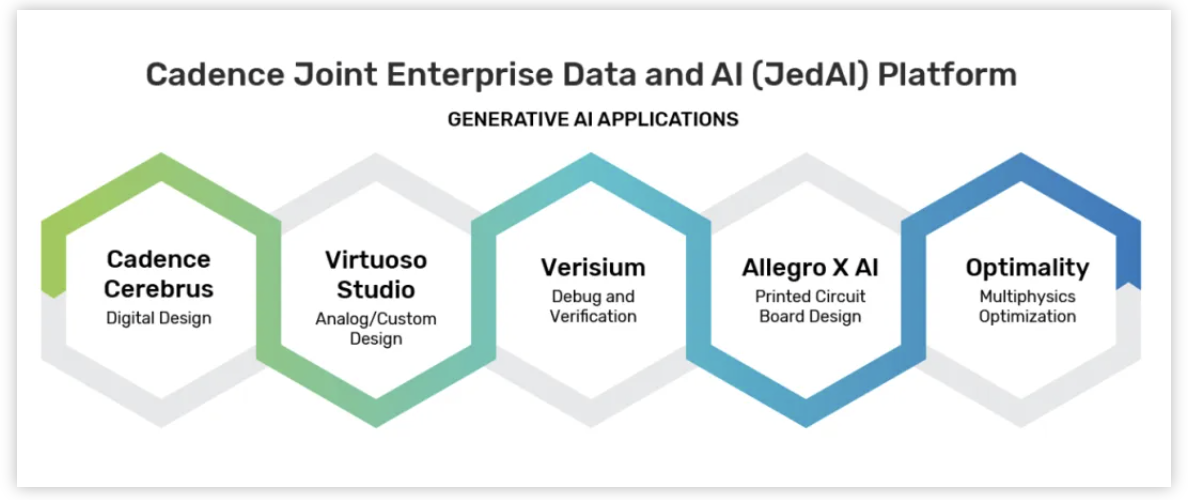

Cadence AI EDA

Cerebrus

Cadence Cerebrus智能芯片资源管理器是一种革命性的人工智能(AI)驱动的IC设计流程自动优化方法。工程师指定设计目标,Cadence Cerebrus的生成式人工智能功能将智能优化设计,以完全自动化的方式以满足这些功耗、性能和面积(PPA)目标。这个工具对标是类似Synopsys的DSO工具,具体的效果目前没有测试过。

Virtuoso Studio

这个是Cadence新出的平台,据介绍是从底层重新优化的模拟平台,集成了AI工具以助力模拟的研发,原本Cadence在模拟方向就处在领先地位,这些工具的产生再次巩固其在模拟IC领域的领先地位。

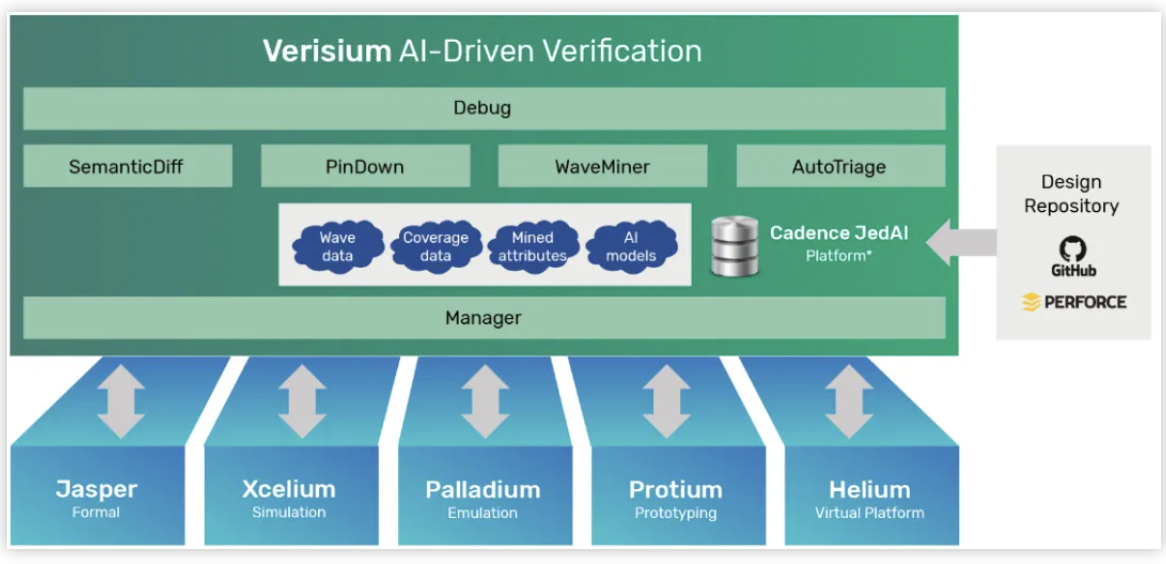

Verisium

这个是近些年Cadence发布的Debug验证系统平台,内部集成了Debug工具,Manager,AutoTriage,SemanticDiff,WaveMiner,PinDown等工具,如下图所示,是一个完整的平台套件。

Debug:之前Indago的升级版本,从单次运行到多次运行的全面调试解决方案,利用波形、原理图、驱动程序跟踪和SmartLog技术提供快速交互式和后处理调试。

PinDown:与 Cadence JedAI 平台和行业标准修订控制系统集成,建立源代码变更、测试报告和日志文件的人工智能模型,以预测哪些源代码检入最有可能导致故障。

SemanticDiff:提供一种算法解决方案,用于比较 IP 或 SoC 的多个源代码修订版本,对这些修订版本进行分类,并对哪些更新对系统行为的破坏性最大进行排序,以帮助找出潜在的漏洞点。

结语

各个EDA厂商对人工智能的重视程度不言而喻,目前的IC设计流程变得更加复杂,人工智能的加入对于加快产品迭代意义非凡,不仅是芯片本身进入AI时代,设计芯片的流程也开始进入AI时代。为了应对当前芯片市场窗口的缩小,使用AI工具来提升复杂IC效率是当前行业内的趋势。

作者:亦安QAQ

文章来源:亦安的数字小站

推荐阅读

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。