提纲

1. 参考模型的含义和相关的概念。

2. 参考模型要不要带时序?

3. 几种参考模型的示例。

IC验证工程师两只手,一个抓规格特性SPEC,另一个抓SV UVM TestBench。而TestBench的一个很重要的组成部分就是参考模型。

参考模型,英文是reference model,简称RM。通常在模块级验证(BT)或者单元验证(UT)中,IC验证工程师根据自己对业务和规格特性的理解,使用比硬件描述语言Verilog/VHDL较抽象的语言,例如System Verilog或MATLAB,实现设计模块的功能和特性。这种实现就是参考模型。

参考模型是逻辑模块的功能的等效。用来与逻辑模块进行比较,以证明逻辑设计的正确性。逻辑模块的功能特性也不是非要IC验证工程师来开发,也可以集成第三方的设计,例如验证某些算法逻辑时,使用的参考模型,就是由算法工程师开发的Matlab模型。但是,这个参考模型一定不能由逻辑设计工程师自己开发。

这是为什么呢?

鲁迅先生说过,这世间本没有路,走的人多了也便有了路。其实这世间也本没有IC验证工程师,逻辑电路写好之后,IC设计工程师自己随便给逻辑输入一些测试激励,看看输出时序是否满足要求就可以了。后来集成电路发展了,复杂度提升了,不能仅仅通过简单的灌入测试激励就保证逻辑的正确性,需要专门的人来验证逻辑电路的正确性。开发逻辑电路与开发软件最大的不同是,一旦电路开发完成,做成芯片,就不能再改。因此必须要保证验证的充分性和完备性。人的思维往往有一定的局限性,在一个复杂的设计之中,往往存在一些隐秘的角落,考虑不全,难以覆盖。面对这样的复杂设计,若由两个人分别从各自独立的角度思考,犯同一个错误的概率也是比任意一个人犯错的概率也大大的减少。因此便有了IC验证工程师。

我思故我在。能独立思考而不被IC设计工程师引诱和牵绊,是IC验证工程师存在的最大的价值和意义。

为什么要使用参考模型?参考模型存在的意义是什么?

从辩证法角度看,这是抽象和具体的又一个示例。我们在描述一件事物的时候,抽象能够保证正确性,具体能够保证准确性。越抽象越正确,越具体越准确。例如夸赞一个人的时候,说:她是一个好姑娘。单一个“好”字,足够抽象,也绝对正确。又说:她是一个善良可爱的好姑娘。比较抽象,但不具体。绝大多数人会认为在夸她,但也有可能被误解为暗指她长得丑。这种夸赞也不够生动具体,到底怎样的善良,又有多可爱,并没有表述清楚。又说:她是一个视金钱如粪土,为朋友两肋插刀的好姑娘。这个描述非常具体,把这个姑娘的“好”描述的非常准确和生动形象。可是抽象性很弱,正确性就难以保证了。这姑娘是挺好,可是咋不像女的呢

再例如这篇浅谈参考模型的赘述。如果我记忆力够强大,把我写过的参考模型的代码直接贴到这里,简单直接,十分具体。可是我的代码就足够代表参考模型设计的含义吗?显然不能。

逻辑电路是对规格特性的具体而准确的实现,准确是是首要的。参考模型是为了验证逻辑电路而专门设计的,对规格特性的正确性模拟是首要的。因此,写参考模型的时候,要考虑增加其抽象性,而减少其具体性。因为抽象性越高,其正确性越能够保证。

举个例子。在基带芯片的验证过程中。各个算法逻辑模块的参考模型的实现,有两种选择,IC验证工程师根据算法的理解和规格文档用SV语言开发,或者用算法工程师写的MATLAB模型。这两种方法都比RTL设计,抽象性高,正确性也高。SV与MATLAB相比,抽象性略低,因此正确性略低,但准确性要高一些。项目组没有定死,可灵活选用。但俗话说的好,小孩子才选择,大人全都要。最好是在BT/UT中两种方式都实现,与RTL做到三方比对。三个人错在一起的概率会更小。对于调制解调子系统的正确性,则只能通过抽象性较高的MATLAB模型来保证了。

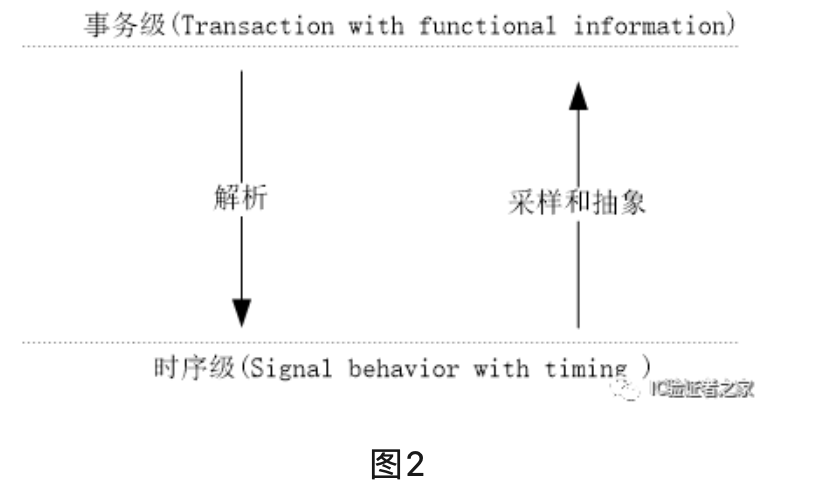

从抽象和具体的关系上看,在参考模型这加入时序,是不好的。时序的引入,将抽象的事物级描述,变为比较具体的时序级表述。准确性上有提升,但正确性上会打折扣。这也是为什么带时序的参考模型不够鲁棒,不好调试,不易适配RTL的改动的根本原因。

关于事物级和时序级的关系,如下图所示。事物级是对时序级的抽象,时序级是事物级的具体实现。

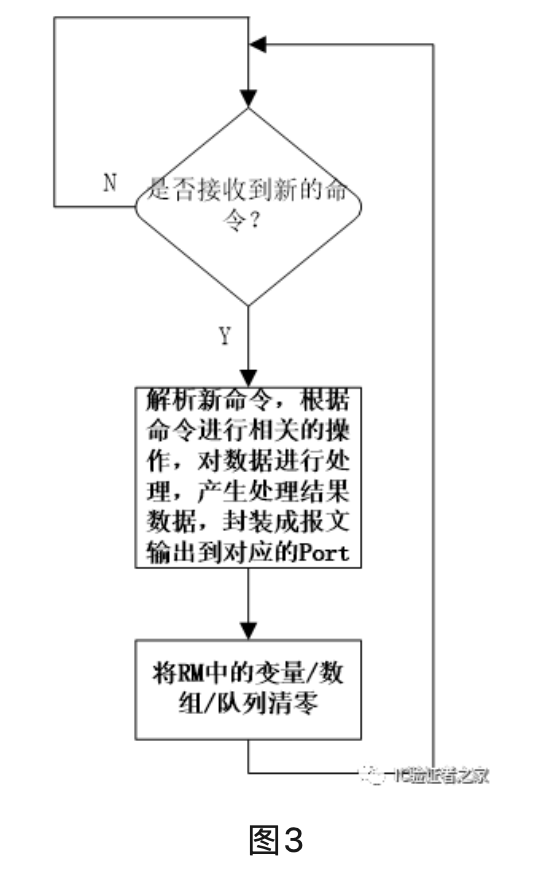

我本来想把之前写过的,见过的参考模型梳理归类,逐一罗列。如此这般,一来繁琐冗余,难以列全,二来过于具体,容易出错。将参考模型抽象为如下的一副流程图,如图3所示。

参考模型的功能概括为以下四点:

第一、参考模型是一个死循环,不休不止。如果没有业务报文或命令到达,则等待。如果有,则进行解析和处理,完成之后,继续等待新的命令或报文。

第二、参考模型处理的是事务级报文,没有时序,没有延迟。从接收到命令或报文,到完成处理,耗时为0。

第三、参考模型的输入和输出都是传输报文的TLM端口,通常扩展自UVM component。

第四、参考模型处理完成一个报文或命令后,使用到的变量或缓存队列,数组等都应该清零。

作者:一只特立独行的猪

文章来源:IC验证者之家

推荐阅读

- Arm中的TLB

- CPU多层caches的allocation方式

- PCIE,USB,SATA ,Ethernet 都在用的SerDes到底是个啥?

- 搞芯片,不懂逻辑综合是啥?

- IC各细分领域公司简介以及薪资调研(GPU篇)

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。