✎ 编 者 按

ARM所推出的AMBA4总线相对来讲还是应用广泛的。无论是芯片设计里还是FPGA设计里,时常能见到AMBA4总线的身影。在验证领域,SystemVerilog Asseration还是一个很常见的验证手段。在Xilinx Vivado中有提供AMBA总线相关的Checker VIP,其内部也是采用的SystemVerilog Asseration来实现。今天给大家推荐下ARM自家所推出的BP063 AMBA4 SVA组件。

》获取方式

可通过下方的“阅读原文”跳转至ARM官网对应的链接,需通过注册ARM账号来获取相关文件。

若不想注册账号,我在github上也上传了一份,也可通过github进行下载:

https://github.com/xiaochuang-lxc/AMBA-SVA

》使用

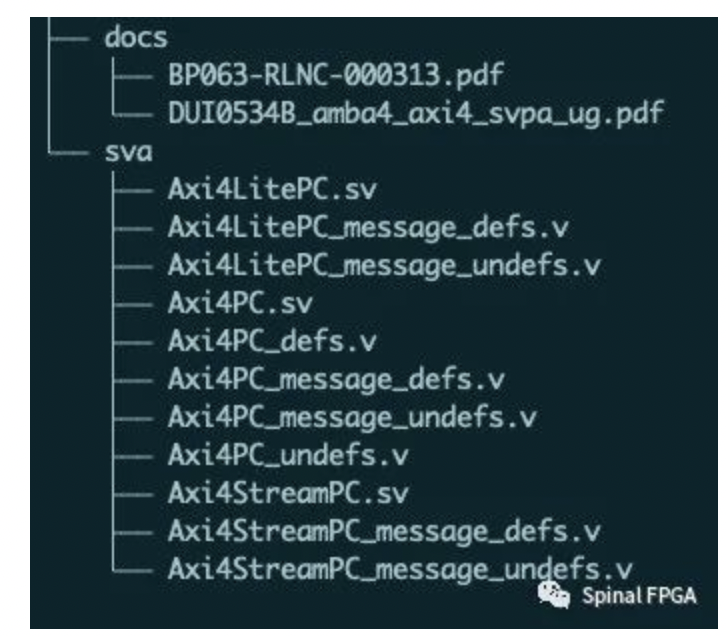

下载下来后文件夹里包含了sva文件和docs资料:

详细的使用教程可以参照文件夹里面的BP063-RLNC-000313.pdf,这里就不在照本宣科的给从头到尾讲了,文档中已详细说明了如何使用及各种参数的配置。

》One More Thing

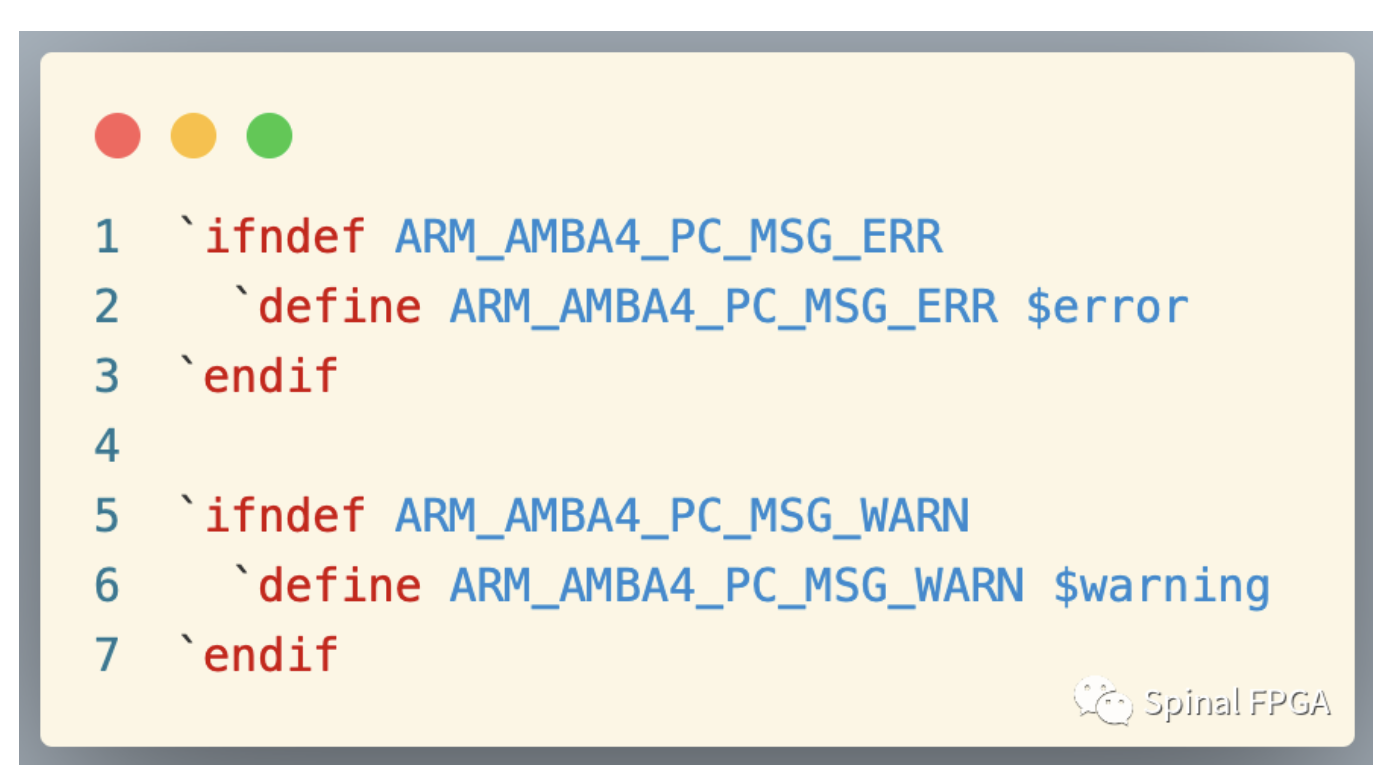

参照文档基本可以保证能够正常使用。对于SVA而言,其本质无非是通过各种规则进行检查,若不符合情况则根据错误等级进行报错。在ARM AMBA4 SVA里面,出错后的错误等级分为了$error和$warning两种:

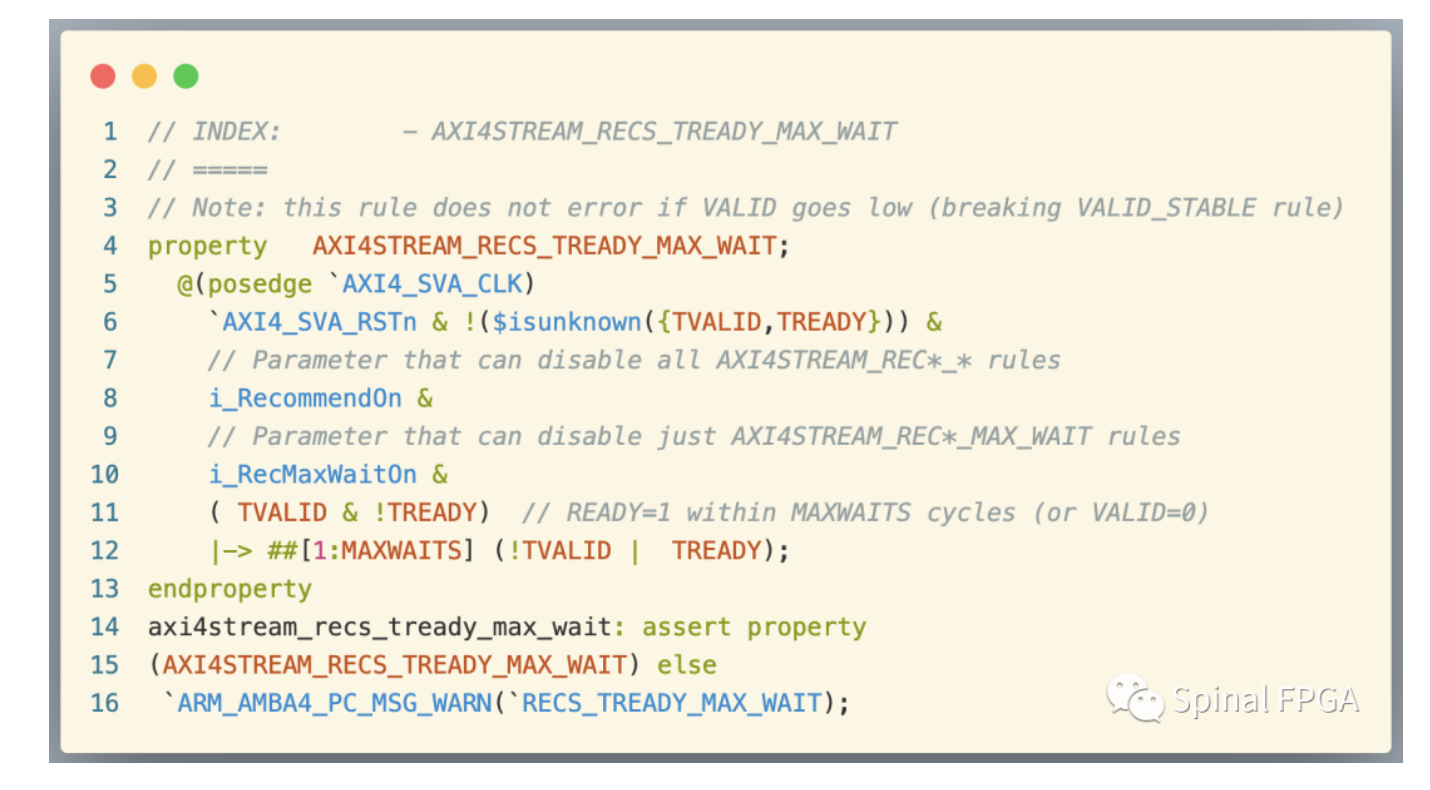

在仿真器执行时,对于$warning其只是打印信息,并不会影响仿真器继续向下执行。如果对于一些规则检测,如果你觉得使用$warning并不符合需要,则可以手动对源代码进行修改。例如下面对于ready超时的检测:

这里当仿真时不符合设计预期时会通过\`ARM_AMBA4_PC_MSG_WARN来进行$warning报警,如果需要出错时仿真立即停下来那么则可以将其替换更改为\`ARM_AMBA4_PC_MSG_ERR。

作者:玉骐

原文链接:Spinal FPGA

微信公众号:

推荐阅读

- Dispatcher By Round Robin

- Efficient Parsers on FPGA

- 二合一:ROM初始化放置到RTL中

- FPGAer浅入浅出DDR——容量规格篇(一)

- 偷点儿小懒 —— Stream 总线类模版

更多SpinalHDL技术干货请关注Spinal FPGA欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。