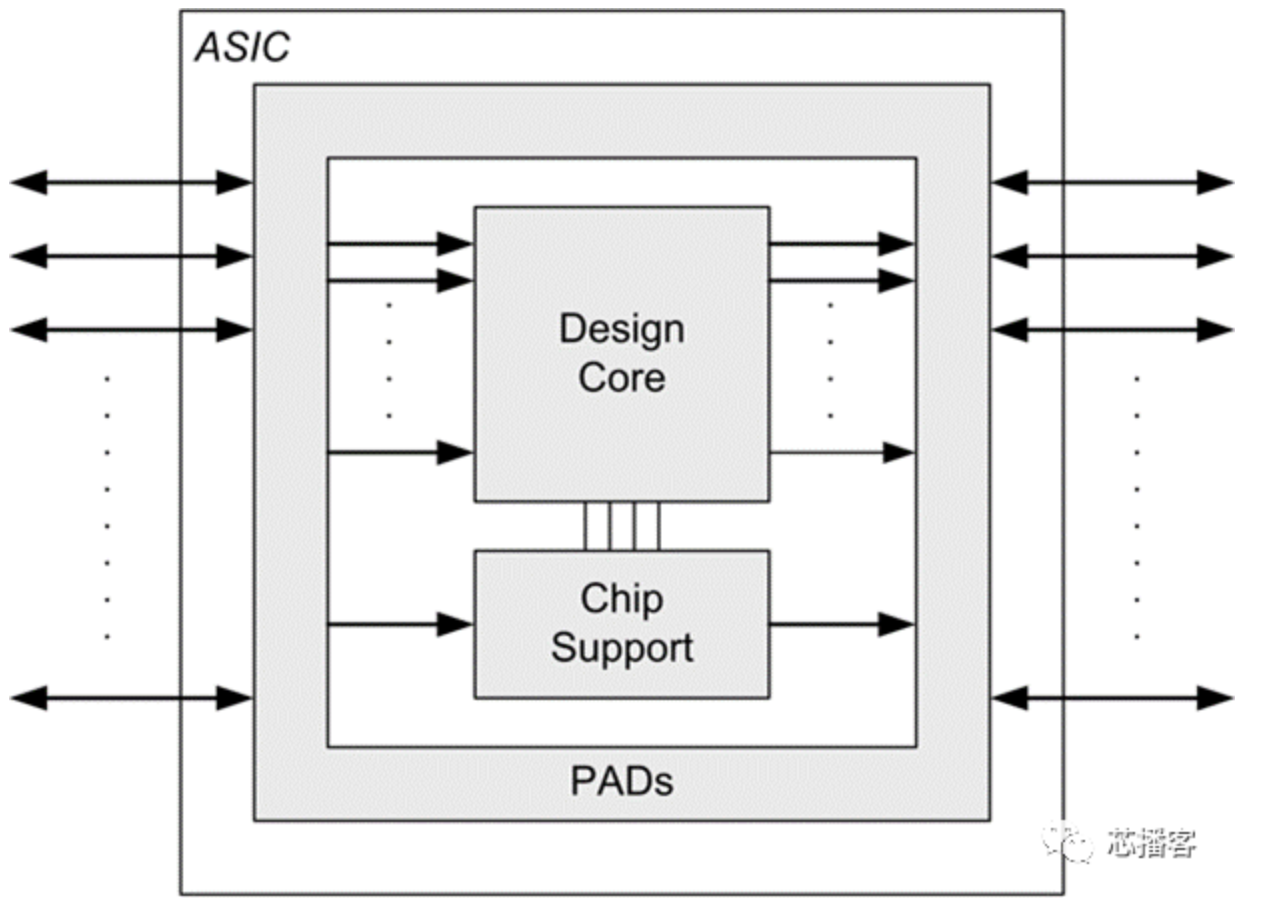

FPGA原型验证系统要尽可能多的复用SoC相关的模块,这样才是复刻SoC原型的意义所在。通常,许多SoC中设计的方式在FPGA中其实是不能通用的,在SoC设计的顶层,主要包括SoC芯片外设元件和顶层的IO PAD实例。典型的SoC顶层的简化视图如下所示:

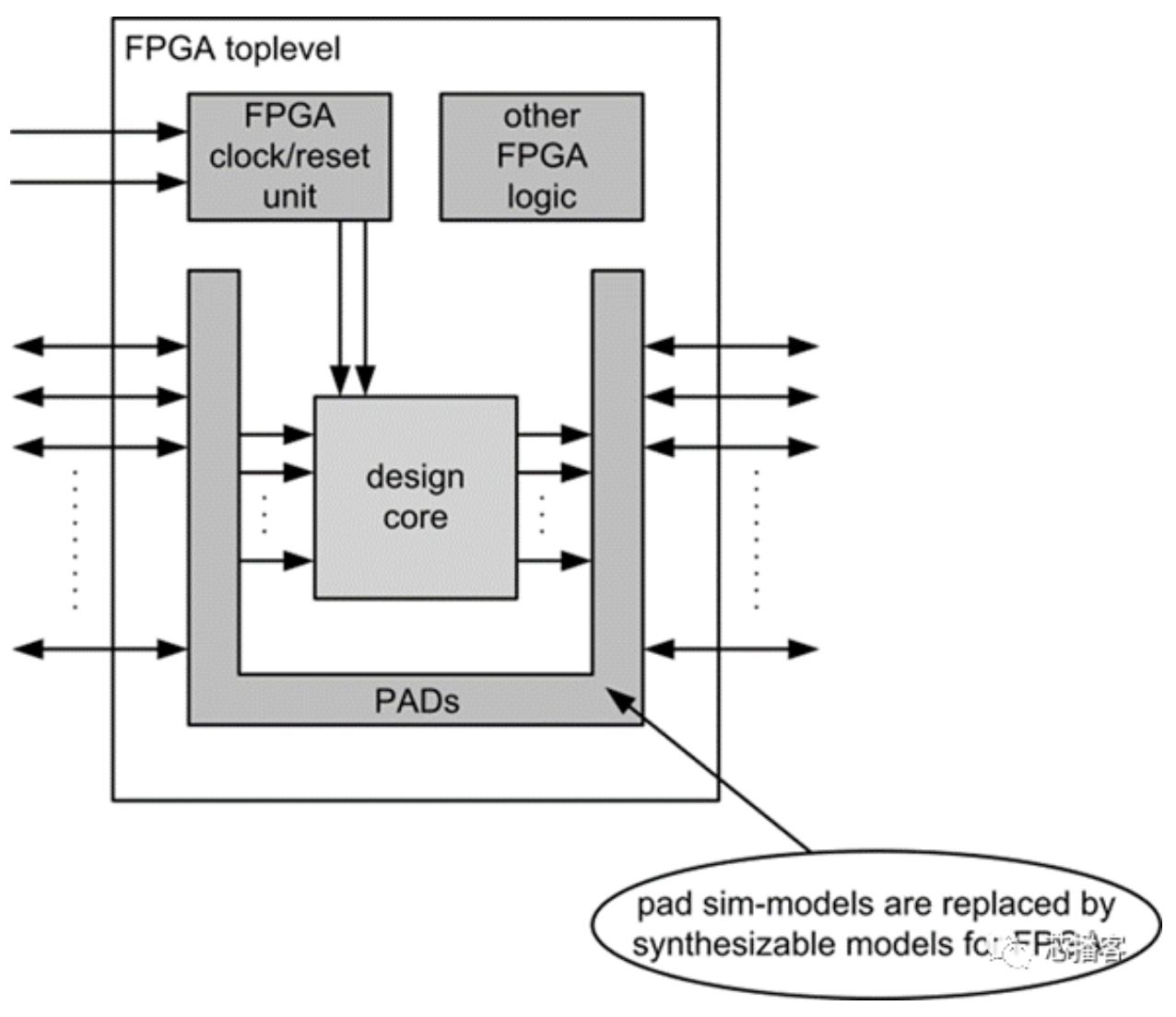

为了将这种SoC设计顺利移植到FPGA,我们需要用FPGA中现有的等效物替换图中所示的Chip Support和IO PAD,或者简单地完全移除顶层,并用新的FPGA里面特有的单元顶层封装Design Core。

RTL中的IO PAD实例化的代码在FPGA中是不能被综合的,并且FPGA中其实是不需要再将SoC代码中的IO PAD综合的,因为综合工具根据相关设置能够将相应的SoC的IO映射到FPGA的IO PAD,在大多数情况下只需要做绑定FPGA管脚的配置,并用其FPGA等效实物的可综合模型替换每个SoC的IO PAD实例。

ASIC的工艺厂商技术库中的典型IO焊盘在其边界处可能有20个或更多的连接,包括主输入和输出加上电压和转换控制以及扫描测试。其中一些连接将连接到封装引脚/球,而另一些连接到设计的核心或直接连接到相邻的焊盘。为了进行FPGA原型设计,我们只需要对从设计核心到“外部”世界的逻辑连接进行建模。因此,我们只需要一种更简单的焊盘形式来实现逻辑连接,省略扫描等。我们写一个小RTL文件,该文件适合SoC

RTL中的IO PAD实例化,但包含等效的FPGA子集,这将黑盒PAD实例化转换为FPGA可综合的。尽管SoC中可能有一千多个PAD,但可能只有十种或更多不同类型的PAD。用FPGA等效可综合逻辑代码替换每种类型将相对简单,特别是如果我们的SoC设计在多个项目中使用相同的PAD库,我们可以建立一个小的等效逻辑库。

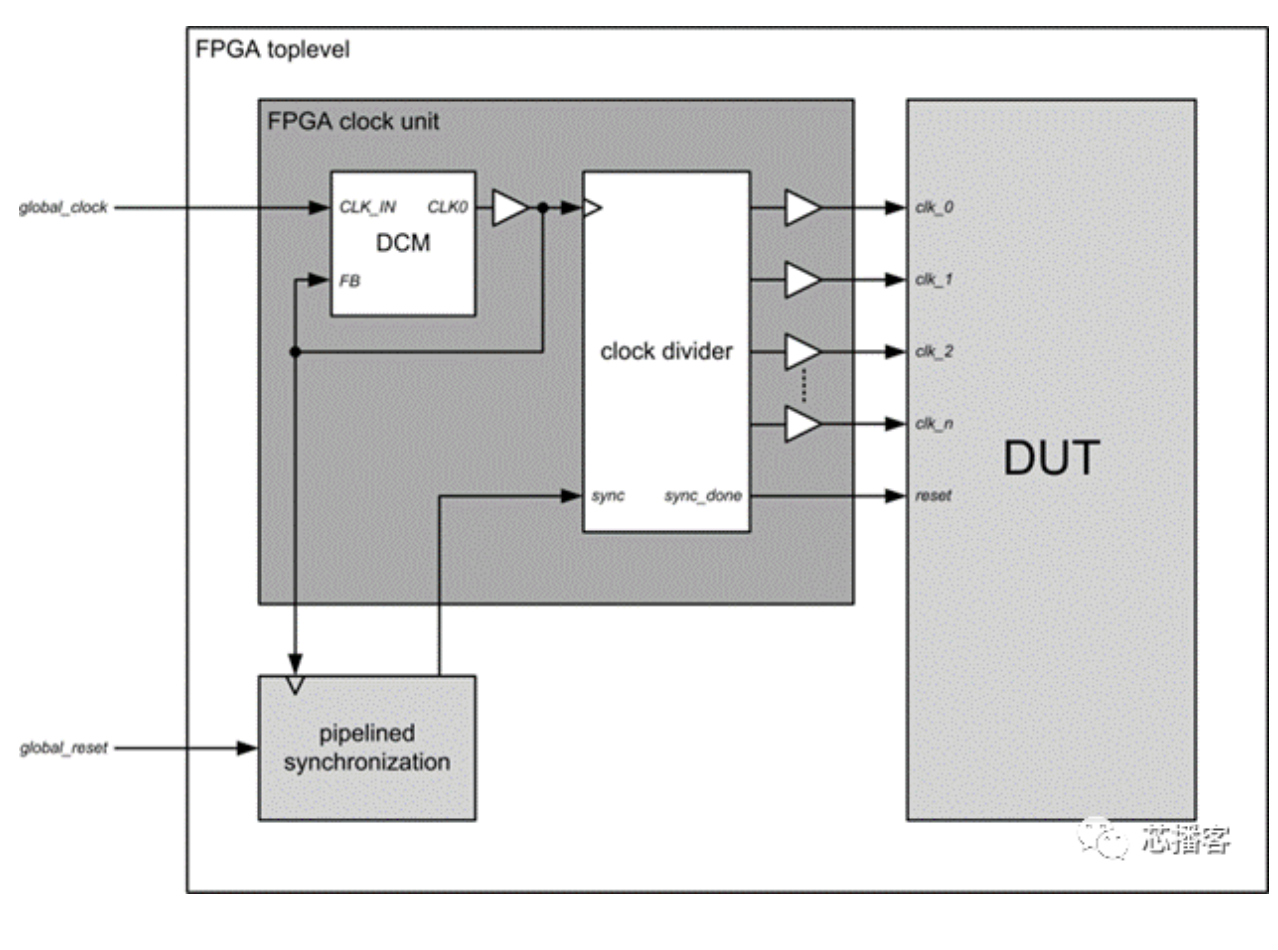

上图中标记为“Design Support”的块包含设计中通常特定于目标的元素,通常被视为SoC的RTL代码主要功能的次要元素,但对其功能正确至关重要。这可能包括时钟生成和分配、复位控制和同步、电源门控以及测试和调试控制等功能。一些团队建议简单地用另一个更简单的块替换Design Support块,该块负责FPGA所需的元件。这意味着,实际上我们有一个新的FPGA兼容版本的SoC顶层。SoC的顶层RTL文件可以用作新FPGA顶层的基础,下图中的框图显示了新顶层的示例,可以看到顶层的时钟生成和同步电路图。

支持现有设计核心。等效FPGA芯片支持块的创建是一项相对简单的FPGA设计任务,涉及分频器、时钟缓冲器和同步器,当原型使用多片FPGA时,FPGA时钟网络的使用变得更加复杂。

原文:芯播客

作者: Jacky Yu

相关文章推荐

- 【芯知识】多片FPGA原型验证系统互连拓扑分析

- ICer必备技能,一文带你了解Python的使用!

- 一份MCU的验证计划,大家看看全不全?

- 浅谈验证平台的通讯机制

- UVM中add_typewide_sequence和add_sequence的区别

- 灵动微课堂 |开源项目:基于MM32F0160微控制器的机械键盘

更多FPGA干货请关注IC设计技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。