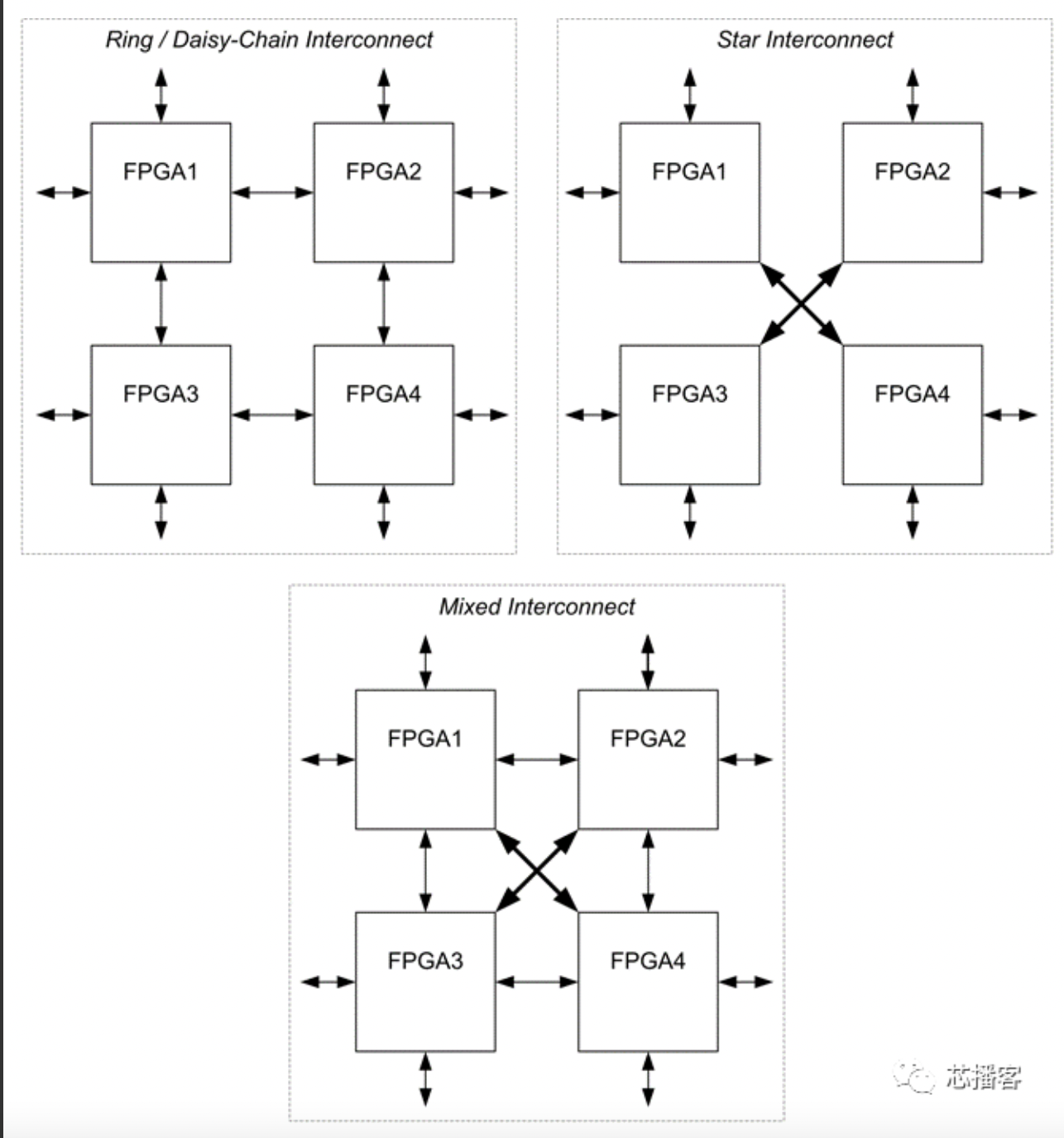

多片FPGA的原型验证系统的性能和容量通常受到FPGA间连接的限制。FPGA中有大量的资源,但IO引脚的数量受封装技术的限制,通常只有1000个左右的用户IO引脚。然后,这1000个引脚需要连接到其他FPGA或板上的外围设备,以形成尽可能普遍适用的互连网络,但这应该是什么样子?引脚应该以菊花链环形排列的形式连接各个FPGA,还是所有FPGA引脚都应该以星形连接在一起?FPGA是否应仅链接到相邻的FPGA,或者是否应做出一些规定以链接到更多远程设备?

其实,每中连接方式都有优点和缺点。

菊花链互连要求信号通过FPGA本身以连接远程设备。这种直通连接不仅限制了其他信号的引脚可用性,而且还显著增加了整体路径延迟。依赖于直通互连的电路板或系统通常比其他类型的电路板运行得更慢。然而,这样的电路板可能适合于一种由单个宽数据路径主导的设计,很少或没有分支。

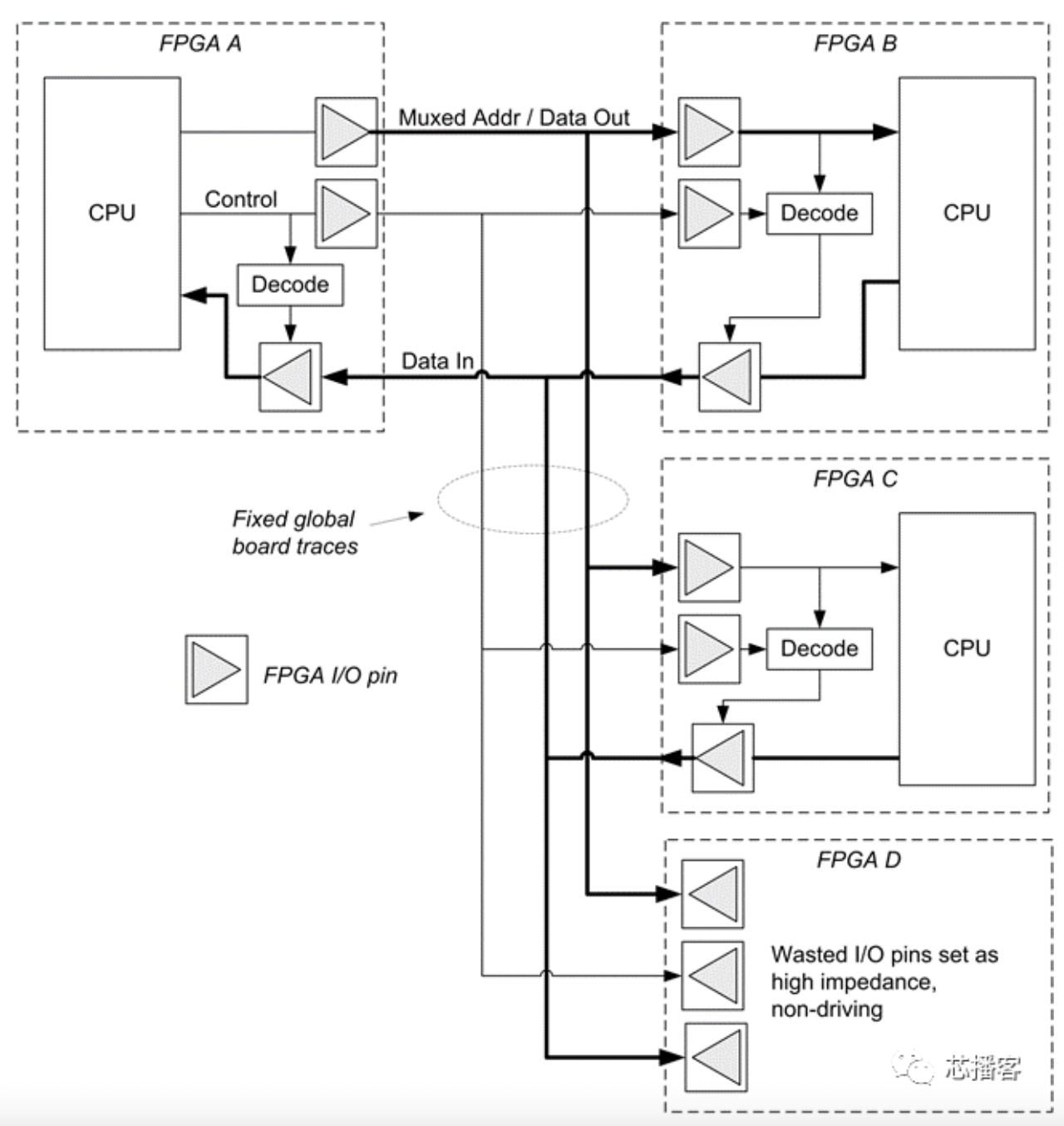

星形连接的使用可能更快,因为任何FPGA都可以通过直接导线驱动任何其他FPGA,但星形连接通常使用FPGA引脚的效率最低。如下图所示。可以看到一个简单的多路复用总线上的三个设计块是如何被划分为一个板上四个FPGA中的三个,其中板采用基于星形的固定互连。由于直接连接,三个块之间的连接将是高速的,但第四个FPGA上的许多引脚将被浪费。此外,这些未使用的引脚将需要配置为高阻抗,以便不干扰期望的信号。如果第四个FPGA将用于设计的另一部分,那么这种引脚浪费可能非常严重,并且可能会对将设计的其余部分映射到剩余资源的能力产生很大影响。

如果电路板是在内部设计和制造的,我们可以根据需要精确地安排互连,以满足原型项目的需求。互连通常类似于SoC设计的顶层框图,特别是当使用原型设计方法来简化将顶层SoC块划分为FPGA时。这种自由度可能会为该原型项目产生最佳的互连布置,但对于后续项目来说可能是次优的。此外,如果SoC设计在发展过程中发生变化,则在原型项目开始时修复互连资源可能会导致问题。

同样,具有固定互连的商用原型验证板不太可能满足给定项目的确切需求,因此需要做出妥协。典型的在许多商用原型验证板上找到的解决方案是前面提到的直接互连布置之间的混合。

理想的互连拓扑是什么

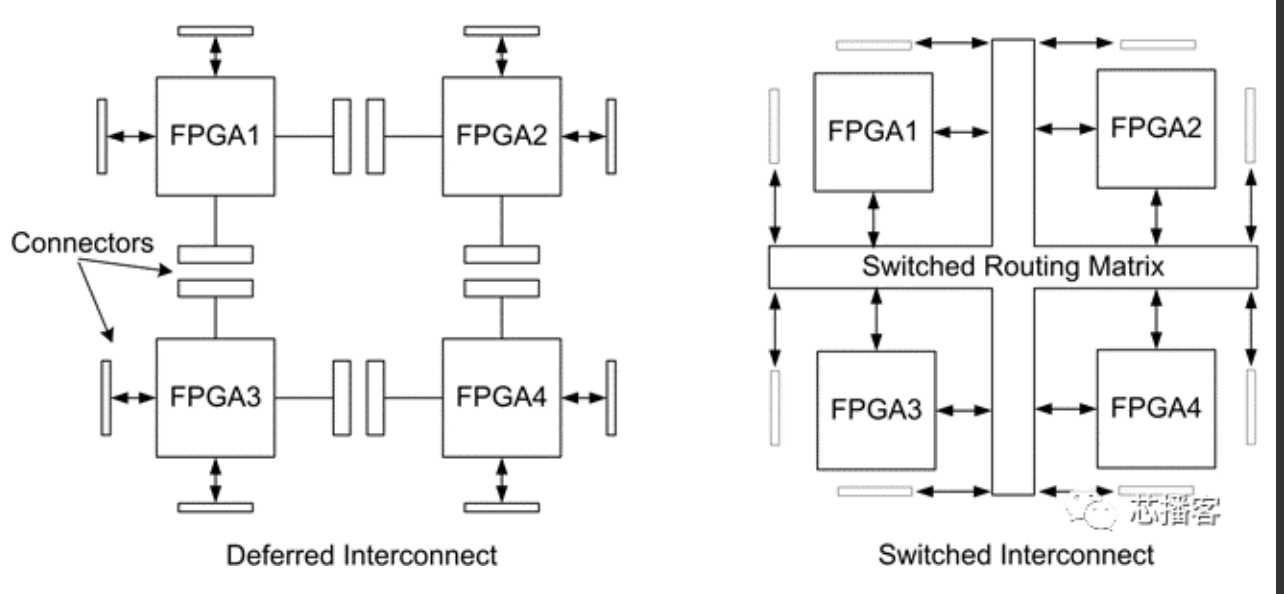

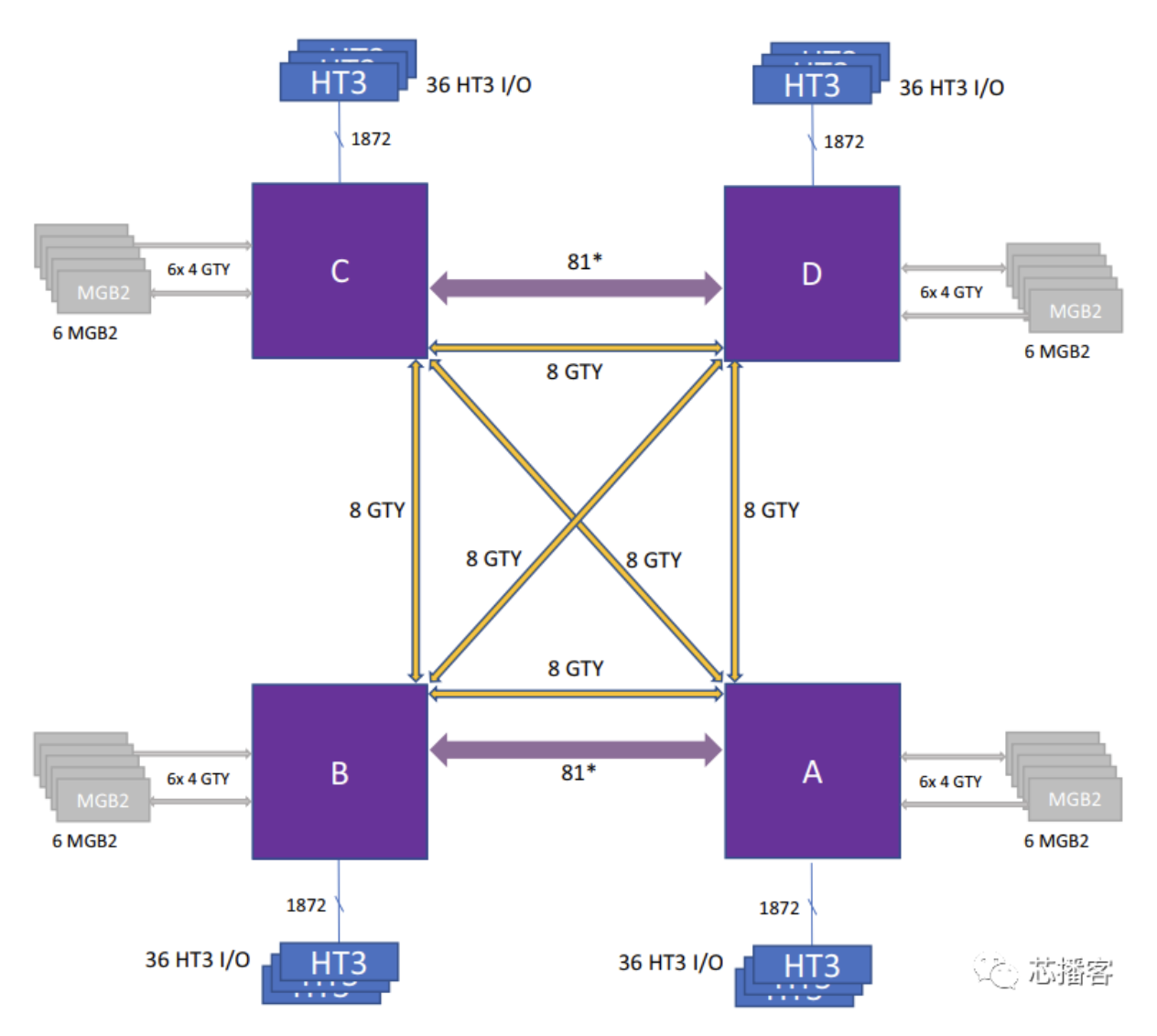

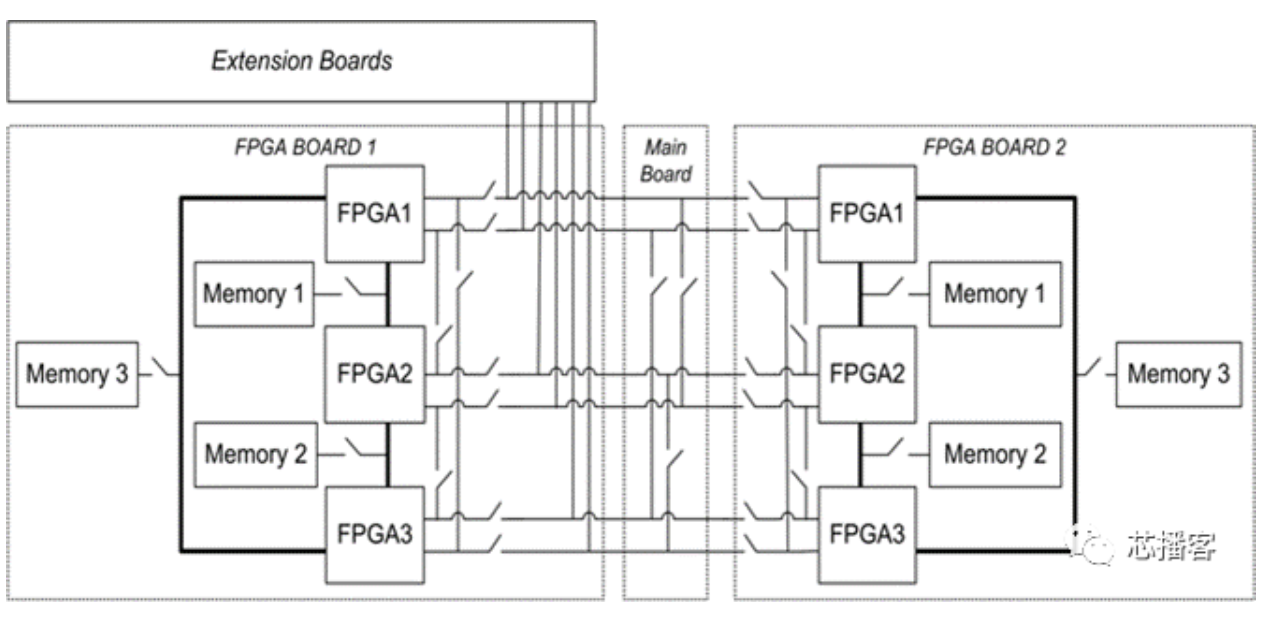

我们正在寻求尽可能灵活的互连布置,但要有高性能,并且也可以尽可能地定制,以满足给定原型项目的互连需求。供应商应理解这些明显矛盾的需求所推断出的妥协,并应尽量选择适用于尽可能多的最终用户项目的最佳互连安排。最灵活的解决方案是使用某种形式的间接互连,其中两个最常见的示例如下图所示。这两个例子是延迟互连和交换互连。

在延迟互连拓扑中,FPGA之间的固定连接相对较少,但每个FPGA引脚都被路由到附近的连接器。然后,根据每个特定项目的需要,使用其他介质(某些类型的连接器板或柔性电缆)连接这些连接器。例如,在上图中,我们看到了一种连接器布置,通过在每个FPGA的多个连接器之间使用连接电缆,可以在FPGA

1和FPGA 4之间进行大量连接。如果需要,堆叠连接器仍允许多个点之间的星形连接。

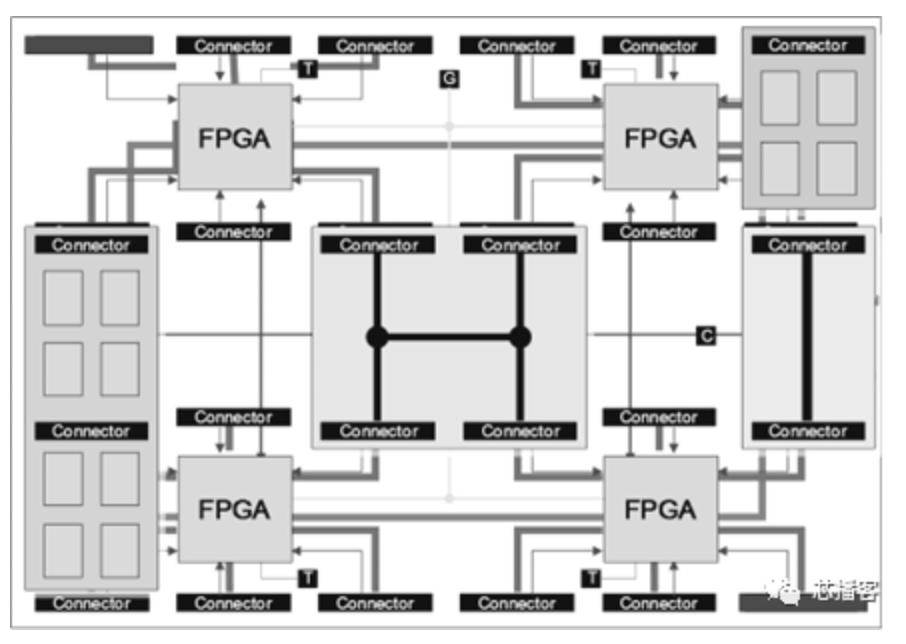

下图是基于HAPS的平台的示意图和照片,显示了使用夹层连接器板和带状电缆进行的本地和远程连接。

连接器的粒度将影响其灵活性,但延迟互连为将FPGA连接在一起以及将FPGA连接到系统的其他部分提供了大量可能性。此外,由于连接不是固定的,因此很容易断开电缆和连接器板,并在下一个原型项目中以新拓扑重新连接FPGA。

间接互连的第二个例子是交换互连,它依靠可编程开关将互连的不同部分连接在一起。当然,可以使用手动开关,但连接密度要低得多,出错的可能性也会增加。假设,我们有一个理想化的中央交换路由矩阵,它可以将任何点连接到电路板上的任何点。该矩阵可编程并配置为满足任何给定设计的分区和路由需求。由于是可编程的,它还可以在项目之间或甚至在项目期间快速更改,以便轻松探索不同的设计选项。对于远程操作,可能是在另一个站点的软件验证实验室,可以将设计图像加载到系统中,并配置交换互连,而无需任何人接触原型本身。

交换互连方法的另一个显著优点是它非常快速且易于更改,因此用户不必认为互连是静态的,而是更动态的。在将设计配置到板上之后,仍然可以将未使用的引脚或其他连接路由到其他点,例如,允许快速探索解决方案或调试方案,或将额外信号路由到测试和调试端口。

交换互连的另一个优点是可以将交换机的编程置于设计划分工具的控制之下。在这种情况下,如果分区器意识到,为了实现最佳分区,它需要某些FPGA之间的更多连接,它可以立即执行该选项,同时使用这些修改的互连资源继续分区任务。在这些场景中,细粒度的交换机结构非常有用,因此可以尽可能少地进行必要的连接来解决分区问题,同时仍然允许其他地方使用其余的本地连接。

如上图所示。这里我们可以看到,除了同一板上的FPGA之间的固定迹线之外,还有可编程开关,可用于通过附加迹线连接FPGA。类似的交换机可以将内存模块链接到平台或链接到其他板或平台,从而构建具有更多FPGA的更大系统。并非所有的交换机组合都是合理的,而且在大多数情况下,由于它们太多,无法手动控制,因此它们由软件自动配置,软件也了解系统拓扑和分区要求。

原文:芯播客

作者: Jacky Yu

相关文章推荐

- ICer必备技能,一文带你了解Python的使用!

- 一份MCU的验证计划,大家看看全不全?

- 浅谈验证平台的通讯机制

- UVM中add_typewide_sequence和add_sequence的区别

- 灵动微课堂 |开源项目:基于MM32F0160微控制器的机械键盘

- 从FPGA说起的深度学习(七)-循环并行化

更多FPGA干货请关注IC设计技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。