FPGA基于B50610实现UDP收发,纯verilog编写,带ping功能,提供工程源码和技术支持

1、前言

目前网上的fpga实现udp基本生态如下:

1:verilog编写的udp收发器,但不带ping功能,这样的代码功能正常也能用,但不带ping功能基本就是废物,在实际项目中不会用这样的代码,试想,多机互联,出现了问题,你的网卡都不带ping功能,连基本的问题排查机制都不具备,这样的代码谁敢用?

2:带ping功能的udp收发器,代码优秀也好用,但基本不开源,不会提供源码给你,这样的代码也有不足,那就是出了问题不知道怎么排查,毕竟你没有源码,无可奈何;

3:使用了Xilinx的三速网IP实现,这样的代码也很优秀,但还是那个问题,没有源码,且三速网IP需要licence,官方提供的licence有效期只有120天,其实三速网IP仅仅实现了rgmii到gmii再到axis的转换,完全可以不用这个ip;

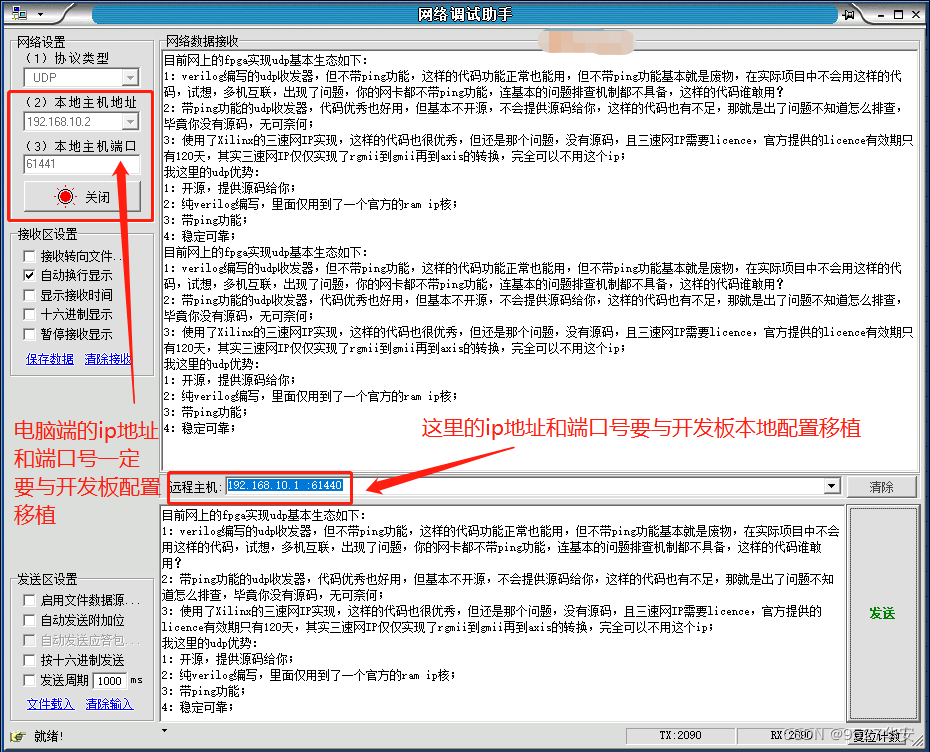

本设计使用B50610作为网络PHY芯片,使用verilog代码设计UDP协议,并带有用户接口,使得用户无需关心复杂的UDP协议而只需关心简单的用户接口时序即可操作UDP收发,用户接口时序在顶层helai_udp_loop.v文件中有阐述,非常简单,通过一个fifo实现UDP数据的回环收发,并在电脑端使用网络调试助手进行UDP收发验证,在文章末尾有演示效果展示。

2、本设计UDP的优势

我这里的udp优势:

1:开源,提供源码给你;

2:纯verilog编写,里面仅用到了一个官方的ram ip核;

3:带ping功能;

4:稳定可靠;

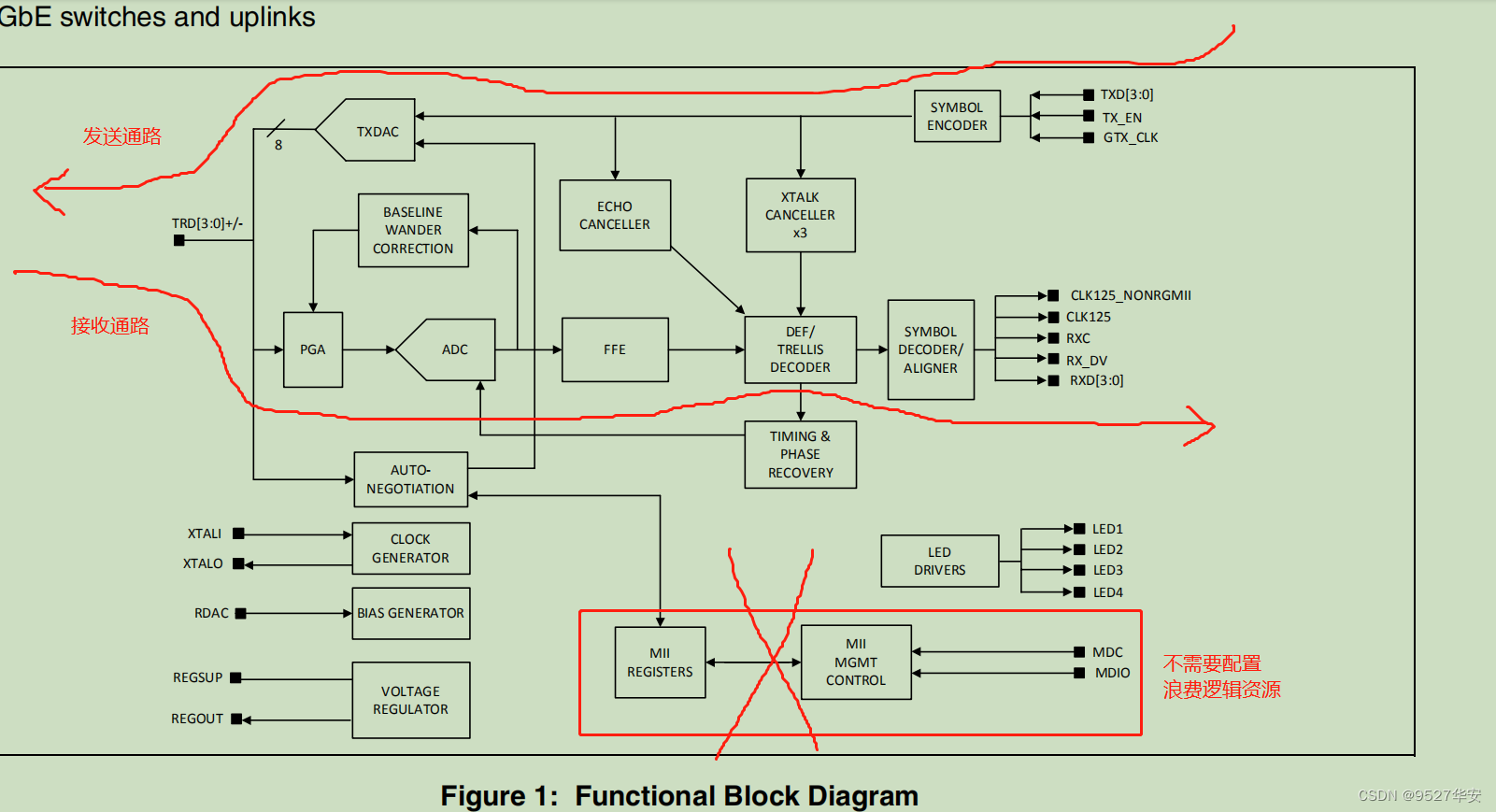

3、B50610芯片解读

说正文,我用到的phy芯片是B50610,想要跑udp,首先必须搞懂B50610,由于我不是画原理图和pcb的工程师,这里仅介绍fpga工程师需要关注的点,直接上数据手册的精华部分:

逻辑框图:对于fpga工程师而言,直到这三点就够了;

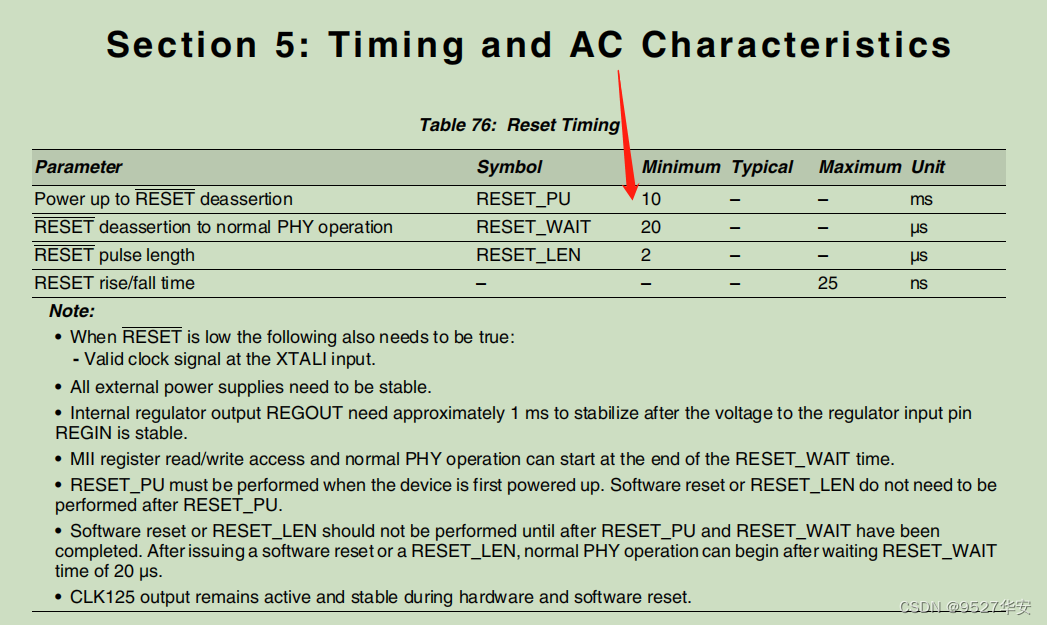

复位:复位时间大于10ms即可;

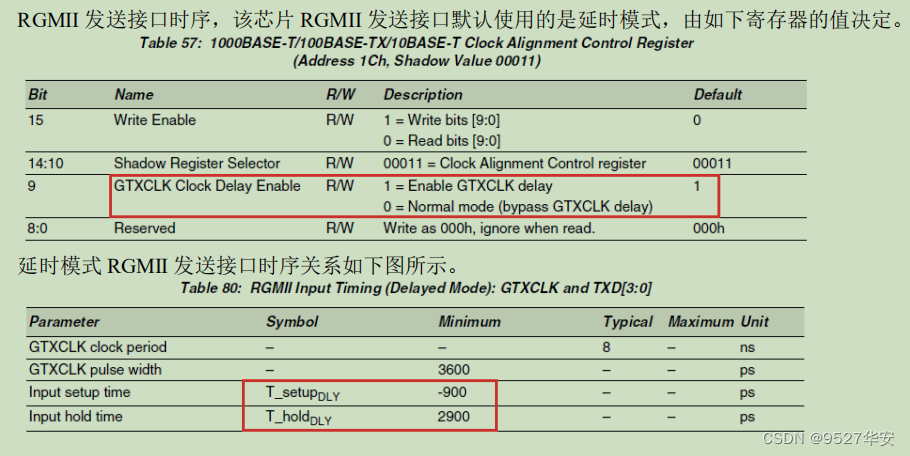

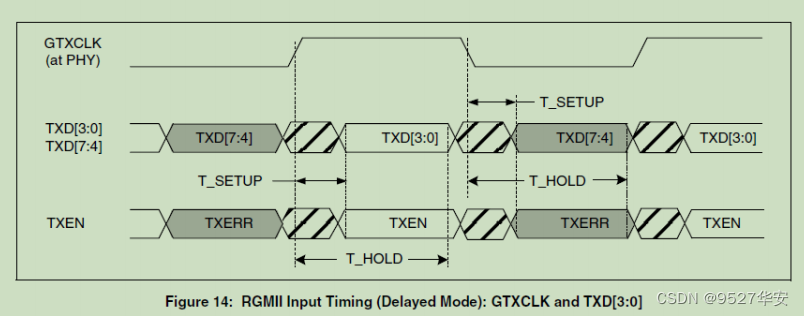

发送时序:发送默认工作在延时模式,不清楚延时模式是什么意思的话可以参考我之前写得文章延时模式

这里的0.9ns和2.9ns的建立和保持时间很重要,后面的时序约束要用;

发送时序:发送默认工作在延时模式,不清楚延时模式是什么意思的话可以参考我之前写得文章延时模式

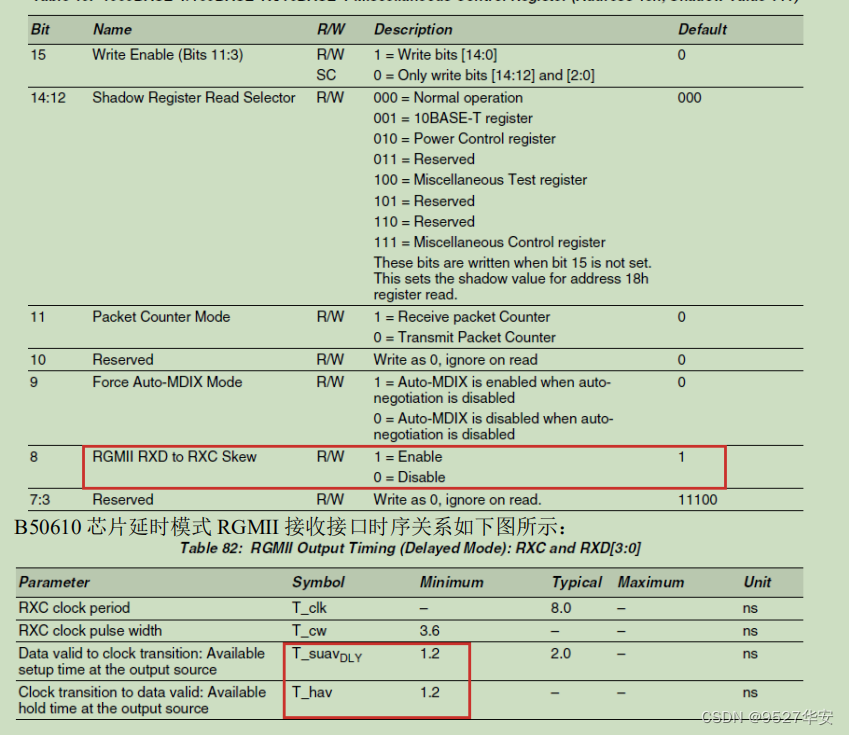

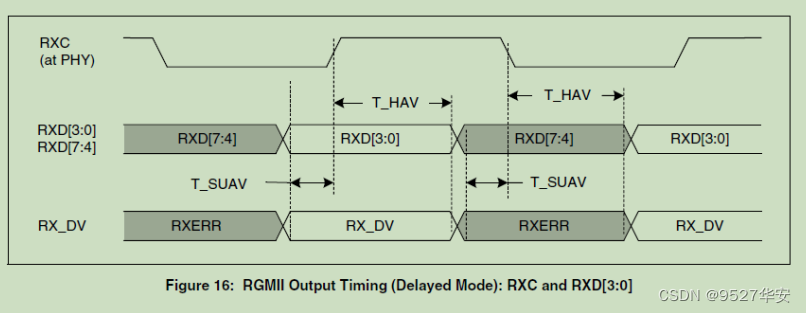

这里的1.2ns和1.2ns的建立和保持时间很重要,后面的时序约束要用;

到此,B50610需要了解的就完了;

4、UDP实现

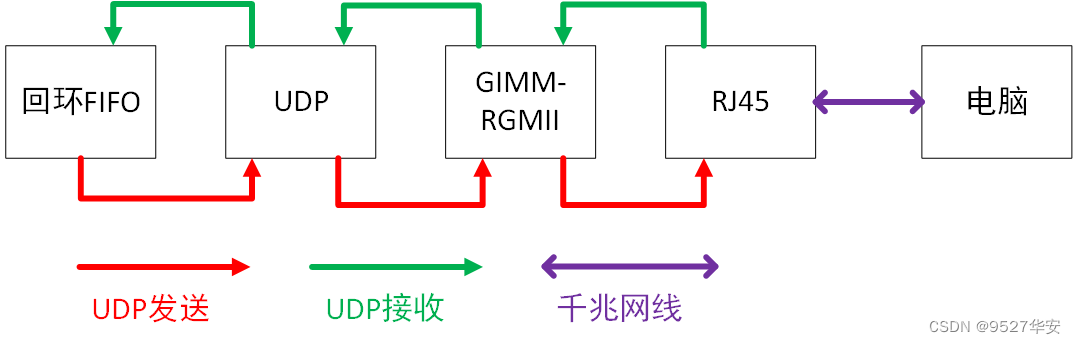

UDP设计思路和框架如下:

框图收发流程很清晰,就不多说了。。。

下面直接介绍工程:

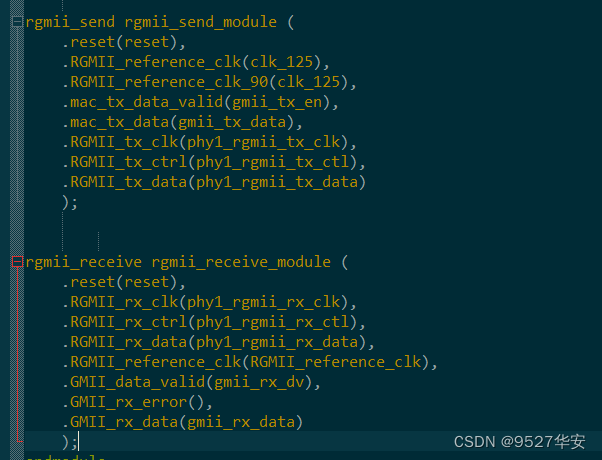

rgmii转gmii,用Xilinx官方源语实现,很简单,可以参考其他博文,其实网上的这块都是抄的Xilinx官方的例程,没什么可说的,

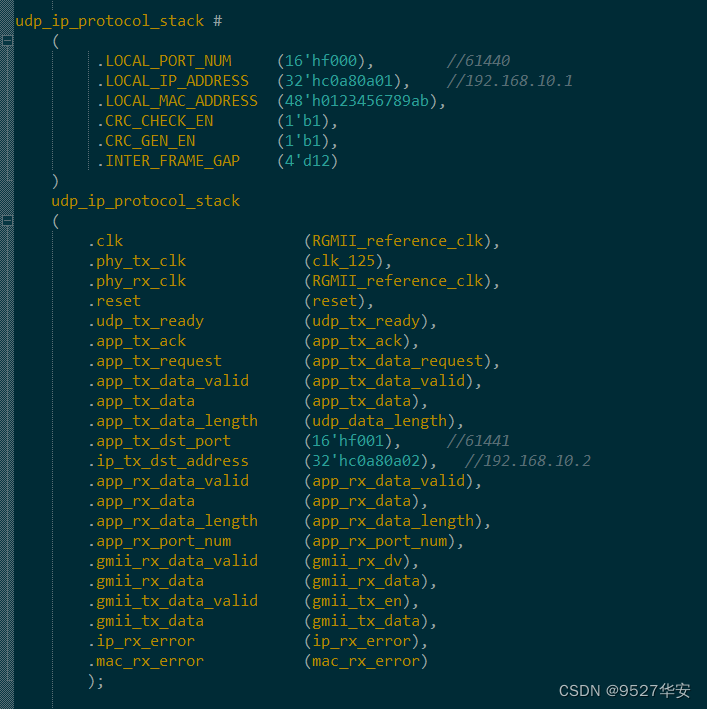

rgmii转gmii后,数据已经是8位的并行数据了,再送udp模块处理进行收发,如下:

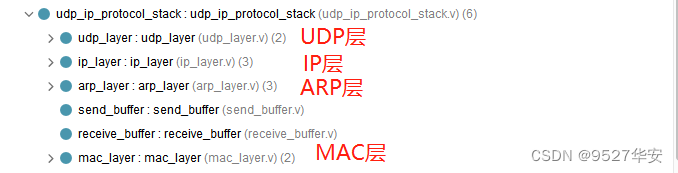

udp模块从上层到下层结构如下:

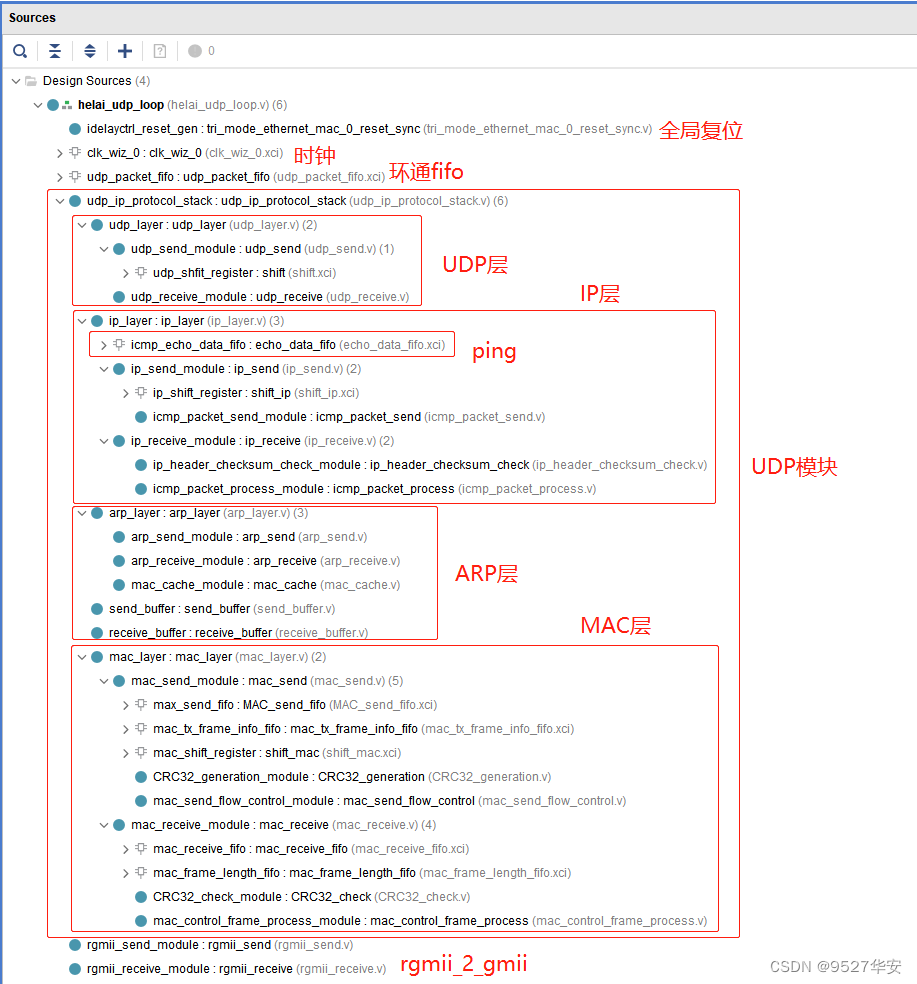

5、vivado工程详解

工程介绍:

开发板:Kintex7开发板;

开发环境:vivado2019.1;

输入输出:UDP环出;

工程代码架构如下:

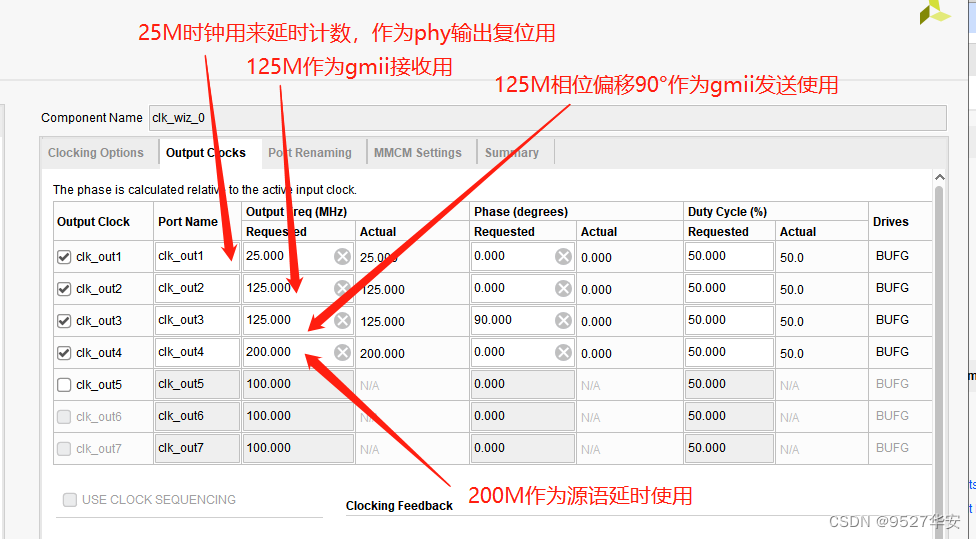

时钟配置如下:

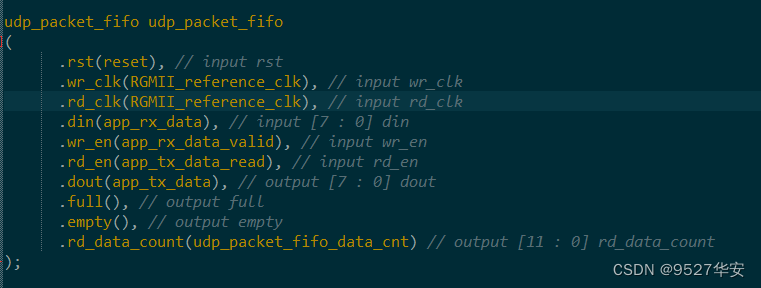

fifo收发:

udp模块用户接口:

关于这部分后面找个时间专门写一篇文章并附上时序图;

6、上板调试验证并演示

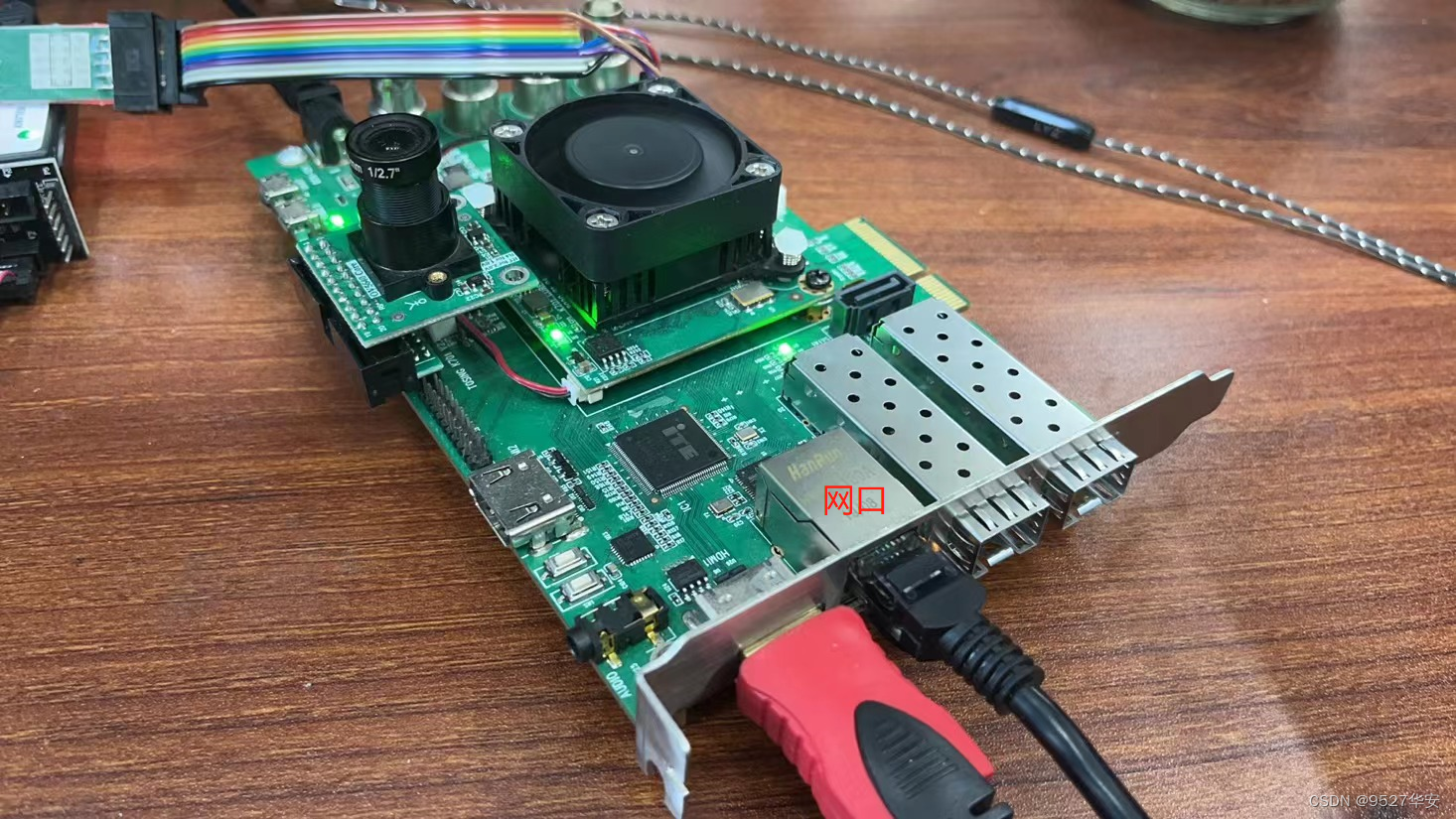

上板验证:

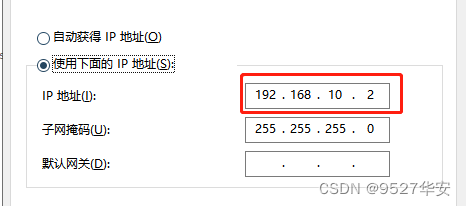

电脑ip设置:

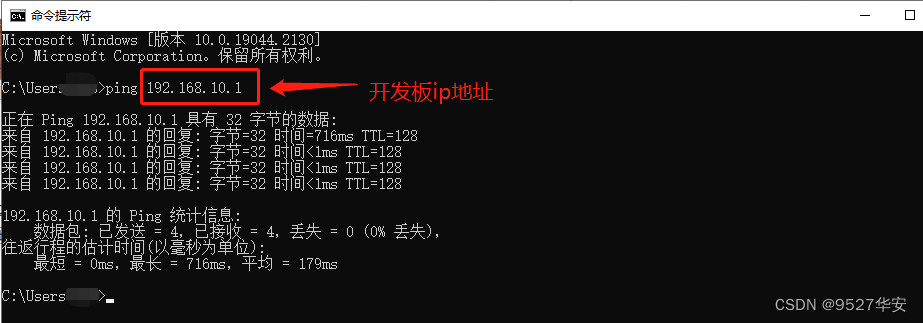

ping功能验证:

UDP环通测试:

可以看到:收发一致,测试成功;

7、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以百度网盘链接方式发送,

通过微信获取资料:

网盘资料如下: