FPGA实现UDP传输视频,提供2套vivado工程源码和接收显示上位机程序

1、前言

FPGA实现UDP传输是FPGA在通信领域的应用之一,只要有UDP收发模块,那么实现UDP传输就只剩下数据组包的事项了;

之前我写过一篇文章介绍过FPGA实现UDP协议的文章FPGA实现UDP协议

后来发现有封装了这个代码的UDP协议栈网表文件,然后添加了Xilinx三速网IP和FIFO的UDP方案,该方案更有利于实现大批量数据传输,整体性能高于之前写的那个FPGA实现UDP协议,但这个方案的UDP协议部分没有源码,但能用,而且还很稳定;关于这部分请看我之前写的文章FPGA实现UDP协议新方案

想要使用这个方案,必须先去Xilinx官网申请三速网IP的licence;关于这部分请参考我之前的文章三速网licence申请

2、设计思路框架

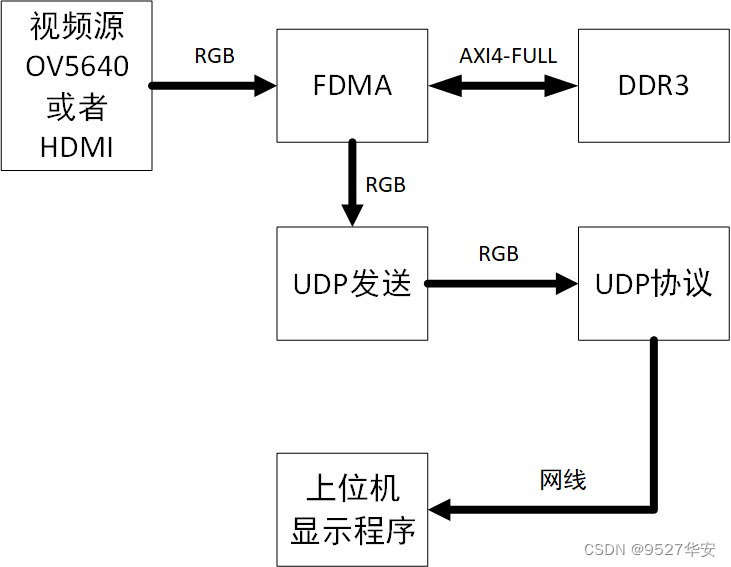

设计框图如下:

视频源

有两个,对应2套工程,1是OV5640摄像头视频,720P,RGB888;

2是HDMI输入视频,720P,RGB888;

图像缓存

实现将采集到的输入视频缓存到DDR3中再读出来,使用米联客的方案,这部分请参考我之前的文章FDMA图像三帧缓存方案

UDP发送

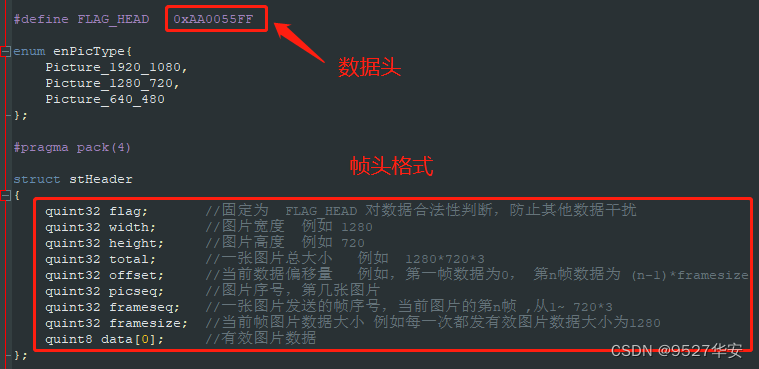

实现UDP数据的组包,UDP数据发送必须与QT上位机的接受程序一致,上位机定义的UDP帧格式包括帧头个UDP数据,帧头定义如下:

另外,由于UDP发送是64位数据位宽,而图像像素数据是24bit位宽,所以必须将UDP数据重新组合,以保证像素数据的对齐,这部分是整个工程的难点,也是所有FPGA做UDP数据传输的难点;

UDP协议

这部分就是前面说的FPGA实现UDP协议新方案这里注意一下,我板子的phy芯片是B50610,关于这个芯片FPGA需要掌握的常识请看这篇文章B50610解读

提供的2套工程说明

网盘资料内容如下:

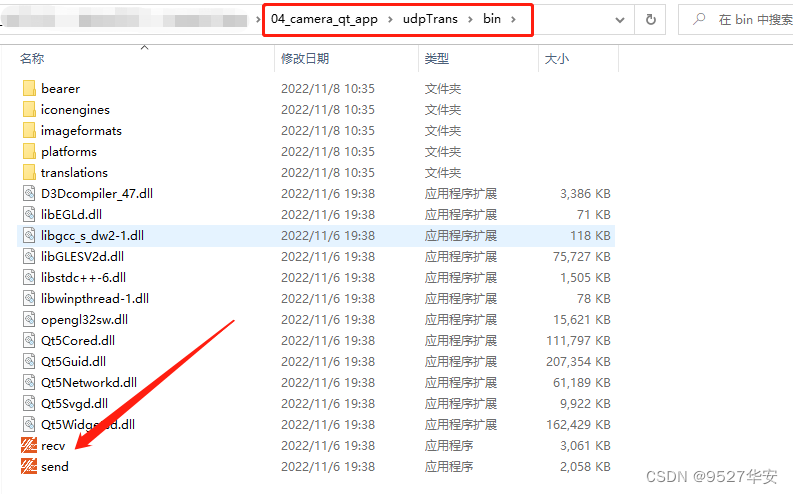

上位机运行程序只适用于Windows版本,目录在、如下:

3、vivado工程1详解

工程1:

开发板:Kintex7开发板;

开发环境:vivado2019.1;

输入:OV5640摄像头,720P,RGB888;

输出:RJ45网口;

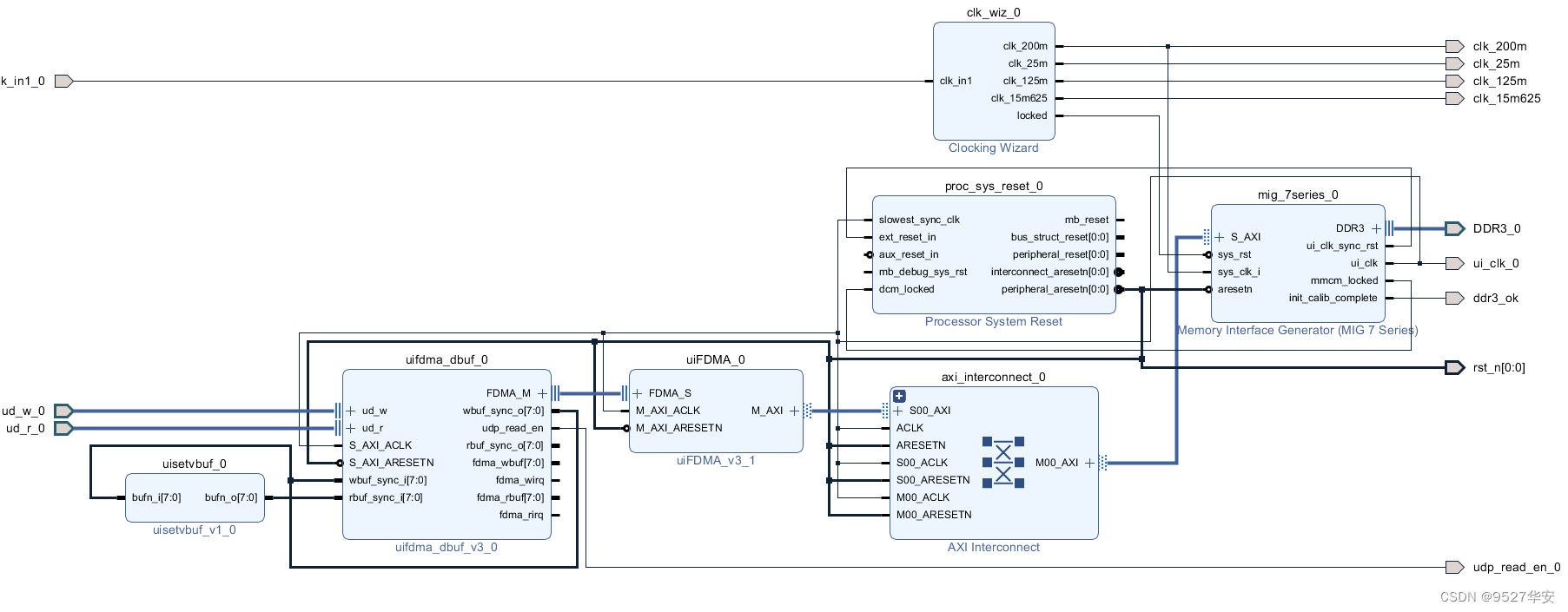

工程BD部分如下:

这里的FDMA控制器要做修改,我已经修改并重新封装,感兴趣的可以去看源码,这里多了个输出信号udp_read_en,作用是等待fifo缓存足够数据时才发起UDP传输;另外,输出数据位宽也变为了128位;

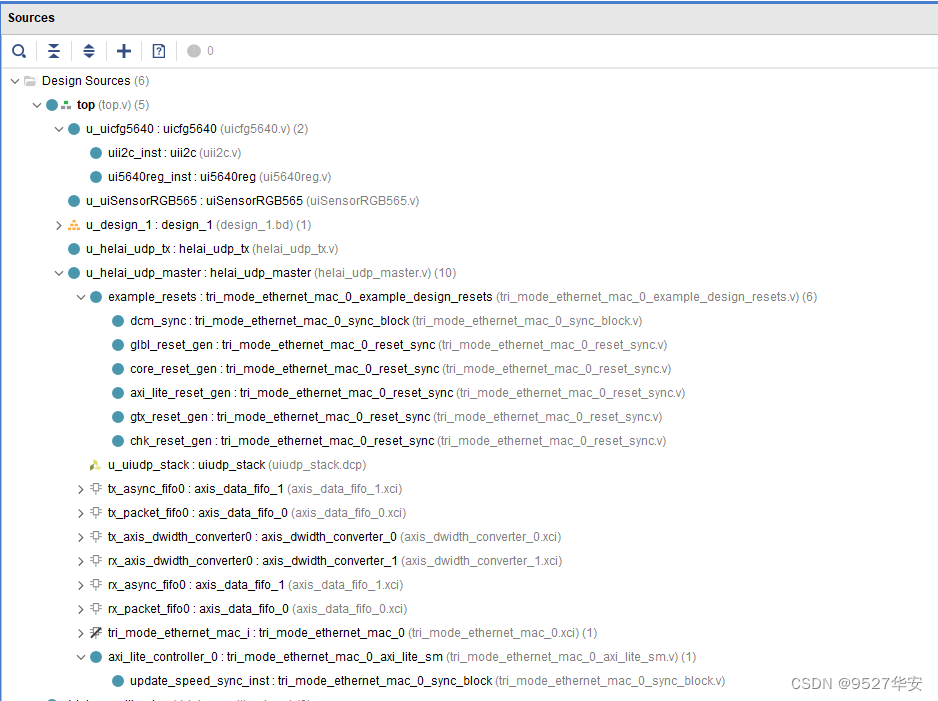

代码架构如下:

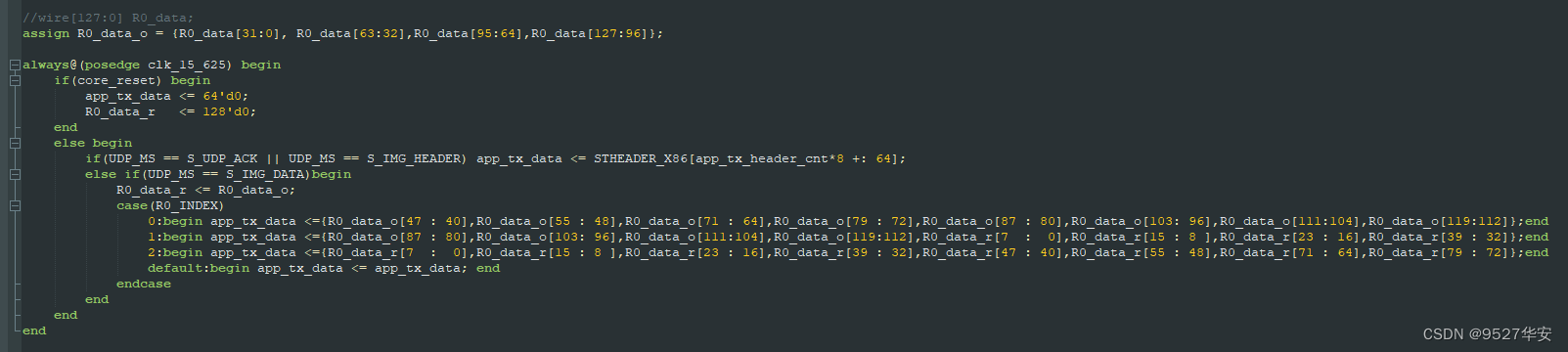

关键代码部分如下:

这部分代码实现了RGB888数据的紧密排列,拿到代码后要好好理解,不然看不懂这个工程;

4、vivado工程2详解

工程2:

开发板:Kintex7开发板;

开发环境:vivado2019.1;

输入:HDMI输入720P,IT6802解码,RGB888;

输出:RJ45网口;

工程BD部分与工程1相同;

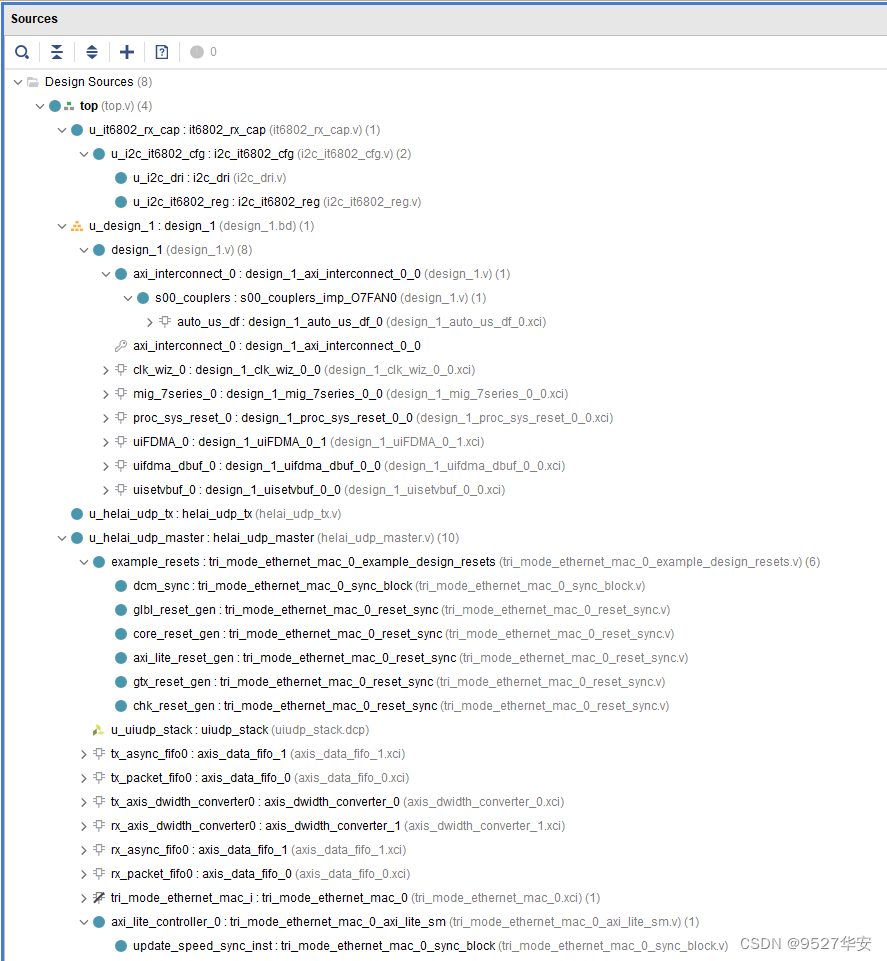

代码架构如下:

5、上板调试验证

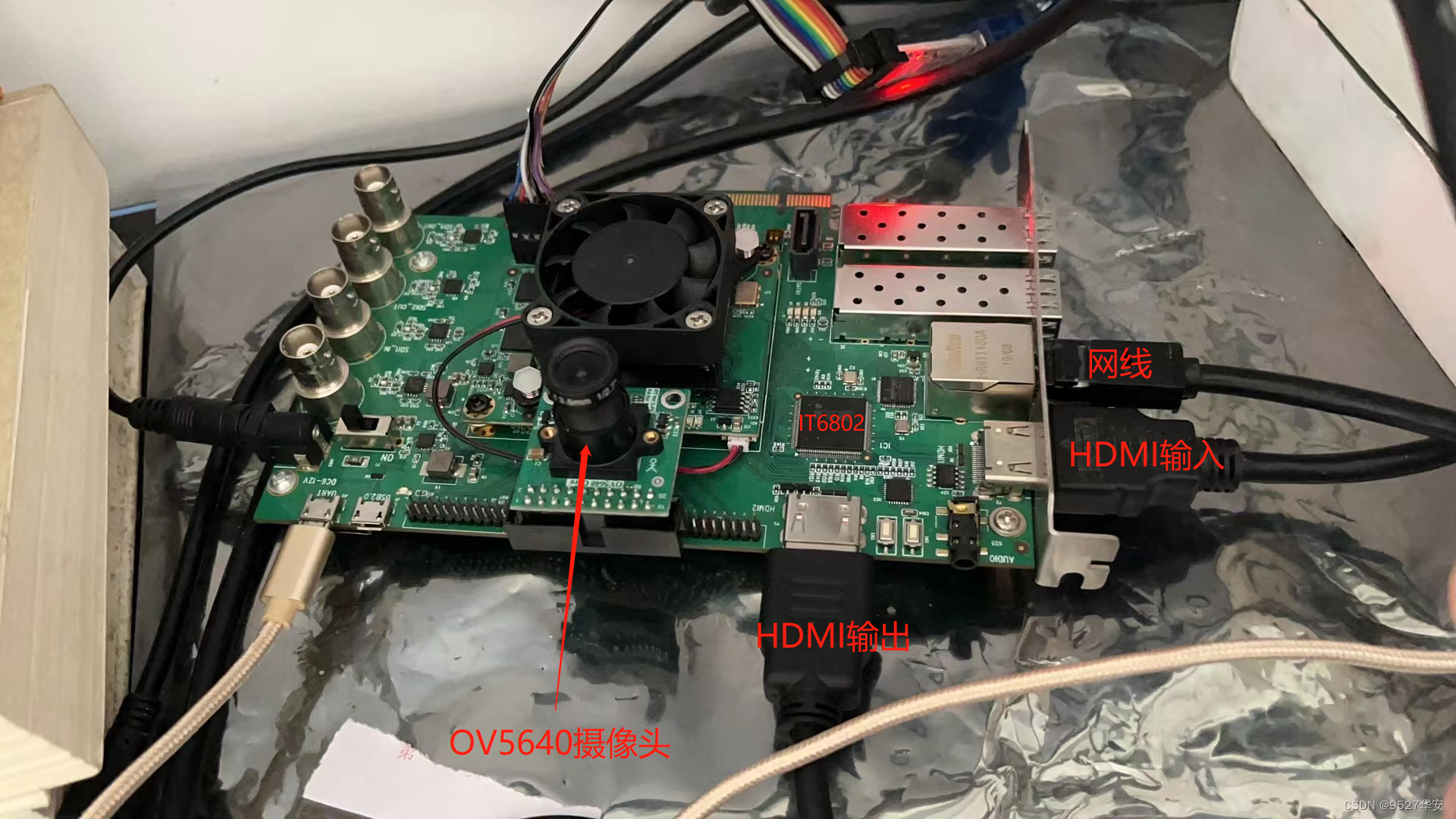

上板连接:

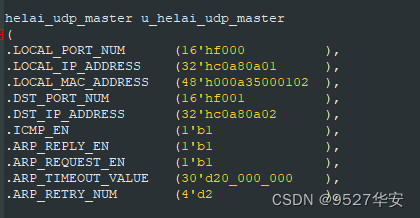

开发板IP地址如下:可根据需求自由修改

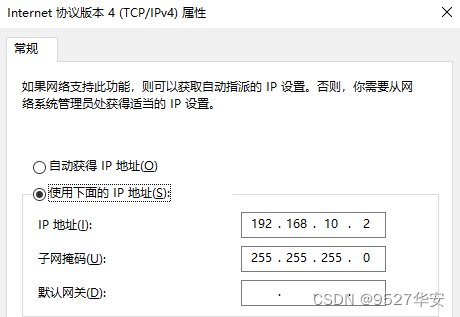

电脑端IP修改如下:

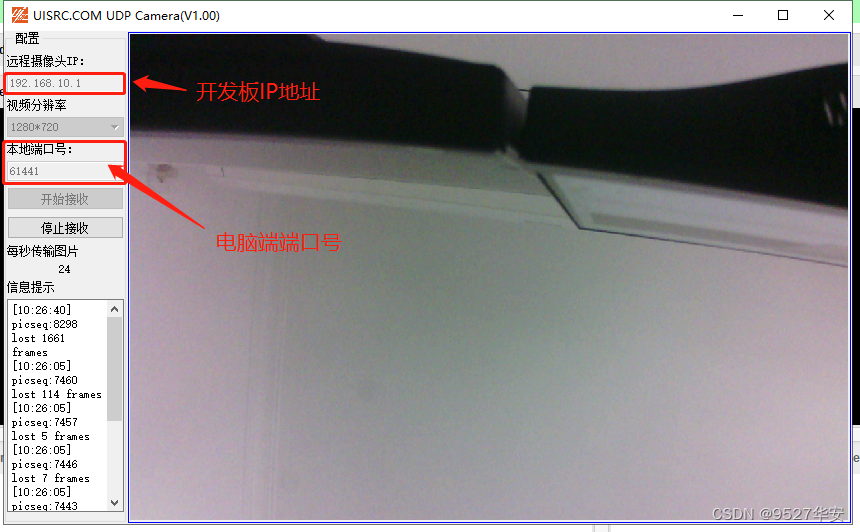

上位机设置如下:

显示效果如下:只演示了ov5640的效果,HDMI的自己去输出看看吧兄弟

点击直接查看输出演示视频

6、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以百度网盘链接方式发送,

通过微信获取资料:

网盘资料如下: