2023年7月20日,第十七届中国半导体行业协会半导体分立器件年会暨2023年中国半导体器件技术创新及产业发展论坛在杭州开幕,华大九天高级产品总监刘晓明受邀出席,并发表题为《EDA助力分立器件设计-制造协同发展》的技术演讲。

(华大九天高级产品总监刘晓明)

分立器件是半导体市场的重要组成部分,包括功率,信号处理,光电传感等不同器件类型,在通讯,汽车,计算机,物联网等领域都有广泛应用。分立器件厂商会从材料,结构及工艺等环节优化制造工艺,满足多样化的市场需求。但这些优化的目标,可归纳为更高的性能,更高的可靠性,更高的良率。EDA作为设计和制造的桥梁,将助力分立器件市场设计与制造的协同发展。

刘晓明在分享中指出,从设计的角度看,分立器件面临诸多挑战。不同材料及结构的器件,需要多样化的模型支持,例如第三代半导体材料的高频器件,需要更多的模型创新;分立器件版图的圆弧等复杂图形设计,也是传统 EDA工具难以绘制的,这也给EDA版图工具提出了新的要求;当器件设计出来后,功能满足要求还不够,尤其是车规和工控应用领域,还有需要产品有更高的可靠性,这需要工具能够精确及高效率的分析;当完成分立器件设计,交付数据到晶圆制造时,如何在一个晶圆上,通过合理的排版产生更多的器件,直接影响器件的单位批次的产量,这也是设计者关心的问题。

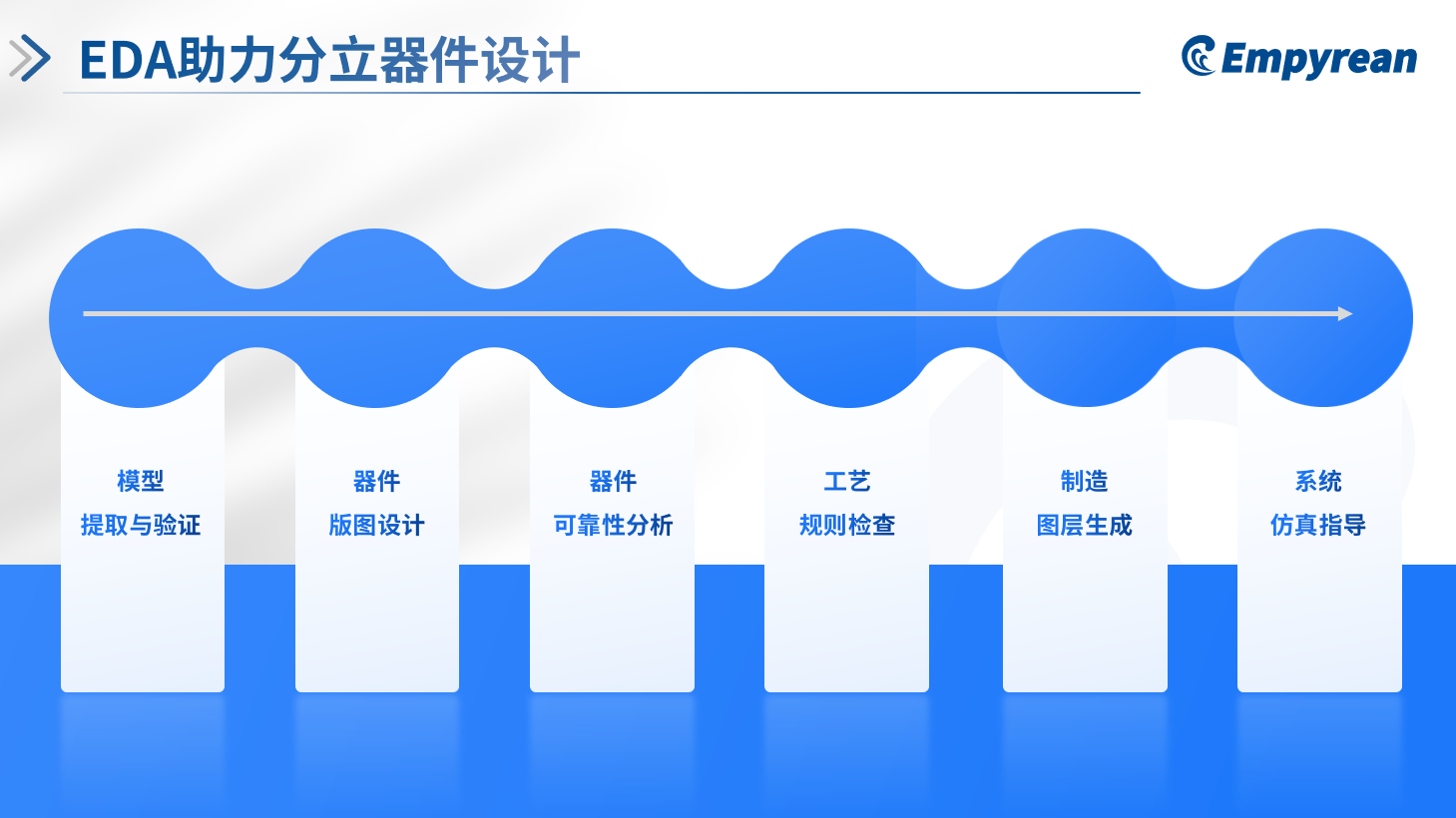

针对以上问题,华大九天从最初的器件设计到最后的量产提供了对应的解决方案。器件模型提取方面,可通过参数化的test pattern设计,测试及建模,高效完成电学模型提取;器件可靠性方面,可通过量化分析的手段直观地体现器件可靠性问题;在制造环节,通过专业化的设计规则检查,保证图纸能够正确交付;在制造的掩膜板交付环节,通过图层计算与最优化排版提高生成效率及单位批次器件产量;最后,系统层面,可利用华大九天在模拟及射频领域系统的仿真,实现器件与系统的协同仿真,并从系统的视角来去评判和指导分立器件设计及优化。

华大九天EDA工具在分立器件领域已经做出诸多应用和尝试:

首先,在器件模型提取领域,华大九天可提供一套完整的与模拟及射频芯片相兼容的器件模型的提取与验证的流程。在这个流程中,可同时支持CMOS, BCD及各种第三代半导体材料器件的提取。在器件可靠性方面,工具可基于老化及宽温等测试数据,实现模型的扩展,并结合各类器件模型,高效地完成数据拟合与优化。从应用角度看,器件最终是要工作在不同的环境中,以车规芯片为例,其需要支持——55度及125度的环境。例如在中国黑龙江“中国寒极”的极低温度下,器件是什么样的特性,需要我们从器件的角度来先做量化分析。总之,这套工具可结合不同材料,器件结构,宽温,高压,老化等数据,完成全面的模型提取与验证。

为了帮助器件设计者高效地获取精确的电学模型,华大九天基于参数化单元技术,还可提供自动化的test pattern生成方案,并结合设计服务业务,为设计者提供一站式模型提取与验证解决方案。

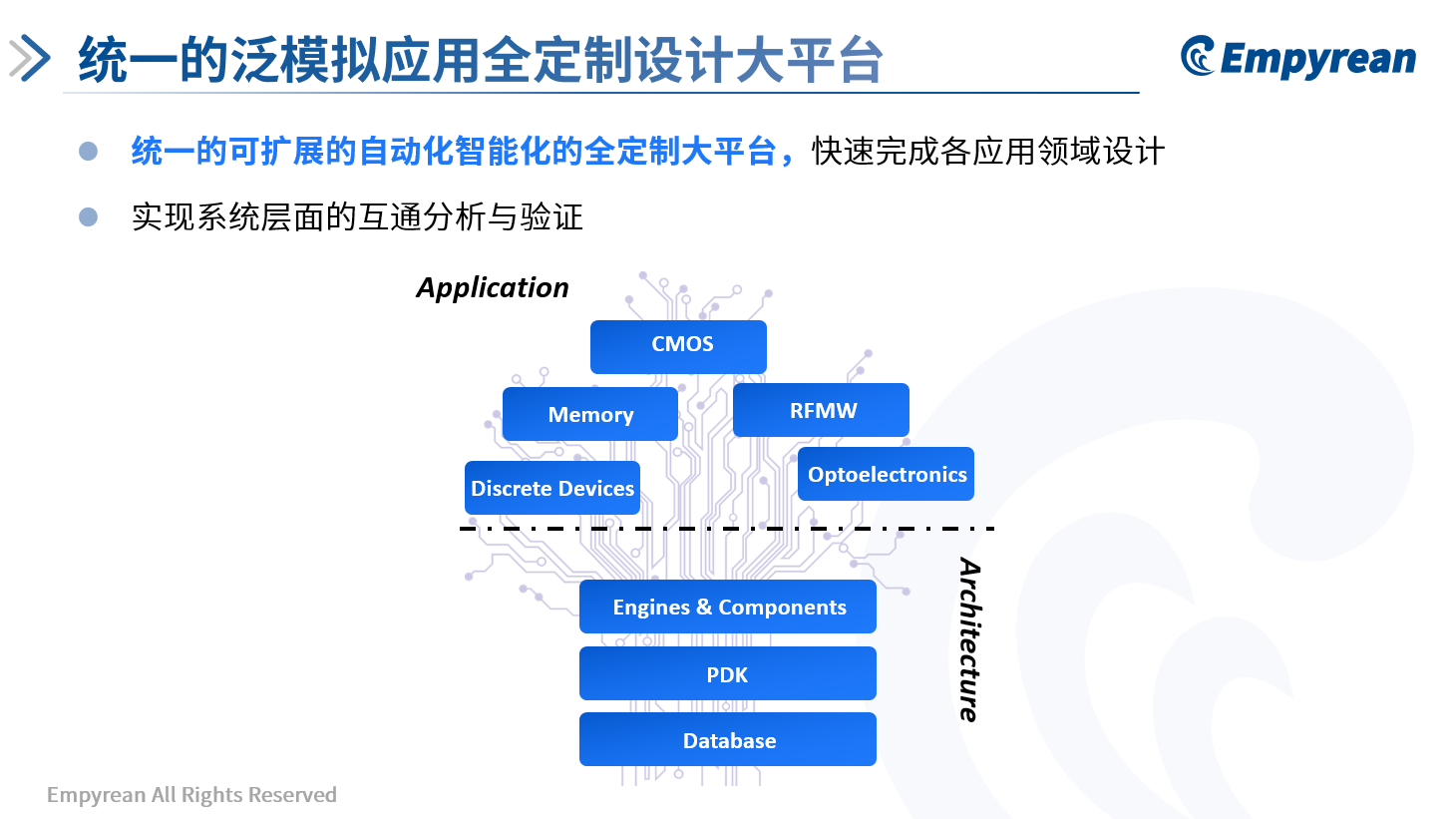

分立器件最终需要与其它器件构成电路系统,为了适应未来的系统设计,华大九天基于融合的思想,提出了构建统一的“泛模拟应用全定制大平台”概念。在这个大平台上,工具基于统一且开放的数据库,针对模拟、射频、分立器件、存储、光电等不同领域的工艺要求,提供统一且兼容的PDK,并针对不同领域的设计特点,开发对应的功能及模块。因为,这些应用的底层数据是相通的,所以工具可以把分立器件和与其匹配的模拟电路,射频电路等做综合分析,并从系统的角度来做一个分立器件性能的评判。

在上述全定制设计大平台上,版图工具可支持各种复杂的版图规则功能,也可通过复杂的数学函数完成曲线及圆弧的绘制。在具体的操作方法层面,也有很大好用的小功能。比如,高压器件需要有保护环,而保护环不能是矩形,应该设计成圆角,华大九天的版图工具可自动完成矩形保护环到圆角保护环的转换。此外,版图工具还可利用图层逻辑运算批量化产生图形。光电器件为了传输光信号,需要利用圆弧的光波导做器件结构设计,版图工具可引用Python函数,完成精细的圆弧类器件设计。

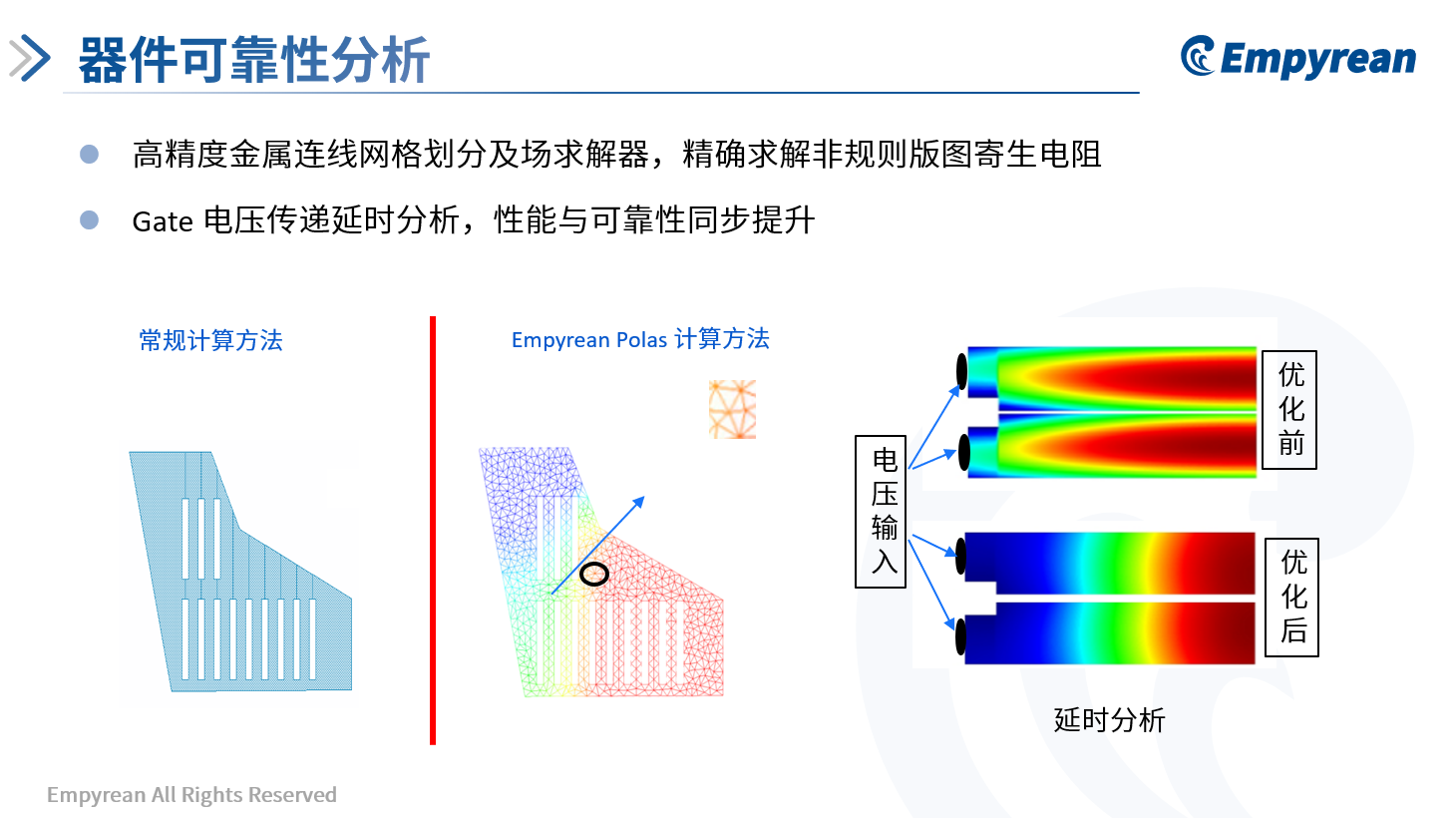

在可靠性分析方面,华大九天可对功率型分立器件的电源走线做精准的量化分析。不同于传统的利用矩形网格及方块电阻计算金属线网的方法,华大九天的Empyrean Polas®利用高精度自适应网格剖分技术,精确还原电源网络电阻分布,然后基于电源网络做量化的可靠性分析。例如,当信号从pad传递到多个并联的器件时候,工具可以计算各个器件导通的延时分布。 对于垂直结构的器件,工具可结合晶圆制造工艺上的每一个图层及其立体结构做这种精确的电阻提取,如果分立器件通过金属引线连接PCB,工具也可计算引线的电阻。利用精准的电源网络及器件内部图层通路电阻,工具可对分立器件做完整的导通电阻计算,并通过电压降及电流密度分析,指导器件版图的设计与优化。

版图设计及分析后,还需要进行设计规则检查。在传统的CMOS芯片设计领域,各家Foundry会提供标准的设计规则,但在分立器件领域,器件厂商会根据不同的市场需要来定制工艺,设计规则也会挑战,这也给设计者带来了难题。华大九天的工具可提供界面化的设计规则平台,帮助设计者条理清晰的书写设计规则。完成设计规则书写后,工具可自动生成测试图形验证设计规则的正确性。在版图验证环节,工具通过引擎上的算法优化,可实现圆弧图形的高效检查,降低伪错数量。在报告查看是,工具可将错误结果生成网页格式的报告,便于多个团队间的数据传递和交流。在版图改版时,工具可通过双窗口实现版本间差异的直观比较。

当设计版图交付生产时,需要做生成制造的掩膜板。华大九天的工具可利用图形计算技术,逐层产生掩膜版图层数据。当器件在原型的晶圆上排版时,设计者会面临如何排版的问题,器件阵列向各个方向移动一点,都会有新的器件进入或超出边界,这是一个最优化排版问题。EDA工具,可以通过最优化算法计算,完成最优排版,在一次生产过程中,产生更多的分立器件。

在泛模拟芯片设计领域,华大九天可提供SPICE模拟电路仿真器,也可提供射频电路的仿真器。利用全定制大平台以及仿真器,工具可将分立器件,模拟电路、射频电路,以及光电电路在一个统一的系统做仿真分析,并从系统指标层面上,实现对分立器件设计的指导。

目前,分立器件行业更多地沿用CMOS电路设计EDA工具。随着市场需求的多样化,其设计方法也需要进一步创新。CMOS电路设计在从自动化走向智能化,分立器件设计领域,也可利用AI技术做进一步探索,比如模型提取,版图自动生成,可靠性分析等。华大九天也会做更多尝试,助力分立器件设计与制造协同发展。