思考:

- 页表最大支持几级页表查询?

- 虚拟地址的有效位一般是多少?最大是多少?

- 虚拟地址的高16bit的用途?

- 查询到的页面的大小,可以是多大?

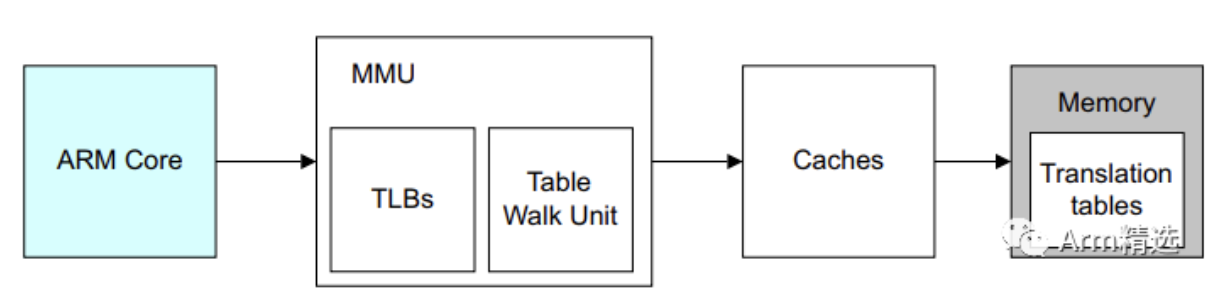

Memory Management Unit (MMU)的主要功能就是能够让系统在执行多任务时,作为一个独立的程序运行它自己的虚拟地址空间中,它们无需知道真正的物理地址是什么。开启MMU的硬件框图如下所示:

Virtual and physical memory的映射图如下所示:

一、Translation Lookaside Buffer (TLB)

1.1 TLB entry里有什么?

TLB中不仅仅包含物理地址和虚拟地址,它还包含一些属性,例如:memory type、cache policies、access permissions、ASID、VMID

注:ASID - Address Space ID, VMID - Virtual Machine ID

1.2 contiguous block entries

TLB拥有固定数目的entries,所以你可以通过减少外部内存地址转换的次数来提升TLB hit率.

在ARMV8 architecture中有一个TLB中的feature叫contiguous block entries,它表示一个entry可以对应多个blocks.。一个entry找到多个blocks,再通过index来查找具体是哪个block。页表的block entries中,也有一个contiguous bit。这个bit为1,则表示开启了TLB的contiguous block entries feature。contiguous block entries feature要求alignment,例如:

- 16 × 4KB adjacent blocks giving a 64KB entry with 4KB granule. 缓存64kb blocks,只需16 enties

- 32 × 32MB adjacent blocks giving a 1GB entry for L2 descriptors, 128 × 16KB giving a 2MB entry for L3 descriptors when using a 16KB granule.

- 32 × 64Kb adjacent blocks giving a 2MB entry with a 64KB granule.

如果支持了contiguous bit,那么:TLB查询后的PA = TLB entry中的PA + index。

1.3 TLB abort

如果开启了contiguous bit,而要转换的table entries却不是连续的,或者entries的output在地址范围之外或没有对齐,那么将会产生TLB abort。

1.4 TLB一致性

如果os修改了页表(entries),那么os需要告诉TLB,invalid这些TLB entries,这是需要软件来做的. 指令如下:

TLBI <type><level>{IS} {, <Xt>}二、Translation table

2.1 TTBR0/TTBR1

ARM文档说:因为应用程序切换时要切换页表,页表经常改变,而kernel切换时不需要切换页表,页表几乎不改。所以ARM就提供了 a number of features,也就是TTBR0和TTBR1两个页表基地址。

TTBR0用于0x00000000_00000000 - 0x0000FFFF_FFFFFFFF虚拟地址空间的翻译,TTBR1用于0xFFFF0000_00000000 - 0xFFFFFFFF_FFFFFFFF虚拟地址空间的翻译。

EL2/EL3只有TTBR0,没有TTBR1,所以EL2/EL3的虚拟地址空间是:0x0000FFFF_FFFFFFFF

2.2 页表的entry中包含哪些信息

MMU除了完成地址的翻译,还控制访问权限、memory ordering、cache policies。

如图所示,列出了三种类型的entry信息:

bits[1:0]表示该输出是block address,还是next level table address,还是invalid entry

2.3 granule sizes

有三种granule sizes的页表:4kb、16kb、64kb

2.4 Cache configuration

MMU使用translation tables 和 translation registers控制着cache policy、memory attributes、access permissions、va到pa的转换

三、 ARM mmu三级页表查询的过程

- (1)、在开启MMU后,cpu发起的读写地址是一个64bit的虚拟地址,

- (2)、该虚拟地址的高16bit要么是全0,要么是全1. 如果是全0,则选择TTBR0ELx作为L1页表的基地址; 如果是全1,则选择TTBR1ELx作为L1页表的基地址;

- (3)、TTBRx_ELn作为L1页表,它指向L2页表,在根据bit[41:29]的index,查询到L3页表的基地址

- (4)(5)、有了L3页表的基地址之后,在根据bit[28:16]的index,查询到页面的地址

- (6)、最后再根据bit[15:0]查找到最终的物理地址

作者:lvy

文章来源:Arm精选

推荐阅读

欢迎关注ARM精选专栏, 欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。