1、同步复位寄存器

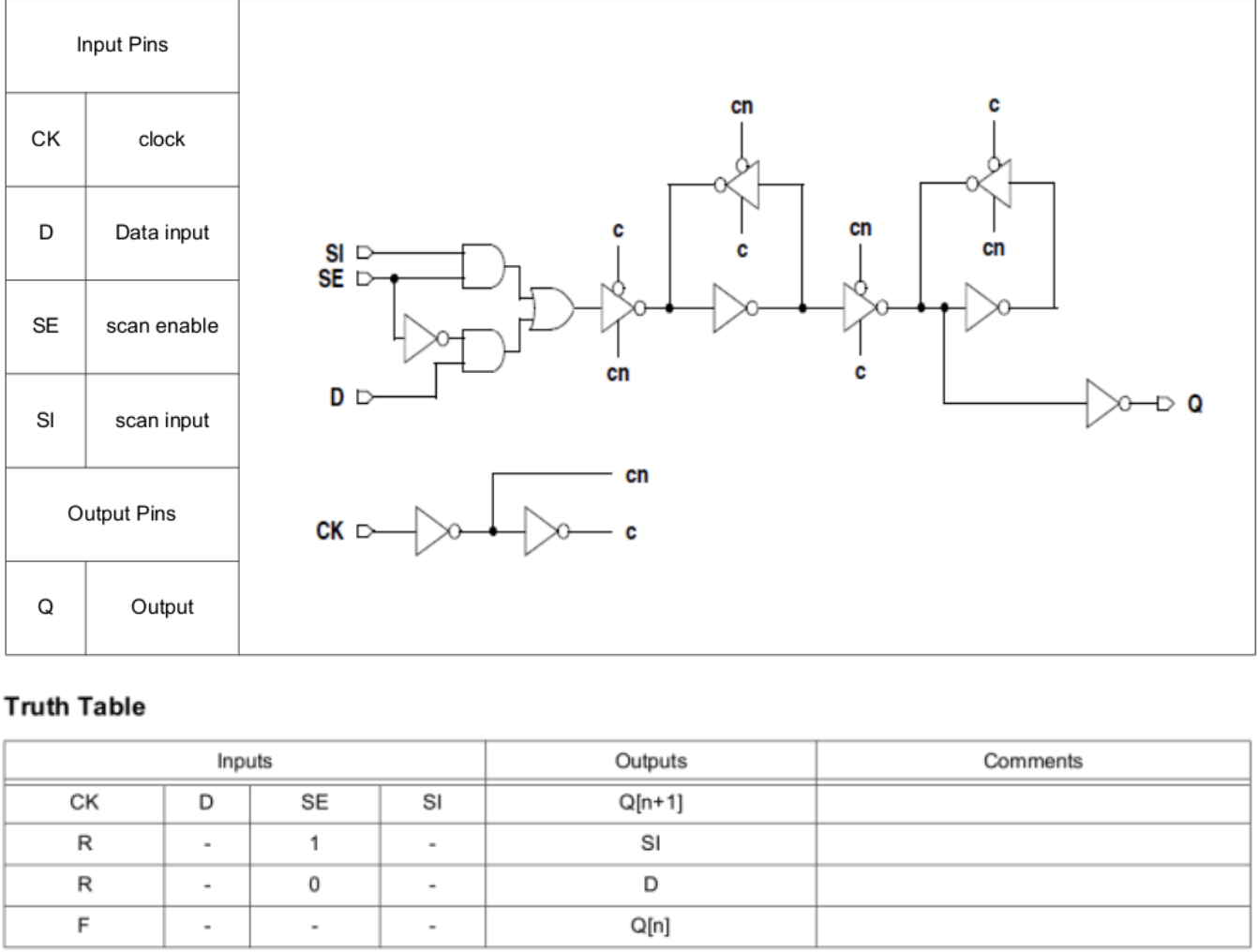

下图所示为上升沿触发的无复位静态D触发器,拥有扫描输入input接口SI和扫描使能SE,D端口是输入数据口,Q是数据输出口。忽略扫描链信号SI和SE,在时钟没有来临的时候,D触发器保持为稳定值,当clock上升沿来临时,图中门电路被打通,输出端Q由D驱动,时钟沿结束后,Q端保持稳定。

下图所示代码为同步复位寄存器,在完成DC综合映射后对应的寄存器就是无复位静态D触发器,而不是带复位的端口的D触发器。

always @(posedge clk) 2. 异步置位寄存器

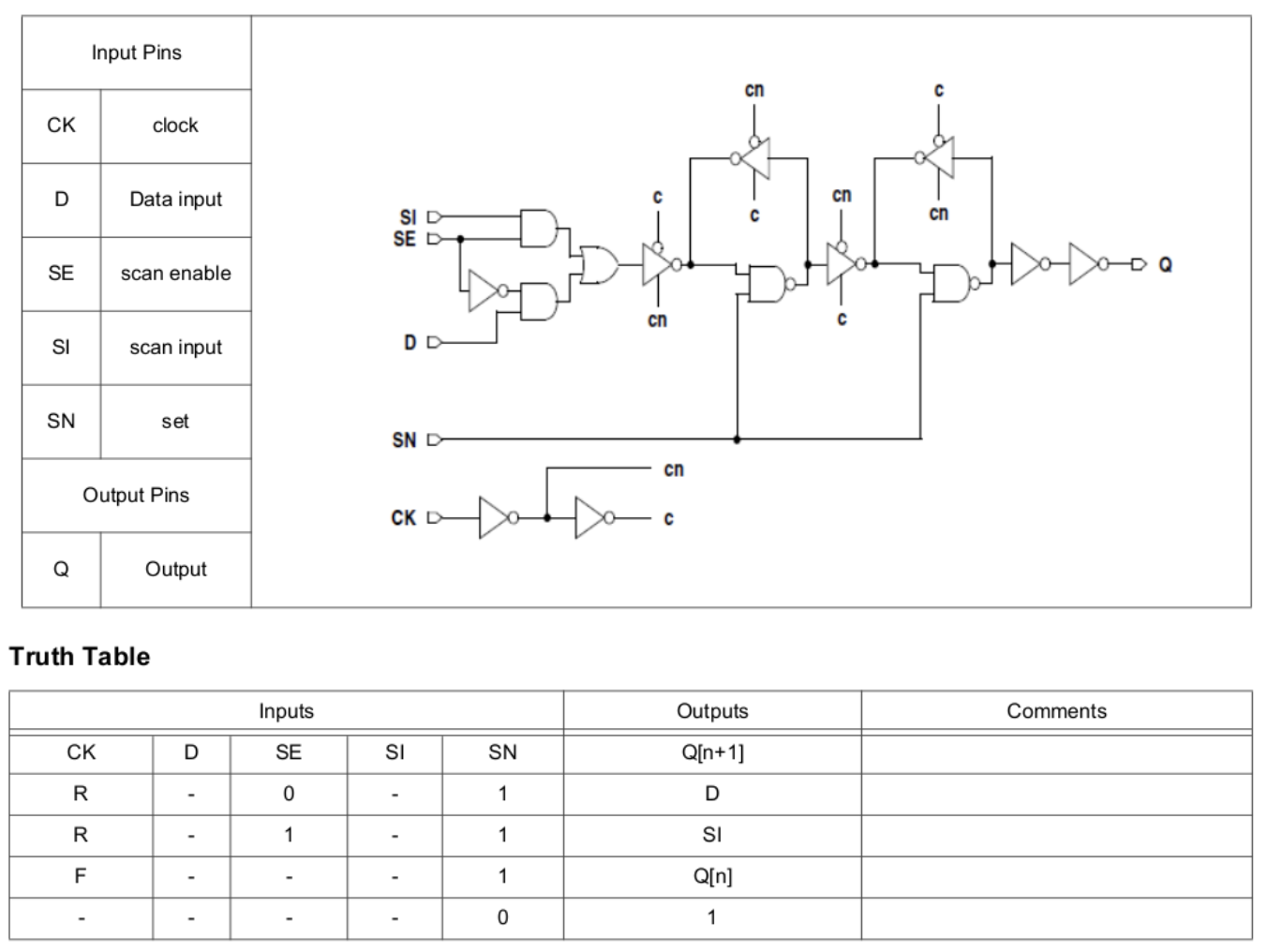

下图所示为上升沿触发的置位静态D触发器,拥有扫描输入input接口SI和扫描使能SE,D端口是输入数据口,Q是数据输出口。忽略扫描链信号SI和SE,在时钟没有来临的时候,D触发器保持为稳定值,当clock上升沿来临时,图中门电路被打通,输出端Q由D驱动,时钟沿结束后,Q端保持稳定。复位信号SN为0时,Q端为1

下图所示代码为异步复位寄存器,因为复位值为1,所以在完成DC综合映射后对应的寄存器就是置位静态D触发器。

always @(posedge clk or negedge rstn)3. 异步复位寄存器

下图所示为上升沿触发的复位静态D触发器,拥有扫描输入input接口SI和扫描使能SE,D端口是输入数据口,Q是数据输出口。忽略扫描链信号SI和SE,在时钟没有来临的时候,D触发器保持为稳定值,当clock上升沿来临时,图中门电路被打通,输出端Q由D驱动,时钟沿结束后,Q端保持稳定。复位信号R为1时,Q端为0.

下图所示代码为异步复位寄存器,因为复位值为0,所以在完成DC综合映射后对应的寄存器就是置位静态D触发器。

always @(posedge clk or negedge rstn)4、要点总结:

Verilog代码中的同步复位寄存器综合映射结果对应的标准cell为不带复位端口的触发器,只有异步复位寄存器才会被综合映射成复位端口的触发器。

同类型(同为高速、低速、normal)的无复位D触发器和有复位/置位寄存器相比来,无复位D触发器的面积约小20%左右(14nm~5nm标准cell手册有提供详细数据,本文未给出),根据工艺不同有所差异。

作者:IC小鸽

文章来源:IC的世界

推荐阅读

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。