Perface

之前我们讲述了关于五个维度安全威胁概要,从现在开始就这几个方面详细的展开讲讲。

第一个系列:硬件安全-CPU

硬件

1、TrustZone

ARM TrustZone技术是芯片级的安全解决方案,通过在CPU内核的设计中集成系统安全性扩展,同时提供安全软件平台,为安全支付、数字版权管理(DRM, Digital Rights Management)、企业服务等应用提供了安全的运行环境。

TrustZone将硬件和软件资源划分为两个执行环境:安全世界(Secure World)和普通世界(Normal World)。不同执行环境的系统软件和应用软件、内存区和外围设备等均相互独立。TrustZone的硬件逻辑,使安全世界的资源与普通世界隔离,不能被普通世界的组件访问。

把敏感资源放在安全世界,能保护绝大多数的资源免受很多潜在的攻击,包括一些很难保证安全的操作,如用键盘或者触摸屏输入密码。

普通世界和安全世界的代码以分时共享的方式在同一个物理处理器核上运行,使其不需要专用的处理器内核来执行安全代码,节省了芯片面积和能耗。

1.1 TrustZone硬件架构

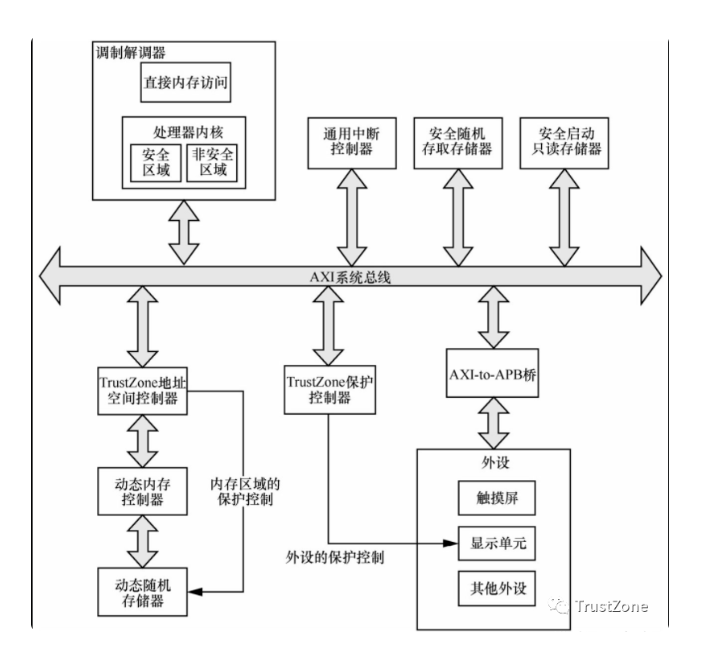

TrustZone的硬件架构如下图所示,

•其核心包括处理器内核、

•直接内存访问(DMA,Direct Memory Access)、

•安全RAM、

•安全启动ROM、

•通用中断控制(GIC,Generic Interrupt Controller)、

•TrustZone地址空间控制器(TZASC,Trust Zone Address Space Controller)、

•TrustZone保护控制器、

•动态内存控制器(DMC,Dynamic Memory Controller)

•DRAM(Dynamic Random Access Memory,动态内存控制器),•TrustZone内部组件通过AXI(Advanced eXtensible Interface,先进的可扩展接口)系统总线通信,与外设通过AXI-to-APB桥通信。

(1)系统安全性

TrustZone隔离了所有SoC(System on Chip,系统级芯片)硬件和软件资源,划分为两个执行环境,即用于安全子系统的安全区域以及用于存储其他所有内容的普通区域。

TrustZone通过AXI和APB实现了硬件资源的区域分离,并通过AXI总线的硬件逻辑确保普通区域的组件无法访问安全区域的资源。

将敏感数据存储在安全区域,将安全软件运行在安全处理器内核中,确保敏感数据存储和访问免受攻击,如使用键盘或触摸屏输入密码等难以防护的攻击。

TrustZone架构的总线结构中,

•AXI是一种面向高性能、高带宽、低延迟的片内总线,用于连接高速设备;•APB是一种低门数、低带宽的外设总线,用于连接低速设备,APB通过AXI-to-APB桥连接到AXI系统总线上。

AMBA协议是用于连接和管理片上系统中功能块的开放标准和芯片互连规范,TrustZone使用的AXI总线和APB外设总线均遵循AMBA3协议。

为支持TrustZone技术,AMBA3 AXI系统总线在每个读写信道都增加了一个额外的控制信号,称作非安全位(NS位)。

当主设备向总线提出读写事务请求时,必须将控制信号发送到总线上,总线从设备的解码逻辑解释该控制信号,允许安全主设备对安全从设备的访问,并拒绝非安全主设备对安全从设备的访问,依据外设的硬件设计和总线配置,从设备或总线可以产生错误访问的状态信号。

TrustZone架构通过AMBA3 APB外设总线提供了保护外设安全性的特性,包括中断控制器、时钟及用户I/O设备。相比仅仅保护数据安全,TrustZone架构的安全世界可以解决更广泛的安全问题。

安全中断控制器和时钟允许非中断安全任务来监控系统,安全时钟源保证了DRM的可靠性,安全键盘保证用户输入密码的安全性。

为了使现有AMBA2 APB外设与实现TrustZone技术的系统兼容,APB总线没有带对应的NS位,而由AXI-to-APB桥负责管理APB外设的安全。

AXI-to-APB桥会主动拒绝异常的安全设置事务请求,而不会把请求发送给外设。

(2)处理器内核安全性

通过ARM处理器内核的扩展,普通区域和安全区域的代码能够以分时的方式安全有效地运行在同一个物理处理器内核上,不需要使用专用安全处理器内核,在保证处理器内核安全的同时兼顾了芯片面积和能耗。(有点像时间片任务切换)

目前ARM主流产品,如ARM Cortex-A5、ARM Cortex-A7、ARM Cortex-A9等处理器均已支持前述处理器内核安全扩展。

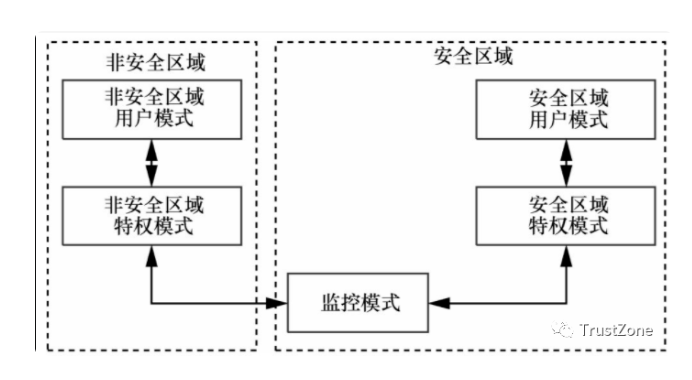

在处理器架构上,每个带TrustZone安全扩展的处理器核都提供两个虚拟核:安全核和非安全核。

它们分属不同的执行环境安全区域和非安全区域,如下图所示。同时处理器引入了一个特殊的机制——监控模式,负责不同执行环境间的切换。非安全核仅能访问非安全系统资源,但安全核能访问所有资源。

ARM CP15协处理器中引入一个安全配置寄存器(SCR),该寄存器中有一个NS位,NS位表明当前处理器所处的安全状态:0代表安全态,1代表非安全态。

安全配置寄存器中的NS位是TrustZone对系统所做的关键扩展,该NS位不仅可以影响CPU内核和内存子系统,还可以影响片内外设的工作。

当ARM处理器处于特权模式工作状态,

•即系统模式(sys)、

•中断模式(irq)、

•快速中断模式(iq)、

•管理模式(svc)、

•数据访问终止模式(abt)或未定义指令终止模式(und)时,可以读写安全配置寄存器,而在用户模式(usr)时不允许读写。

NS位只能被运行在安全态且处于特权模式的软件改变,系统在非安全态时不能访问SCR寄存器,通过NS位的状态控制处理器安全状态的切换。

在TrustZone处理器中同时引入了一个特殊的模式——监控模式。监控模式是一种特殊的安全状态,当系统处于监控模式时,不管NS位是否为0,都可以访问安全世界的资源。

从非特权模式到特权模式只能通过异常来进行,与该过程类似的,从非安全态到监控模式也是通过异常进行的。

从非安全状态可以通过3种异常进入监控模式:执行SMC(Secure Monitor Call,安全监视调用)指令、外部中止、FIQ(Fast Interrupt Request,快速中断请求)和IRQ(Interrupt Request,中断请求)。监控模式还负责实现两个虚拟核之间切换时的上下文备份和恢复。

监控器可以在没有任何执行环境的代码帮助下直接捕获FIQ和IRQ,当执行流到达监控器的时候,监控器能将中断请求路由到相应的中断处理程序与安全中断控制器结合起来,从而让安全中断源发出的中断不被普通世界软件操作。(是不是中断管理器)

ARM推荐使用IRQ作为普通世界中断源,FIQ作为安全世界中断源。如果中断发生在相应的执行环境,则不需要进行执行环境的切换;如果中断发生在另外的执行环境,由监控器控制切换执行环境。

一般情况下在执行监控器代码的时候应该关闭中断。同时在CP15协处理器中还引入一个配置寄存器以防止普通世界的恶意软件屏蔽安全世界的中断。

内存管理是实现安全管理的另一关键技术。TrustZone技术的内存管理,通过对一个增强的内存子系统MMU(Memory Management Unit,内存管理单元)和Cache增加相应的控制逻辑实现。

ARM处理器中一级存储系统的主要部件就是内存管理单元,用来将程序和数据的虚拟地址转换为物理地址。页表描述了虚拟地址到物理地址的映射关系,以及每一页的访问权限和Cache属性。

在有MMU但是没有TrustZone安全扩展的ARM内核中,只有一个页表基地址寄存器,通过特权模式代码重写页表基地址寄存器,使其重新指向一个新的页表来提供多个独立的地址空间。

在TrustZone安全扩展处理器中,有两个页表基地址寄存器,不同安全状态使用不同的页表基地址寄存器,相当于有两个虚拟MMU,每个虚拟MMU分属不同的虚拟核,使每个执行环境有一个本地页表集,各个执行环境的虚拟地址到物理地址的转换是独立的,在切换执行环境时不需要切换页表。

这样,在两种模式切换时不必刷新缓存,进而提升软件在这两种模式间通信时的性能。为了实现这种特性,L1、L2等各级处理器缓存需要为Tag域增加一个NS位,用来标识这一行的安全状态。无论Cache行的安全状态如何,只要没被锁住,都可以被换出到主存中,为新的缓冲数据留出存储空间。高性能设计能够在Cache中同时支持安全模式及普通模式的数据缓存,是一个非常有用的特性。

TrustZone技术中使用协处理器实现处理器扩展功能,ARM协处理器附属于ARM处理器,通过扩展指令集或提供配置寄存器来扩展内核功能。CP15协处理器是TrustZone技术中使用的最重要的ARM协处理器,用于控制Cache、TCM和存储器管理。

协处理器通过设置某些寄存器实现普通世界和安全世界的工作协同。其中某些寄存器是有备份的,即普通世界和安全世界各有一个这样的寄存器,此时修改寄存器只会对它所在执行环境起作用;有的协处理器寄存器是没有备份的,对它的修改会影响到全局,如控制对Cache进行锁定操作的寄存器。

对这种全局寄存器的访问必须严格控制,一般只对安全世界提供读写权限,而普通世界只能读取。

(3)调试安全性

通过安全感知的调试结构对安全区域的调试进行严格控制,而不会影响普通区域的调试。

这个部分之前我曾经写过关于JTAG的文章,可以在我的专栏里搜索一下JTAG;我们知道JTAG的原理和功效,就会知道JTAG的目的是为了调试,但是如果不加以控制就会成为恶意者的后门,所以一般的Soc芯片都会进行相应的权限控制。

软件架构

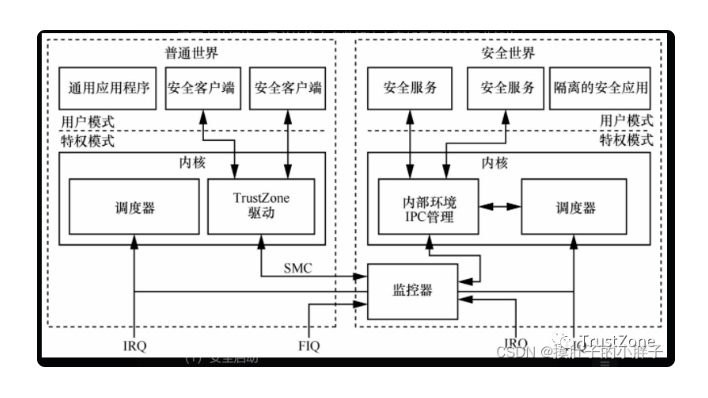

TrustZone硬件架构将新的安全扩展特性应用于CPU内核之中,为建立安全执行环境提供了硬件基础,操作系统厂商、手机制造商和芯片厂商可以根据自己的安全需求,在一个可共用的硬件框架之上扩展和开发不同的安全解决方案。

ARM同时提供了一个典型的安全软件架构,如图3-3所示。安全软件架构包括安全世界、普通世界两个区域,通过监控器实现两者的切换。目前的绝大多数解决方案都是严格基于此架构实现。

TrustZone的安全软件架构设计基于智能终端的使用模式,包含

•安全启动、

•监控模式、

•TrustZone API 3个方面。

(1)安全启动

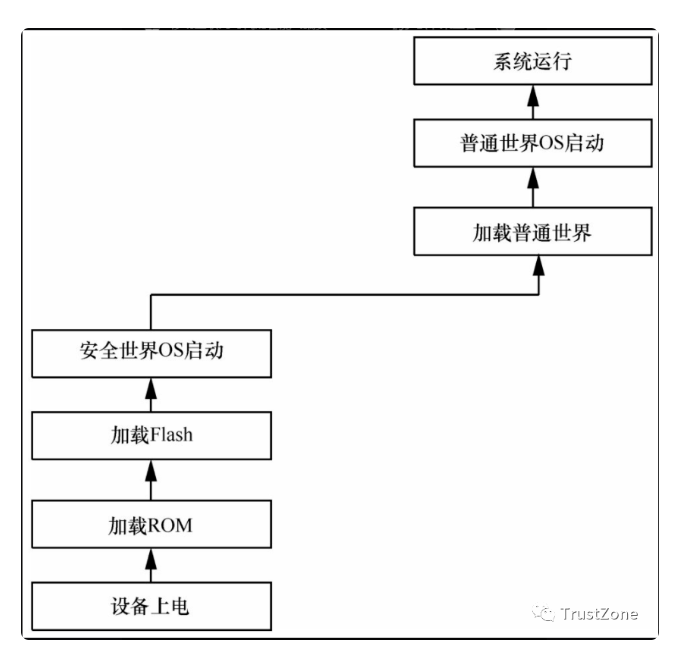

TrustZone软件安全启动过程如下图所示。

在系统初始化时,在安全特权模式下从片内安全引导代码区启动,采用这种方式以避免OS被攻击。

片内安全引导代码完成系统安全状态的设置,然后引导OS启动。

在OS启动的每一个阶段,功能模块均需通过验证才允许加载。

通过检查保存在安全域内的签名可以保证OS引导代码的完整性,避免终端设备被非法重新硬件编程。

(可以看看我在ATF的那个翻译-COT信任链和我写过的SecureBoot的文章,这种启动链的安全校验更多地是像一种思维模式)

(2)监控模式

TrustZone监控器实现软件系统在安全世界和普通世界之间的切换管理。

如前所述,普通世界的应用程序可以通过3种异常进入监控模式:执行安全监视调用SMC指令、外部中止、FIQ和IRQ。

典型的切换过程如下。当普通世界的应用需要切换到安全世界的服务时,首先切换到普通世界的特权模式,在该模式下调用SMI,处理器将切换进入监控模式;

监控模式首先备份普通世界的运行时环境和上下文,然后进入安全世界的特权模式,再转换为安全世界的用户模式,此时的运行环境为安全世界的执行环境,可以执行相应的安全服务。

上述过程包括普通世界和安全世界的切换,以及用户模式和特权模式的切换。执行环境的切换只有在各自世界的特权模式下才能实现,但应用的调用关系只能在用户模式下执行,避免应用越权使用系统级别的调用。(执行和切换)

监控模式中的代码实现两个虚拟运行世界的上下文备份和恢复。CP15协处理器中的安全状态寄存器SCR的NS位标志着当前处理器所处的安全状态, 该寄存器不允许被普通世界的应用访问。由于监控器负责环境切换时对状态的存储和恢复,所以执行环境的切换不需要在各自系统中增加环境切换代码。

TrustZone通过优化中断向量表的设计避免恶意中断攻击,并满足必要的执行环境切换需求。

TrustZone把中断向量表分成两部分:安全的中断向量表置于安全存储器,而且指向安全的中断处理程序;

非安全的中断向量表和处理程序置于普通存储器中,以避免某些恶意程序修改安全的中断向量表和处理程序或其他通过非法手段进入安全世界。

处理器执行完安全任务后,TrustZone监视器最后还要执行一遍SMI指令,其目的在于清除CP15的NS位。

监视器还会将之前的内容重新存回所有寄存器,使处理器恢复到之前的非安全状态。

通过这种恢复机制,所有安全世界中的指令和数据还是原值,未受任何的修改,这也是安全世界之所以安全的关键。(函数的堆栈调用)

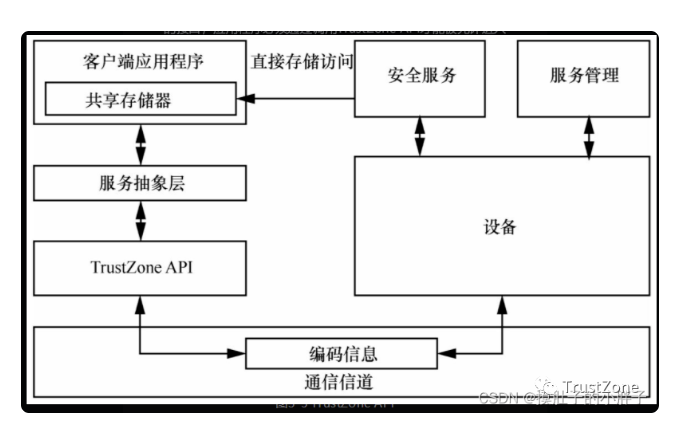

(3)TrustZone API

TrustZone API为希望获取安全保护的应用程序提供了一个标准接口,定义了运行在普通世界中的客户端与安全世界之间交互的接口,应用程序必须通过调用TrustZone API才能被允许进入安全世界。

应用使用TrustZone API能够与一个独立于实际所在系统的安全部件进行通信,使开发者能够专注于应用程序本身的功能和性能,并且缩短开发周期,同时保证应用的安全性。

但是,希望使用TrustZone提供安全保护的应用程序必须根据它们运行的安全平台进行重写,导致市场被过度细分,制约了应用程序与服务之间良好的生态环境的形成。

客户端包括应用程序和Service Stub服务抽象层,调用普通世界下的TrustZone API呼出,通过TrustZone交互机制传送给安全世界下的服务管理器和安全服务。

大部分的API函数都设计为客户端程序与安全服务间的沟通桥梁,两者通过结构体信息(Structured Messages)及共享内容(Shared Memory)这两个机制形成通信信道。

当传递的信息量较小时,可通过结构体信息来传送及沟通;而当传递的信息量较大时,则会直接将客户端的memory映射到安全服务区的memory空间,然后通过该Share Memory作为客户端与服务端之间直接存取信息的缓冲区。(这个部分就是动态TA加载)

2、SecureBoot安全启动技术

由于厂家版本的OS大多嵌入了相当数量的厂家生态应用,同时不明来源的系统镜像和不可靠的刷机是系统风险引入的一个重要途径,多数手机厂商希望用户能保留和使用厂家的OS版本。另外,有的恶意病毒会通过从定向系统启动位置引入安全风险,由此提出了系统安全启动技术。

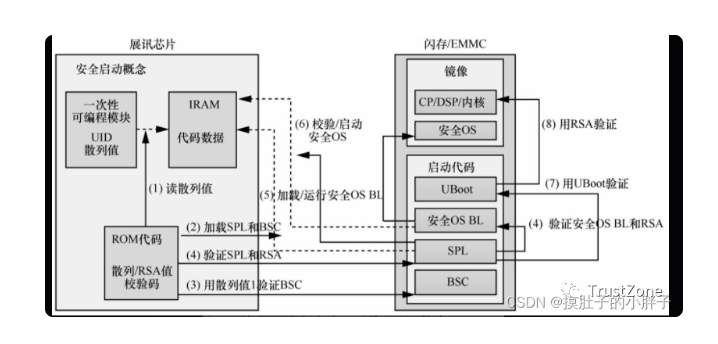

安全启动技术的逻辑大同小异,本节以展讯的SecureBoot为例说明。

展讯的SecureBoot安全启动技术采用多级认证的机制,建立了自底向上的可信启动过程。

SecureBoot对系统软件采用签名认证的方式,在手机出厂前对手机操作系统的Image文件进行签名认证,计算签名文件的散列值并写入芯片的一次性可编程模块。手机每次启动时先校验系统的散列值,然后对签名Images逐级校验,实现从手机芯片到系统软件的链式校验过程。

防止非授权更改甚至替换手机原版操作系统中固件或者操作系统,避免手机出厂后没有得到客户签名认证的非授权操作,保护手机中原有的操作系统和软件版本。

SecureBoot在启动过程中从Rom Code到Images采用了多层链式校验机制;包括对RomCode的散列校验,对SPL的完整性的RSA校验。需要注意的是,RSA私钥是SecureBoot的保障,需要小心保存。

SecureBoot安全启动的流程如下。

•(1)ROMCode读取存储于一次性可编程模块中BSC(Base Station Controller,基站控制器)的散列值和UID(User Identification,用户身份)。

•(2)加载SPL(Second Program Loader,第二次装载系统)和BSC。

•(3)RomCode利用散列函数来验证BSC的完整性。

•(4)RomCode利用RSA算法来验证SPL的完整性。

•(5)加载和运行安全操作系统引导程序。

•(6)验证和运行安全操作系统。

•(7)SPL利用RSA算法验证UBoot。

•(8)UBoot利用RSA算法验证bootimage、recoveryimage、modem、sp等。

这个逻辑其实感觉是单核的,不过感觉逻辑挺快乐的。不像实验室设计的,好几个核,反正很花里胡哨,流程复杂。

不过这个是芯片层面的东西了,下一篇看看加密芯片

参加资料

•《移动互联网时代的智能终端安全》

作者:Hcoco

文章来源:TrustZone

推荐阅读

更多物联网安全,PSA等技术干货请关注平台安全架构(PSA)专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入PSA技术交流群,请备注研究方向。