智能汽车目前大量部署了人工智能系统,因此在传统安全问题之外,人工智能所带来的安全问题,尤其是智驾系统中部署的人工智能模型所带来的安全问题变得愈发严峻和值得关注。因此,本文主要结合AI系统自身存在的安全问题和智能驾驶汽车的应用场景,从对抗场景安全问题、自然场景安全问题、AI黑盒性和AI隐私问题分别介绍可...

之前有位读者让聊聊AUX协议,可能是因为之前讲DP,没有深入这部分,于是今天专门在节前整理点资料,聊聊这个。

卷积神经网络(Convolutional Neural Networks, CNN)的核心技术主要包括以下几个方面:局部连接、权值共享、多卷积核以及池化。这些技术共同作用,使得 CNN 在图像和语音识别等领域取得了显著成就,并广泛用于车辆自动驾驶的图像目标识别中。

在人工智能和自动驾驶技术飞速发展的今天,智能座舱已成为汽车行业的“新战场”。从多屏互动到情感智能,从舱驾融合到 AI 大模型支持,座舱芯片正悄然改变着我们的驾驶体验。

原创:功能安全 26262 中的电子元器件失效率怎么理解?如何计算?3000 字教你搞定!电子元器件失效率数据是功能安全开发的不可或缺的重要依据,功能安全 26262 中的电子元器件失效率怎么理解?如何计算呢?在功能安全标准 ISO26262 中,关于器件失效率的定义主要与汽车电子系统的安全完整性等级,也就是 ASI(Automotive...

在汽车行业飞速变革的今天,每一位汽车安全工程师都像在走钢丝 —— 左手托着乘客的生命安全,右手扛着企业的成本压力。当自动驾驶、智能网联技术掀起浪潮,高等级安全认证(如 ASIL D)成为刚需,如何在 "安全底线" 与 "成本红线" 之间找到平衡,成了这个时代最棘手的行业命题。

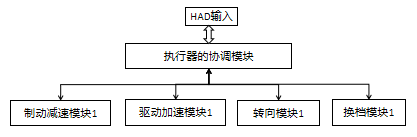

原创:浅谈 L3 系统对执行器的功能安全需求 对于 L3 的设计,首先争论较多的是 L3 接管条件的具体定义,是驾驶员一直在环执行驾驶任务的功能描述,还是在 L3 控制过程中,驾驶员仅在 L3 系统报故障后才进行接管的情况?本文所述为后者,在 L3 功能启用时,若无需驾驶员接管操作,车辆驾驶可全由 L3 系统完成。在 L3 设计...

本文节选自机工社 25 年 3 月出版的《一本书读懂智能汽车安全》,该书是一本全面讲解智能汽车安全的通俗性著作,系统讲解了汽车研发全流程的功能安全、预期功能安全和网络安全,以及三者在汽车研发中的融合之道。本书由 SASETECH 汽车安全社区组织编写,汇聚了博世、蔚来、小鹏、磐时、卓驭、地平线、上汽、吉林大学等业...

(1)分组密码算法的工作模式如 ECB\CBC 等明确要求输入必须是分组大小的整数倍,流密码模式除外;

Android 平台上,GateKeeper+KeyMint 是一种常见的密码解锁方案,基于仅用户知道的密码保护用户的数据。Weaver 是一种基于 Secure Element 等防篡改硬件,旨在增强密码保护用户数据的解决方案,提供了 device-off security threat model 和 brute force password guessing 两个关键特性。

原创:智能驾驶车辆行车安全的两难困境和不可能三角场景环境交通流行为是影响智能车辆行车安全的重要因素。不良的环境交通流行为给本车带来风险。特定参数组合(驾驶员反应时间、最大加减速等)、特定状态组合(位置、速度等)下,智能车辆面临特殊安全决策困境:一旦触发事件发生(如前车急停),系统状态不可避免导向交...

Hi!早哦。今天又是宠读者的一天,应允聊聊 UEFI。前言很难用一篇文章去完全的了解 UEFI,这篇文章的目标是希望能让不了解的朋友看完后达到下面几个目标:UEFI 是什么:概念UFEI 用来干什么:应用UEFI 有些什么东西:架构UEFI 重点场景:启动UEFI 学习资料:推荐通过这几个部分,咱们能一起搭建起一个关于 UEFI 简要知识...

写在前面:在安全芯片的设计与验证过程中,工程师常会遇到一个关键概念——BIST(Built-In Self-Test,内置自检测)。初次接触这一术语时,许多人容易将其简单理解为“芯片内部的自动化测试功能”,甚至误认为其仅用于生产阶段的缺陷筛查。然而,BIST 机制的核心价值远不止于此:它不仅是芯片功能安全的“第一道防线”,更是实...

在上篇文章,我们从通用的冯诺依曼架构聊到 CPU 组成架构,再到汽车嵌入式控制单元 MCU,以及多用于安全监控的基础芯片 SBC,这部分内容也是传统汽车控制单元基本的组成内容,算是旧识吧。

模型是表示另一个事物的某种东西,可以是一个比真实物体小的物理对象,或者是一个可以用于计算的简单描述[30]。

在上篇文章,我们从通用的冯诺依曼架构聊到 CPU 组成架构,再到汽车嵌入式控制单元 MCU,以及多用于安全监控的基础芯片 SBC,以及智能汽车必不可缺的 GPU,这部分内容也是传统汽车控制单元基本的组成内容,算是旧识吧。

本篇属于汽车功能安全专题系列第 12 篇内容,我们来聊聊汽车功能安全软件详细设计及安全测试相关内容。

功能安全标准是确保系统或模块在故障条件下能够可靠运行并避免不可接受的风险的标准。不同的行业和应用领域有不同的功能安全标准,以 ISO 26262, IEC 61508, EN 50128, DO-178C 为例,这些标准对软件开发模型的定义有共通点,在具体规定中也有一些不同。

我们知道内存也可以用于存储数据,而且读写速度非常快,通常比磁盘要快几个数量级,但是内存资源是珍贵而且有限的,通常我们的服务器内存也就是 16G,32G。

原创:整车时钟同步系统的功能安全与信息安全融合设计无论是在 ISO26262 标准中,还是在 ISO21434 标准中,都在讨论两个概念应该充分的沟通和协同,因为功能安全的需求和信息安全的需求和目标可能并不一致却相互影响。例如:增加一个内容的信息安全性往往需要对来源进行身份认证和完整性认证,但复杂的加密算法会增加处理...