思考:

1、为什么要学习 MESI 协议?哪里用到了?你确定真的用到了?

2、MESI 只是一个协议,总得依赖一个硬件去执行该协议吧,那么是谁来维护或执行的呢?

3、你不理解的真的是 MESI 吗,真的需要学习 MESI 吗?应该是 cache 架构吧

4、core0 和 core1 之间的一致性是 MESI?那 cluster0 和 cluster1 之间的呢?sytem1 和 sytem2 之间的呢?

5、MESI 协议中的 M、E、S、I 的比特位,都是存在哪里的?

1、系统中有哪些一致性需要维护

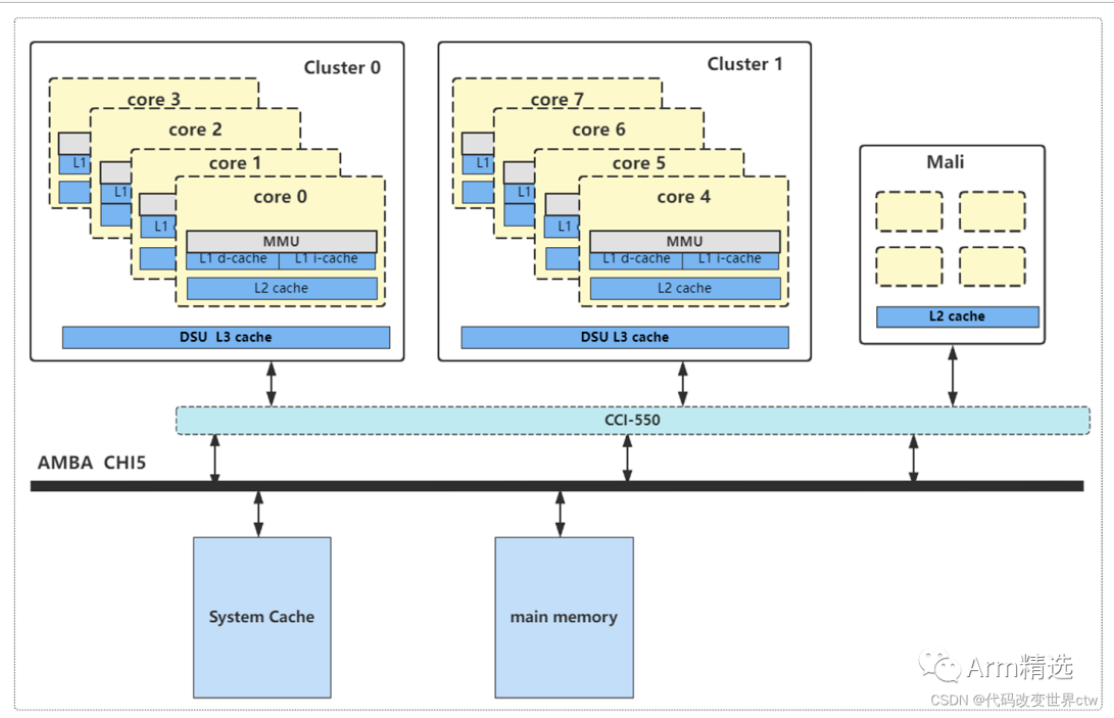

进入正文,我们来看现代 ARM 架构体系(DynamIQ 架构)中的 cache 层级关系图。注意 L1/L2 都在 core 中,L3 在 cluster 中。

所以从以下图中就能够直观的看到答案了:

- (1)core0、core1… 之间的一致性 需要维护

- (2)cluster0 和 cluster1 之间的 L3 Cache 一致性 需要维护

- (3)system 之间的一致性需要维护

其中,core0、core1 之间的一致性是遵从 MESI 协议,而 cluster0/cluster1 之间的一致性、多个 system 之间的一致性并没有遵从 MESI 协议。

所以本文重点介绍的,也就是 core0、core1 之间的一致性,即 MESI 协议。

2、core 硬件对 MESI 协议的支持

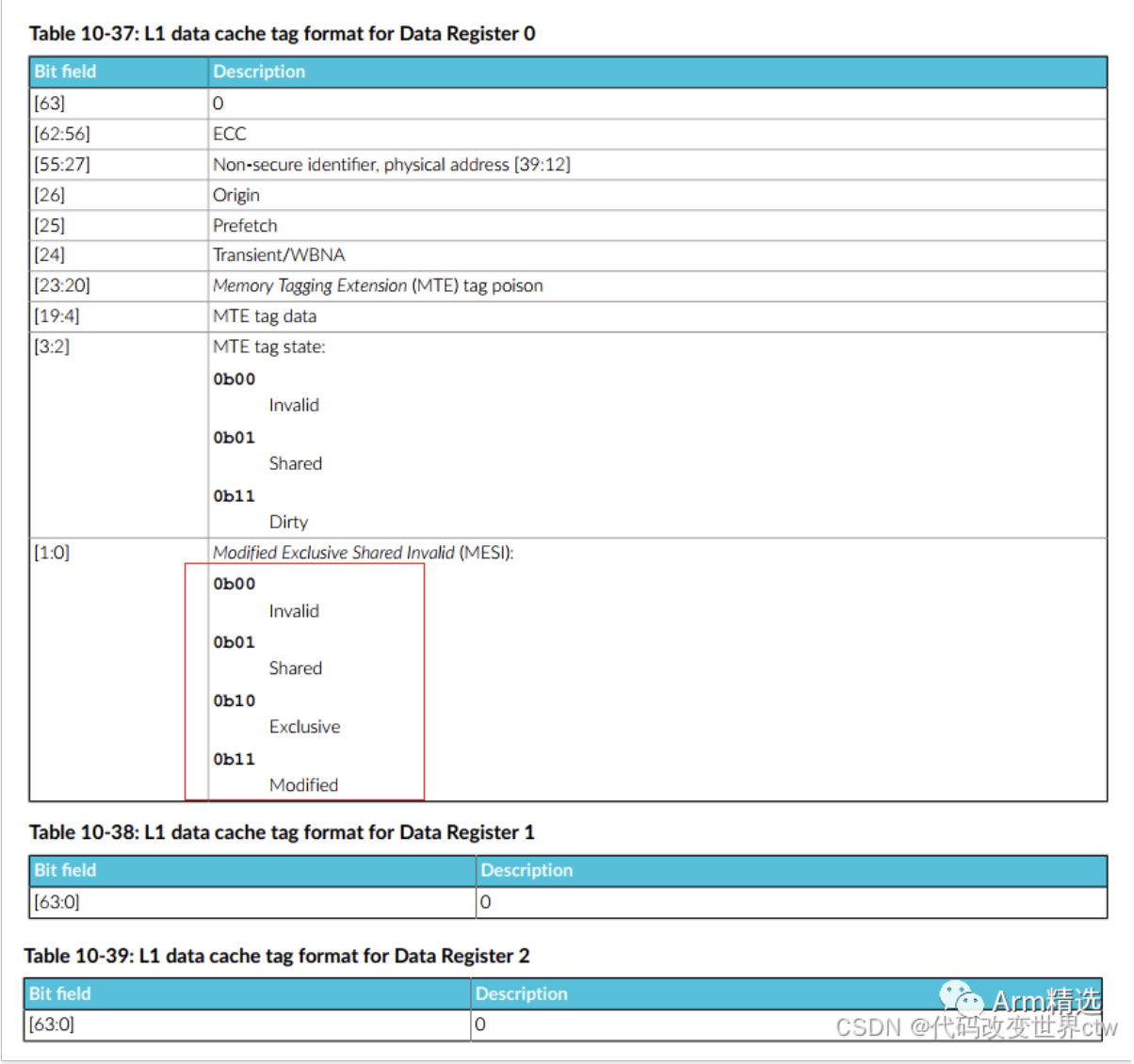

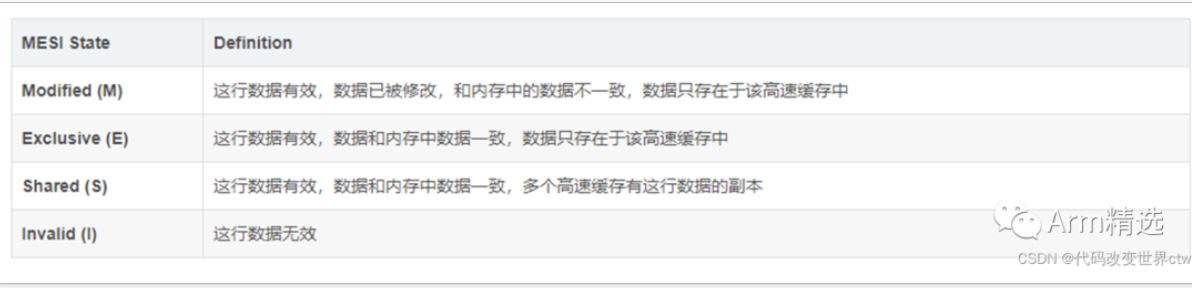

接下来,进入下一个问题, MESI 协议中的 M、E、S、I 的比特位都是存在哪里的?这个问题并不难,告别懒惰,多翻一翻 ARM TRM 手册就能找到答案,如下是armv9 -- cortex-A710 TRM手册中的,cache 的 TAG 里都有什么?

答案显然易见,在 Cache 的 TAG 中,有两个比特位表示了 MESI 的状态

3、MESI 协议的原理

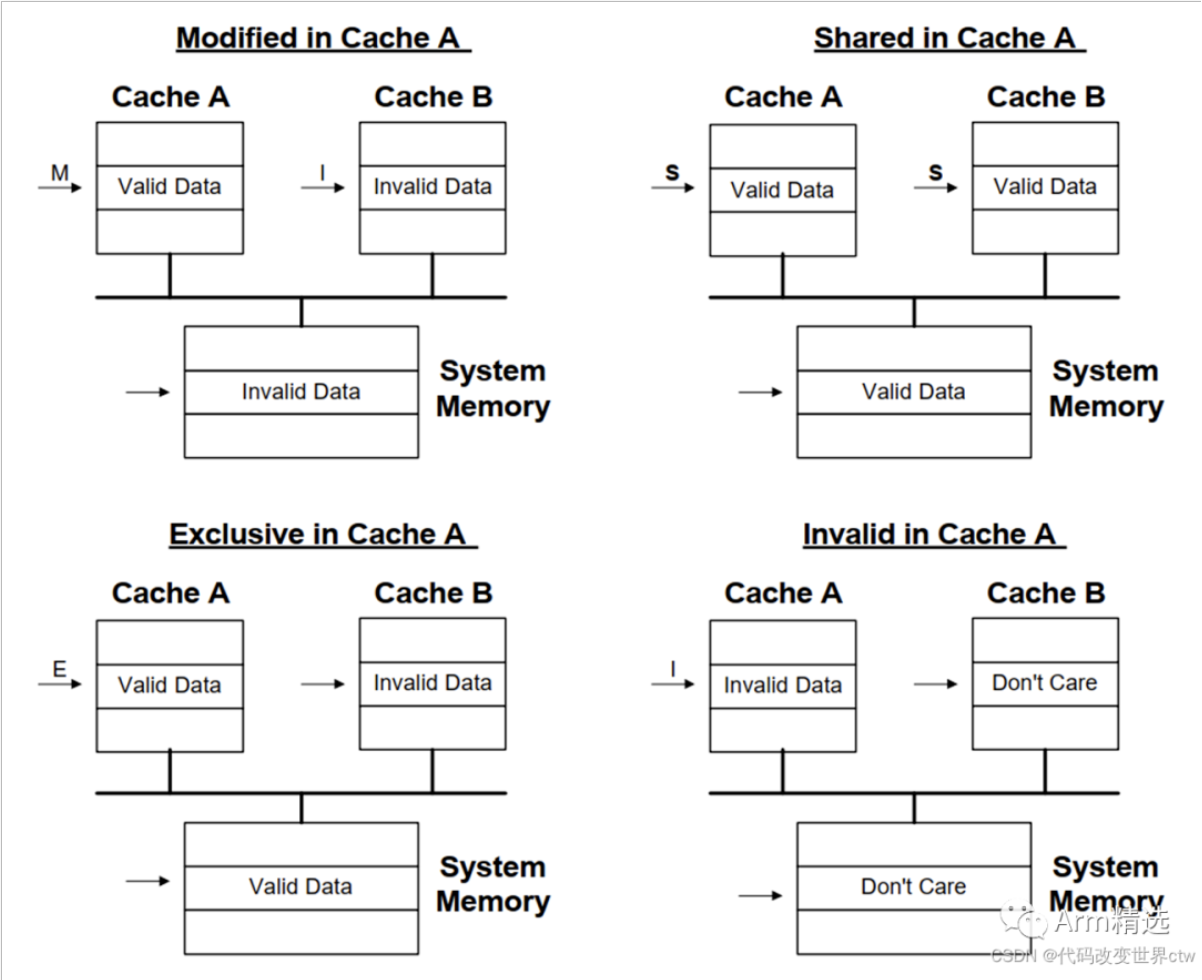

接下来进入本文的核心,MESI 协议到底是什么?怎样维护一致性的?

(看以下图表,我就不说话了)

Events

- RH = Read Hit

- RMS = Read miss, shared

- RME = Read miss, exclusive

- WH = Write hit

- WM = Write miss

- SHR = Snoop hit on read

- SHI = Snoop hit on invalidate

- LRU = LRU replacement

Bus Transactions

- Push = Write cache line back to memory

- Invalidate = Broadcast invalidate

- Read = Read cache line from memory

作者:baron

文章来源:Arm精选

推荐阅读

- Armv9 Cortex-A720的L1 memory system 和 L1 Cache

- Linux Kernel(armv8-aarch64) 的原子操作的底层实现

- 深入理解Armv9 DSU-110中的L3 cache

欢迎关注ARM精选专栏, 欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。