格式有点乱,原文在这里:

【CHI】(一)基础概念

本章介绍了CHI体系结构和术语。它包含以下部分:

- 体系结构概述

- 拓扑结构

- 术语

- 事务分类

- 一致性概述

- 组件命名

- 读数据来源

一、CHI架构

CHI架构是一个可扩展的、支持一致性的集线器接口和由多个组件使用的片上互连。根据系统要求的PPA(performance, power, and area),CHI体系结构允许组件连接的灵活拓扑结构。

1.1组件

基于CHI的系统组件可以包括:

- 独立处理器

- 处理器簇

- 图形处理器

- 内存控制器

- I/O桥

- PCIe子系统

- CHI互连线

1.2关键特性

该体系结构的主要特性是:

- 可扩展的体系结构,支持从小型系统扩展到大型系统的模块化设计。

- 独立的分层方法,包括协议层、网络层和链路层,具有不同的功能。

- 基于数据包的通信。

- 所有的事务都由一个基于互连的Home节点处理,它可以协调所需的窥探snoop、缓存cache和内存memory访问。

- CHI一致性协议支持:

——cache line大小为64byte

——使用Snoop filter和基于directory的系统,用于减少不必要的snoop事务。

——MESI和MOESI缓存模型,并从任何缓存状态转发数据。

——增加了 partial 和empty的cache line状态。

- CHI事务集包括:

——丰富的事务类型以支持PPA高效的系统缓存实现。

——支持互连中的原子操作和同步。

——支持高效执行独占访问的功能。

——将数据移动到更接近预期的使用点来实现高效的数据移动和替换。

——通过分布式虚拟内存(DVM)操作进行虚拟内存管理

- 支持Retry机制来管理协议层资源;

- 支持端到端的Qos(Quality of Service);

- 可配置的数据宽度来满足系统需求;

- 支持ARM TrustZone;

- 低功耗信号,可以使能flit级别门控、组件之间的建断链来支持时钟门控和电源门控、协议层的活动信号来控制电源和时钟;

1.3 CHI层次

CHI层次按功能可以划分为:

- 协议层(Protocol)

- 网络层(Network)

- 链路层(Link)

二、拓扑结构

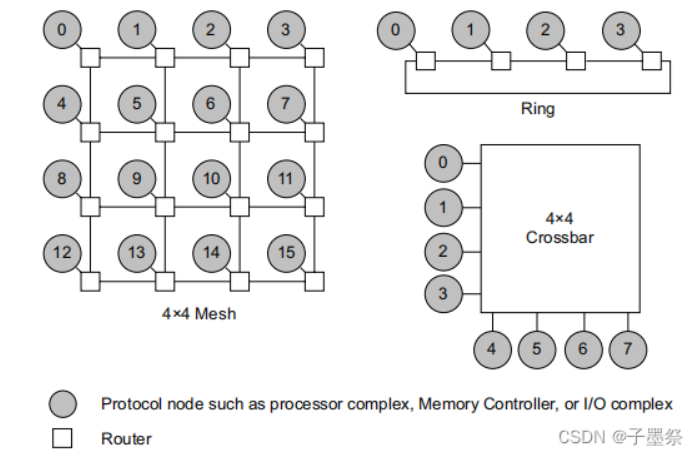

CHI架构主要是与拓扑无关的。然而,本规范中包含了某些与拓扑相关的优化,以使实现更高效。图1-1显示了三个拓扑示例,以显示可用的互连带宽和可扩展性选项的范围。

图1-1

Crossbar:

这个拓扑构建起来很简单,并且自然地提供了一个具有低延迟的有序网络。它适用于连线相对较小的地方。该拓扑结构适用于与少量节点的互连。

Ring:

这种拓扑提供了在互连布线效率和延迟之间的权衡。延迟随环上节点的数量呈线性增加。这种拓扑结构适用于中等大小的互连。

Mesh:

这种拓扑以牺牲更多的连线为代价提供了更大的带宽。它是非常模块化的,并且可以通过添加更多的行和列的交换机来很容易地扩展到更大的系统。这种拓扑结构适用于更大规模的互连。

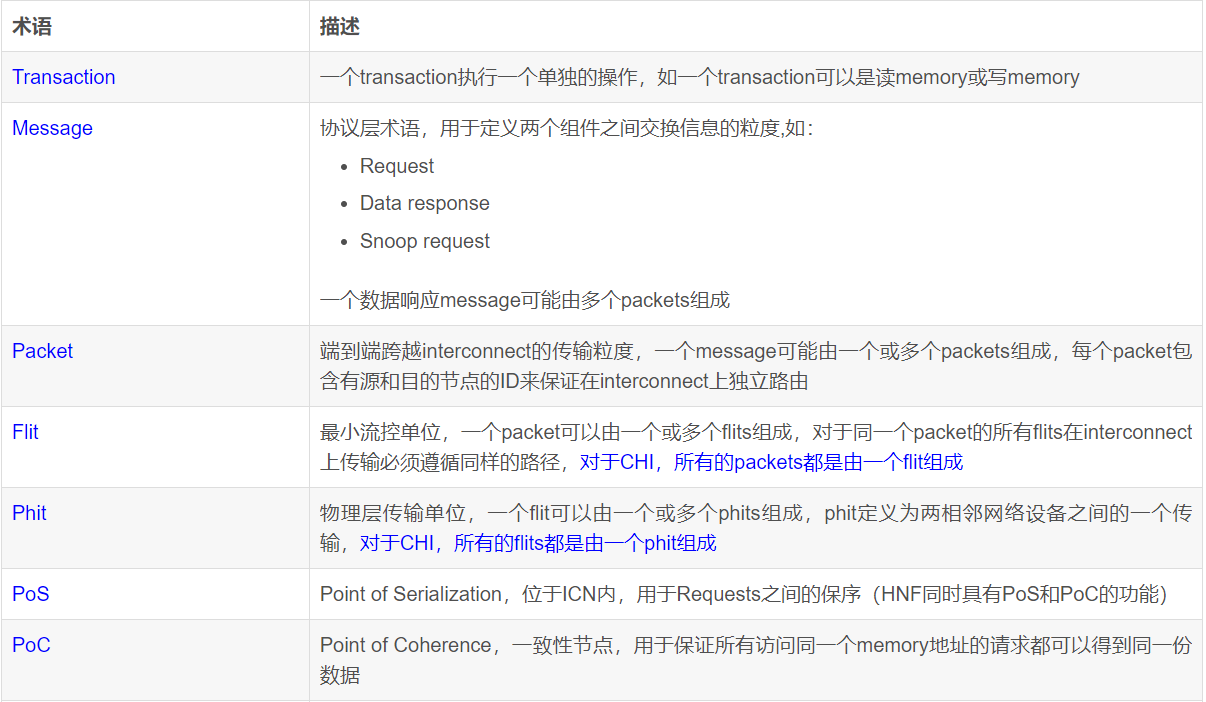

三、术语

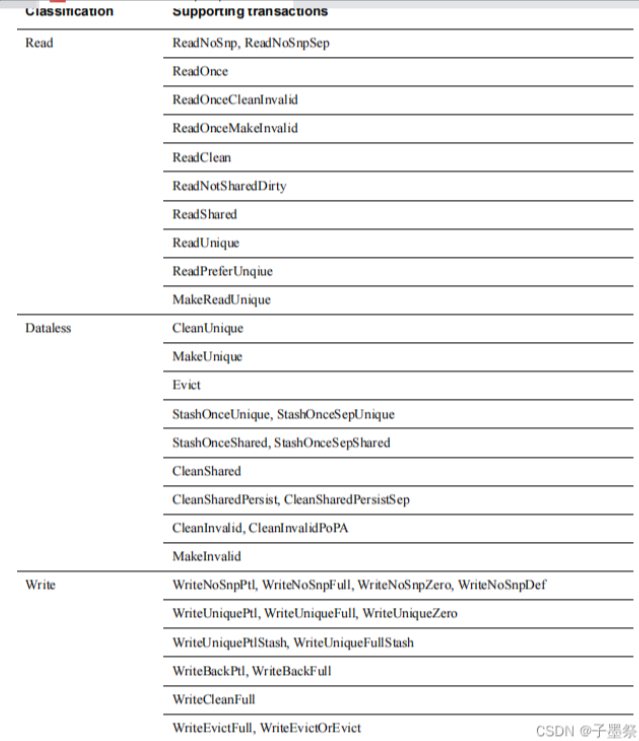

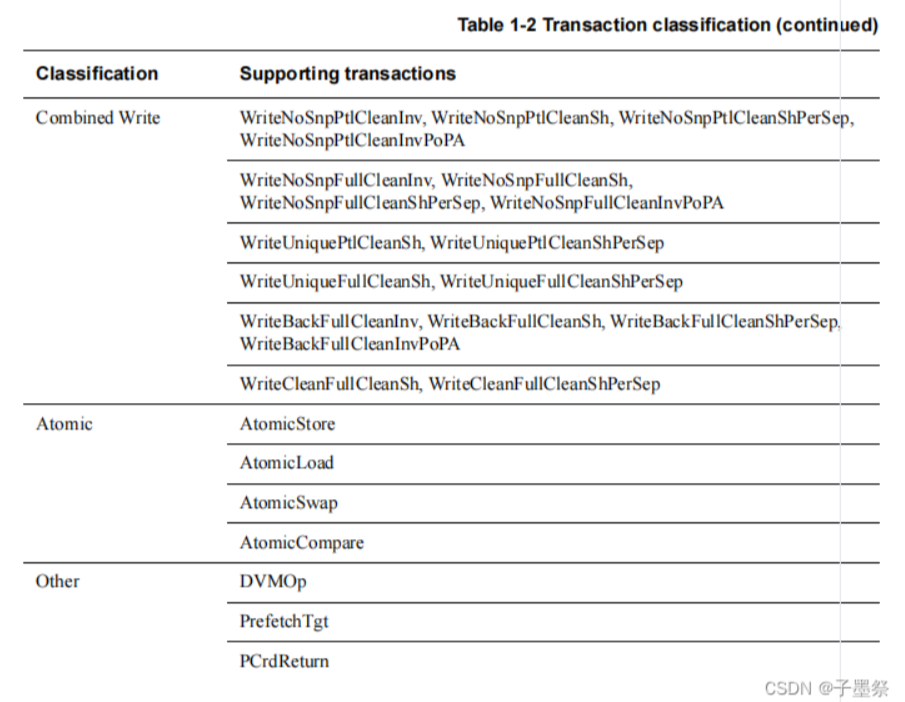

四、事务类型

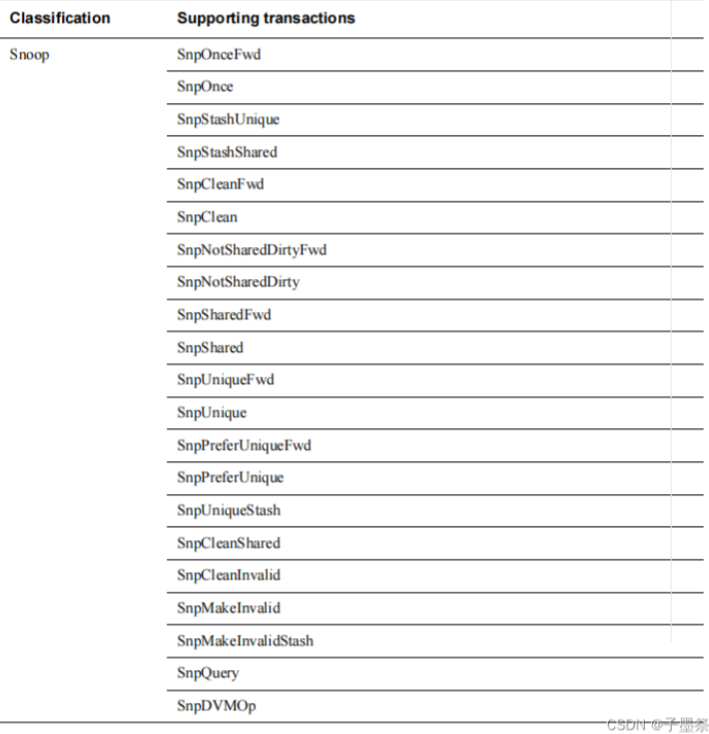

本规范(CHI issueF)所支持的协议事务及其主要分类:

(后续会再开一篇专门描述各种事务及其使用场景)

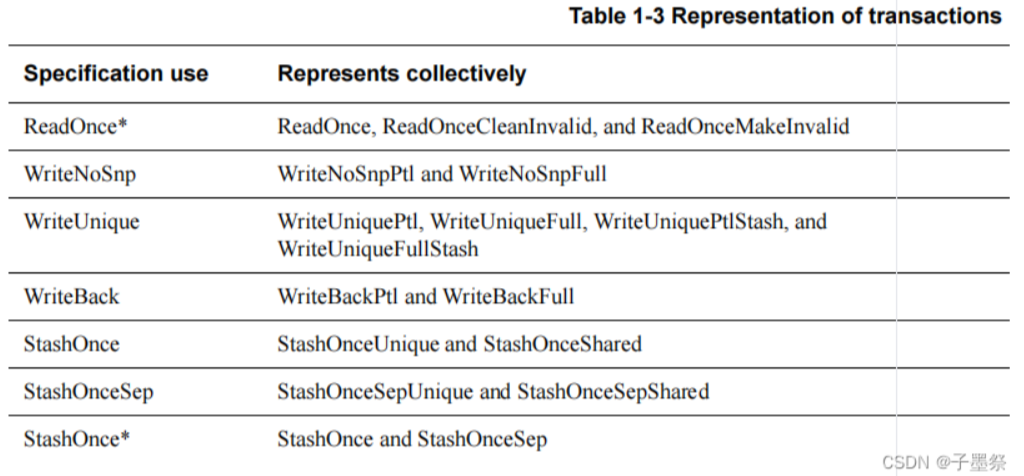

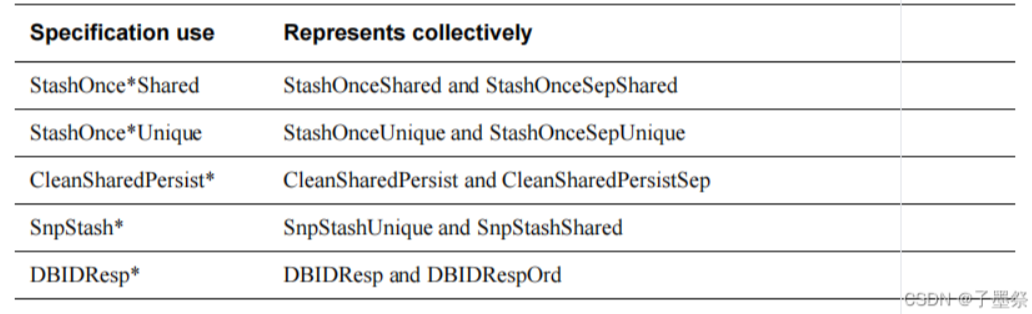

下表显示了事务的表现形式:

五、一致性概述

硬件一致性使系统组件能够共享内存,而不需要软件缓存维护来保持一致性。

如果两个组件往相同地址的memory发起写操作,这些操作可以被所有的组件以相同的顺序观察到,那么这个memory区域就是一致性的。

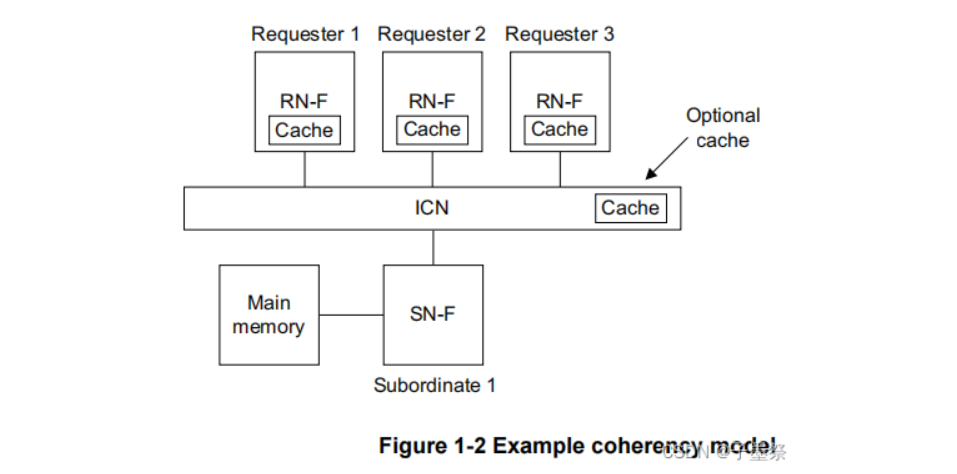

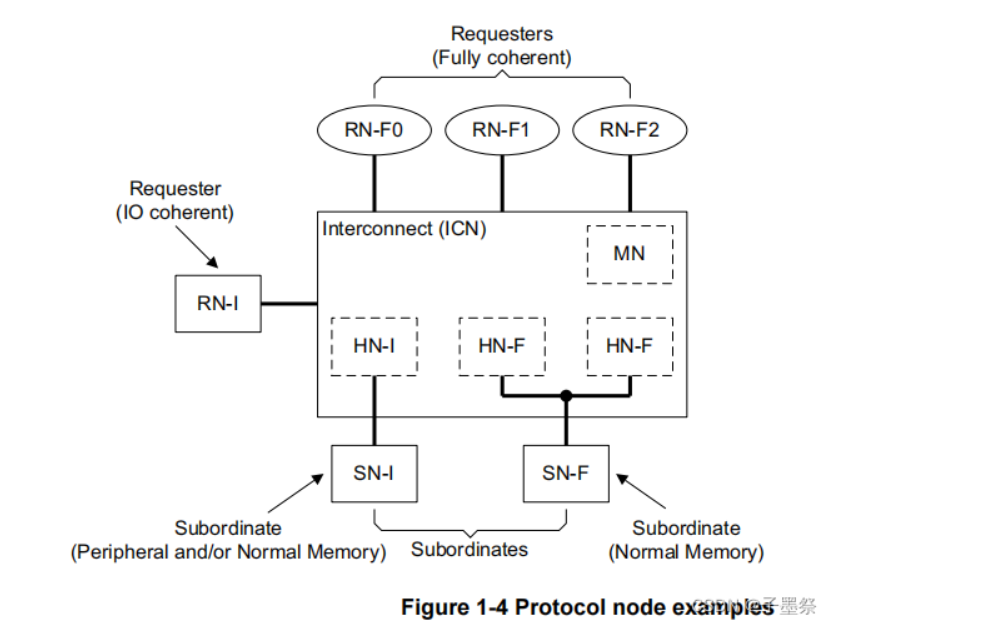

5.1 coherency model

图1-2所示为包含三个master组件的一致性系统,每个master组件包含一份loacl cache和一致性协议节点。CHI协议允许memory数据存放在一处或多处master cache当中。

一致性协议强制要求,当需要存数据时,先把所有其它masters的数据备份失效掉,这样一致性协议可以使得所有的masters获取到任何地址的正确的数据值。在存储完成后,其它masters可以获取到新的数据到自己local cache;

CHI协议允许(不强求)主存的数据不是实时更新,只有在所有master的cache都不需要该数据备份时,才把数据刷新到主存中;

协议使得master可以确定一份cacheline是否是唯一的或者存在多份拷贝。如果是唯一的,master可以直接改变它的值不需要知会系统中其它masters,如果不是唯一的,master必须使用恰当的transaction知会其它masters;

所有的一致性是以cacheline粒度对齐,cacheline在64bytes对齐存储系统中大小为64bytes;

5.2 Cache state model

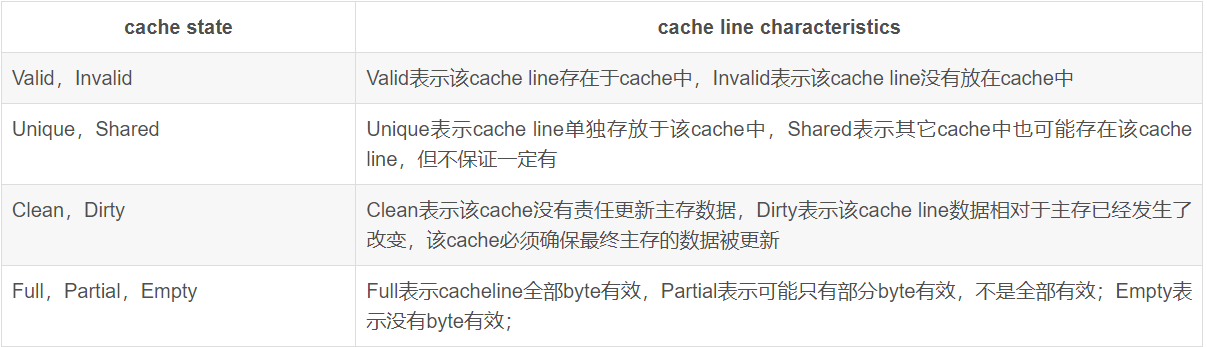

为了使得一个组件在访问cache line时,可以确定是否该执行某操作,CHI协议定义了cache state。每个cache state基于如下的cache line特性:

如下图1-3所示为7种cache state model,注意一个valid的cache state不是Partial或Empty,而是Full。UC、UD、SC和SD全都是Full cache line状态。

具体的状态含义和状态转换将在后文详细介绍。

六、组件名称

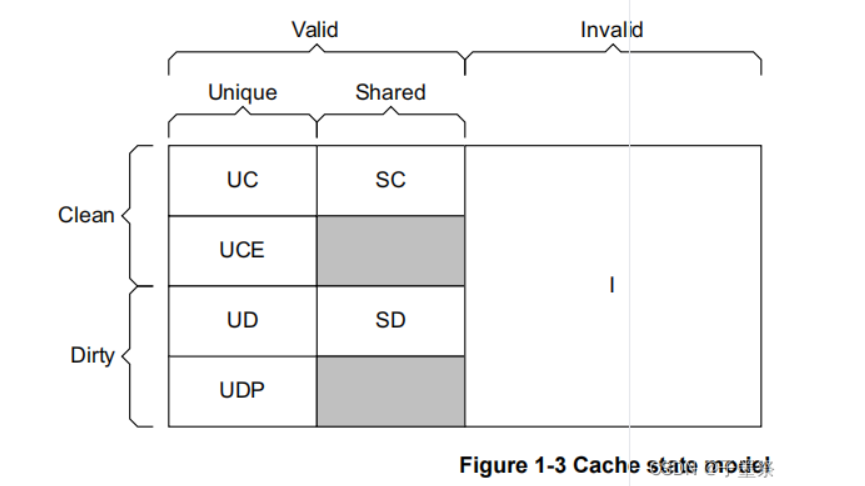

根据CHI协议节点类型,可以将组件分类命名如下:

下图1-4显示了通过互连连接的各种协议节点类型:

七、读数据来源

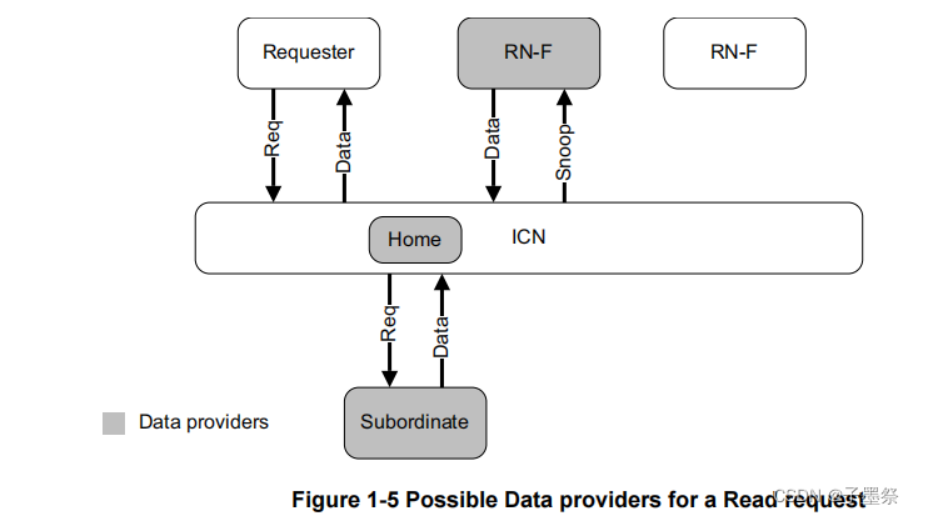

在基于CHI的系统中,读请求的数据可以来自不同的地方,如下图1-5所示,这些源有:

Cache within ICN

Slave Node

Peer RN-F

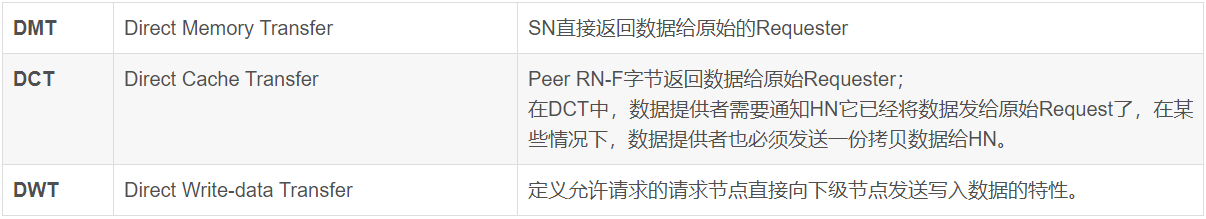

对于RN-F或SN返回的读数据,可以发送给HN,HN再转发数据给原始的Requester;也可以直接跳过HN,返回数据给原始Requester,这样可以减少读数据的latency。这些技术可分类为: