Hey,我们已经通过第一章搭起了硬件安全的框架,在往这个架子上陈列东西之前,我们再加固一下基座:开始正式学习硬件安全之前,我们需要先对SoC硬件有一定认识。

电子硬件概览

- FET:场效应晶体管

- FET是场效应晶体管,它通过控制栅极电压来控制源极和漏极之间的电流,从而实现逻辑功能。

- CMOS:硅基互补金属氧化物半导体晶体管

- CMOS是互补金属氧化物半导体晶体管,它是一种基于硅基材料的半导体器件,具有高速度、低功耗、高集成度等优点。

- 摩尔定律已经失效,正在寻找“超越摩尔”的技术

- 为了超越摩尔定律,人们正在探索新的技术,如三维集成、柔性电子、生物电子等。

一、数字逻辑

数字逻辑是处理数字信号的逻辑,实质上是指基于二进制数学或布尔代数的逻辑。指用数字表示数字电路的信号和序列。

- 1、二进制逻辑:正电压表示为逻辑1、高、真(true);无电压表示为逻辑0、低、假(false)

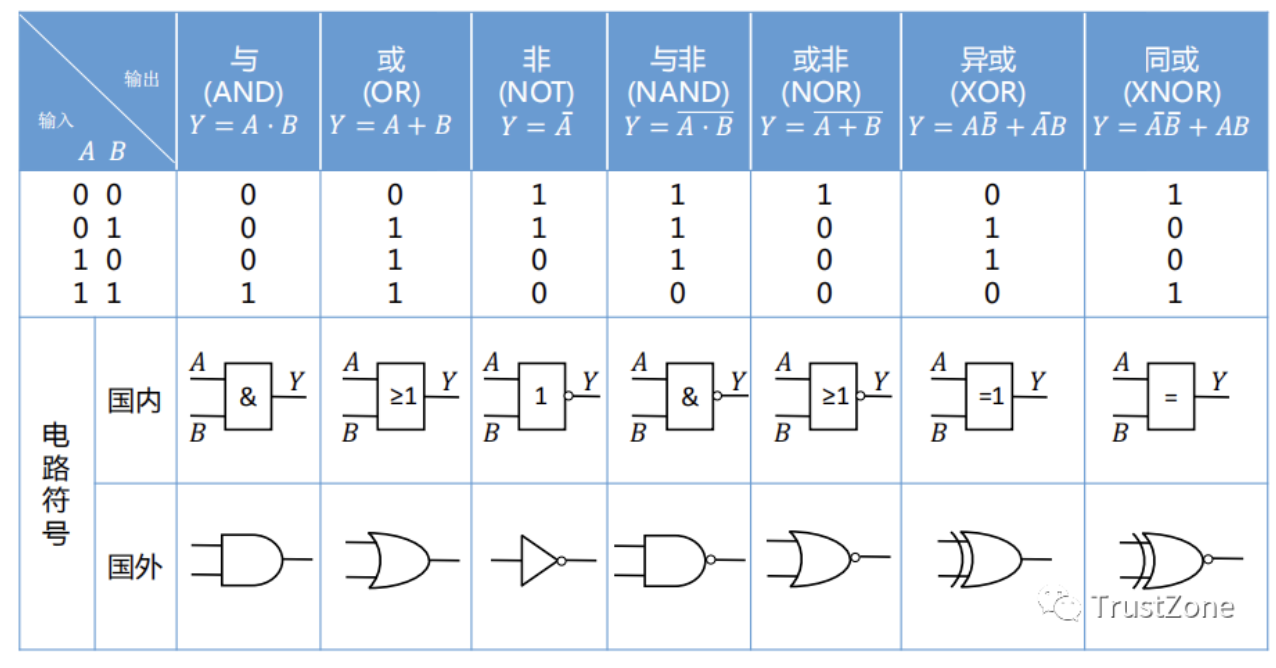

- 2、数字逻辑门:

- 3、时序电路:现代数字逻辑电路分为组合逻辑和顺序逻辑(有存储功能)

- ①时序电路元件:触发器(锁存器),D型、T型(反转)、JK型

- ②计时参数:设置时间、保持时间、传输延迟

学习资料:数电基础:时序逻辑电路[1]

二、ASIC 和 FPGA

- 1、ASIC(Application - Specific Integrated Circuit)专用集成电路

为特定用途制造的集成电路,性能高、功能复杂、功率消耗低、单元较小、单位成本低,但开发周期长、设计流复杂、初始成本高、偶发成本高,在大批量生产上具有优势

- 2、FPGA(Field-Programmable Gate Array)现场可编程门阵列

对已制造完成的芯片进行配置的集成电路,由一组可编程的逻辑块和可重构连接器构成,是现场可编程的。逻辑块可通过重新配置连接器进行连接,配置不同的功能。其灵活、上市时间快、设计简单、可升级而不改变硬件,但功率消耗高、性能中等、单元成本高、资源浪费。在中等批量的生产上具有优势。

还可以用来搭建原型验证平台。

三、印制电路板(PCB - Printed Circuit Board )

- 1、PCB的设计流程:

- 前期准备:这包括准备元件库和原理图。在进行PCB设计之前,首先要准备好原理图SCH的元件库和PCB的元件库。元件库可以用peotel 自带的库,但一般情况下很难找到合适的,最好是自己根据所选器件的标准尺寸资料自己做元件库。原则上先做PCB的元件库,再做SCH的元件库。PCB的元件库要求较高,它直接影响板子的安装;SCH的元件库要求相对比较松,只要注意定义好管脚属性和与PCB元件的对应关系就行。注意标准库中的隐藏管脚。之后就是原理图的设计,做好后就准备开始做PCB设计了。

- PCB结构设计:这一步根据已经确定的电路板尺寸和各项机械定位,在PCB 设计环境下进行设计。

- PCB布局:这主要是指在PCB板上放置元器件的位置。布线:是指根据已经设计的PCB布局,通过具体的连接方式将元器件连接起来。

- 布线优化和丝印:主要是对已经完成的布线进行优化,比如调整走线的角度、长度等,以及添加丝印等。

- 网络和DRC检查和结构检查:这是指对已经完成的PCB设计进行网络检查和结构检查,以确保其满足设计要求。

- 制版:是指将设计好的PCB图纸送到工厂进行制作,制作完成后进行测试和验收。

- 2、PCB生产流程:轮廓、创建铜线路、钻孔、焊上元件、Gerber文件 有点意思:电路板厂之PCB制作工艺过程展示!(动图讲解)[2]

- 基材准备:选择合适的基材,通常是玻璃纤维增强的环氧树脂(FR-4),进行切割和平整处理。

- 表面处理:在基材表面进行清洁、去氧化和化学处理,以增强粘附性能。

- 涂覆铜箔:在基材上涂覆一层铜箔,形成导电层。

- 图形化蚀刻:将Gerber文件的图形信息通过光刻技术转移到涂覆的铜箔上,并使用化学溶液蚀刻掉未受保护的部分。

- 孔位钻孔:根据设计需要,在板上钻孔,形成连接电路和安装孔位。

- 金属化处理:在钻孔后,对板面进行金属化处理,以增强电路连通性。

- 追踪线路:在板上涂覆保护层,并通过蚀刻或化学方法形成所需的导线路径和连接。

- 表面处理:根据要求,在PCB表面进行阻焊涂覆和表面处理,以保护电路和增强焊接性能。

四、嵌入式系统

基于微处理器或微控制器的系统,为特定功能而设计。微控制器是一个整体,包括 CPU。其搭载的软件通常需要工作在内存较少的简单环境中。

五、硬件-固件-软件交互

- 硬件是计算机系统的物理部分,包括中央处理器(CPU)、内存、硬盘、基本输入输出系统(BIOS)等。

- 固件负责在硬件和软件之间建立通信,并管理计算机的基本功能。它通常被存储在只读存储器(ROM)或可编程只读存储器(PROM)中。

- 软件是计算机系统的非物质部分,包括操作系统、编译器和应用程序等。操作系统负责管理计算机的资源,编译器负责将源代码转换为机器代码,而应用程序则为用户提供特定的功能。

在硬件、固件和软件的交互中,固件会与硬件进行通信,将硬件的状态和信息提供给操作系统和编译器。

而操作系统则会根据固件提供的信息,管理硬件资源,并向应用程序提供服务。

编译器则将应用程序的源代码转换为机器代码,以便操作系统能够执行。

计算机固件根据所在设备的不同可以分为多种类型,最常见的有主板固件、显卡固件、鼠标键盘固件等。每一种固件都具有自己独特的功能和操作方式。

固件作为硬件的控制程序,起到了以下几个重要作用:

- 启动系统:固件负责电脑的启动过程,可以加载操作系统,进行初始化设置和硬件自检等操作。

- 管理硬件:固件可以管理电脑硬件的工作状态,包括电源管理、温度监控、风扇转速控制等。

- 支持扩展设备:固件可以支持新设备的接入和识别,保证硬件的兼容性和稳定性。

- 升级与维护:固件可以进行升级和修复,提供新功能和修复已知问题,提高硬件的性能和稳定性。

片上系统的设计与测试

本章讲述 SoC 的设计流程、SoC 测试验证的流程和原理

在设计VLSI(超大规模集成电路)时,会设定一个时序裕度,保证芯片的稳定运行。但IC上的门密度和设计复杂度在不断增加,在纳米尺度的制造工艺下将可能引入更多制造缺陷。因此,验证测试和制造过程的正确性变得越来越重要。

一、基于 IP 的 SoC 生命周期

SoC(system on chip)片上系统 是一个包含给定系统所需所有元件的集成电路,通常包括模拟、数字和混合信号IP核心。

1、SoC的生命周期 :

- 设计阶段:在这个阶段,制定设计规范,随后将所有IP内核集成,并植入DFT结构,生成网表和GDSII格式文件。这个阶段需要经过详细的规划和测试,以确保设计的正确性和性能。

- 制造阶段:在制造阶段,将在晶圆片上进行光刻和化学处理,以制造出芯片。这个阶段需要使用精密的设备和工艺,以生产出高质量的产品。

- 装配阶段:即IC封装,装上外壳,并提供电气连接和散热的热路径,以保护芯片。这个阶段需要使用先进的封装技术,以确保芯片能够正常工作并得到良好的保护。

- 发行阶段:在发行阶段,产品将被分销到各个销售渠道,供消费者购买和使用。这个阶段需要制定市场策略和销售计划,以促进产品的销售和推广。

- 系统集成阶段:在系统集成阶段,与多个器件一同集成为一个系统。这个阶段需要考虑如何将各个功能模块集成在一起,以实现系统的完整性和稳定性。

- 退役阶段:在退役阶段,产品将不再被生产和销售,并逐渐退出市场。这个阶段需要进行产品的清理和回收,以保护环境和资源。

在整个SoC的生命周期中,需要不断地进行优化和改进,以提高产品的性能、降低成本并满足市场需求。同时,也需要不断地更新技术,以保持公司的竞争力和市场地位。

2、SoC的设计流程:

SoC 技术设计系统芯片,一般先要进行软硬件划分,将设计基本分为两部分:芯片硬件设计和软件协同设计。

芯片硬件设计包括:

- ①制订设计规范,并指定一个IP列表实现既定规范。(3PIP的购买:软IP核以HDL交付;硬IP核以GDSII交付;固定IP核使用通用库交付。

- ②将所有IP集成,加入DFT结构,生成RTL描述(完整的系统级数字电路描述)和网表。

- ③门级网表被转换为基于逻辑单元格和I/O几何图形的物理布局

- ④进行测试,测试完毕后,发往代工厂进行制造

二、SoC 的验证测试流程

验证阶段又称硅前验证,即在流片前确保从设计规范到网表的功能正确和正确转换的过程;

测试阶段,是流片后的制造测试和生产测试的过程。

- IP 验证 IP 是任何 SoC 的基本构建块。因此,IP验证需要详尽的白盒验证,这需要形式验证和随机模拟等方法,特别是对于处理器IP,因为一切都是由它们作为任何SoC的核心组件启动和驱动的。下图 显示了我们如何通过基于 SystemVerilog 的 UVM TB 的详尽随机模拟来验证处理器 IP。所有处理器指令都可以使用各种随机值进行模拟,从而生成功能、断言和代码覆盖率。我们使用覆盖范围来衡量验证的进度和质量,然后进行最终的验证签核 IP 级验证要求在 HVL 编程、正式和动态 ABV、仿真调试以及使用 VIP 和 EDA 工具方面具备良好的专业知识。

- ABV- 基于断言的验证,VIP – 验证 IP

- UVM-通用验证方法 UVC-UVM 验证组件

- BFM总线功能模型VIP验证IP RAL寄存器抽象层

- 子系统验证 子系统主要由预验证的IP和一些新建的IP组成,例如特定于芯片的网桥和系统控制器。图 显示了我们如何从子系统构建 SoC,该子系统使用 AMBA 等片上总线集成了所有必要的接口 IP、网桥和系统控制器。在这种情况下,我们更喜欢基于模拟的灰盒验证,特别是使用验证IP的随机模拟。所有VIP,如AXI,AHB,APB,GPIO,UART,SPI和I2C UVC [UVM验证组件]都将配置并与各自的接口连接。如图所示,我们创建了其他 TB 组件,如参考模型、记分板和 UVM RAL,以使验证环境自检。我们在顶层执行各种VIP UVM序列,验证数据流,并测量总线的性能。

- SoC验证 SoC主要由预先验证的第三方IP和一些内部IP组成。通常,我们更喜欢使用硬件仿真或模拟(simulation/emulation)技术进行黑盒验证,以进行SoC级验证。例如,您可能会遇到复杂的 SoC 验证环境,如下图 所示。SoC测试平台[TB]将具有各种测试平台组件,如标准UVM验证IP[USB /蓝牙/WiFi和标准接口],带有UVM包装器的传统HDL TB组件[JTAG Agent],自定义UVM代理[固件代理],以及一些显示器,以及记分牌和SystemC / C / C++功能模型。在这种情况下,您将不得不在芯片级别处理固件和UVM序列。作为验证工程师,您需要知道如何使用标准 VIP、传统 HDL BVM 和固件代码实现这种混合验证环境,更重要的是,了解如何使用 EDA 工具自动执行simulation/emulation。

深入一下:SoC Verification Flow and Methodologies[3]

1、SoC的验证流程

- ①对IP进行单独验证。

- ②基于接口协议,对芯片中各块接口进行验证

- ③系统级验证,通过仿真软件进行硬件和软件的验证。分别进行功能验证和结构验证。

- ④对IC的物理布局进行验证。验证完成。

2、SoC的测试流程

- ①晶圆测试,为晶圆提供电气刺激进行测试

- ②识别制造缺陷或故障,使用自动测试模式生成工具ATPG

- ③对芯片进行表征,找出芯片的理想工作参数

- ④功能测试和结构测试

- ⑤封装模具的老化应力测试

三、调试性设计

SoC调试,即硅后验证,在第一个硅制造后进行。调试支持由芯片上的调试性设计架构和软件组成。其策略是将接入点放置在系统中,由它的接口获得和控制芯片内部信号。

电子系统中有三种元件需要测试:数字逻辑、内存块、模拟或混合信号电路。制造测试成本主要取决于测试数据的数量和测试时间

ATPG 扫描测试(又叫ATPG)。scan path。与边界扫描测试的区别,是内部移位寄存器实现的测试数据输入输出。测试目标是std-logic,即标准单元库。(扫描测试和边界扫描,不是一个概念。需要区别对待。内部的触发器,全部要使用带SCAN功能的触发器类型。)

Boundary scan Boundary scan:边界扫描测试;boundary scan test。测试目标是IO-PAD,利用jtag接口互连以方便测试。(jtag接口,实现不同芯片之间的互连。这样可以形成整个系统的可测试性设计。)

Lbist Lbist:LBIST 是一种内置自测 (BIST) 形式,其中芯片内部的逻辑可以在芯片本身上进行测试,而无需任何昂贵的自动测试设备 (ATE)。BIST 引擎内置于芯片内部,只需要像测试访问端口 (TAP) 这样的访问机制即可启动。Lbist的组成部分 片上lbist一般由三部分组成:BIST controller、TPG (Test Pattern Generator)、RA (Response Analyzer)。

mbist mbist:内建自测试BIST;(模拟IP的关键功能,可以开发BIST设计。一般情况,BIST造成系统复杂度大大增加。memory IP一般自带BIST,简称MBIST)

loading board loading board:LOAD BOARD通常用于测试半导体器件的电气特性,例如电流、电压、功率等。它是连接测试设备和被测试芯片的桥梁,通常包括一些接口,例如引脚插座、测试点和电源接口等。LOAD BOARD的设计必须与被测试器件的引脚布局相匹配,以确保测试结果的准确性和可重复性。

BURN IN BOARD BURN IN BOARD则用于加速半导体器件的老化过程,以检测器件在长期使用中的可靠性。它通常包括一个温度控制系统,用于控制被测试器件的环境温度。BURN IN BOARD还可以模拟真实世界的使用条件,例如高温、低温、高压和高湿等。因此,LOAD BOARD和BURN IN BOARD的主要区别在于它们的用途。LOAD BOARD主要用于测试器件的电气特性,而BURN IN BOARD则用于测试器件在长期使用中的可靠性。

深入一下:DFT学习(一):DFT概述和ATE概述:DFT概述和ATE概述

")

1、DFT调试技术概览

- ①扫描:对所有在扫描设计中的存储元件进行访问和控制。

- ②扫描触发器(SFF):性能开销低,但速度慢

- ③扫描链:将扫描触发器连成一串,然后将扫描值与SO值(扫描输出值)进行比较

- ④扫描测试压缩:利用少量的测试的重要值来减少测试数据和测试时间

- ⑤边界扫描:边界扫描技术利用边界扫描链,在芯片内部的信号线上插入测试信号,从而实现对芯片内部电路的测试和诊断。有效降低了PCB制造成本。

2、全速延迟测试

用于检测计时相关故障的方法

- ①故障类型:转换故障(慢升和慢降造成的延迟),路径延迟故障(路径上的累计延迟)

- ②两种方法:LOS和LOC

印制电路板 :设计与测试

本章讲述 PCB 的历史、生命周期、设计验证、装配流程

印制电路板PCB是基于基地结构的非导电板,为电路电气元件提供电气连接和机械支撑。

一、PCB 的历史

在PCB量产前,通常使用点对点的飞线连接;

早期PCB是在电路板材料上钻孔,并在孔中植入黄铜。

20世纪20年代,PCB诞生,申请了第一个专利;

20世纪30年代到40年代,PCB在二战中得到广泛运用;

20世纪50年代,发明了酸刻蚀铜金属电路板的方法;

20世纪80年代,表面贴装技术(Surface Mount Technology,SMT)的发展在1980年代引入了新的PCB制造和组装方法;

现代,三维PCB、柔性PCB。

二、PCB 的生命周期

PCB的生命周期与SoC的生命周期类似

设计规范->PCB设计->PCB原理图->PCB布局->制造和装配->检测验证

三、PCB 的设计验证

恶意攻击者可以利用当今复炸而高度集成的PCB设计,借助隐藏孔或无源嵌入式元件,以硬件木马的形式篡改或植入额外的恶意电路,目前行业并无有效的安全措施来防御。

1、PCB检查

- ①自动光学检查(AOI):多次拍照,拼接成一个完整的大图像,与设计图进行比对。

- ②自动X射线检查:利用不同材料对X射线的吸收率不同,对PCB进行检查

2、PCB测试

- ①芯片内测试:万用表原理

- ②功能测试

- ③JTAG边界扫描测试

小结

到这里我们就对电子硬件、片上系统、PCB都有了一定认识。学习硬件安全的前提是我们得了解硬件,了解它的设计、测试、生产,才能指导在哪里会面临安全风险,以及才有什么样的手段去增加硬件的安全性。

下一篇就开起我们的硬件安全学习!

那么下次见!

引用链接

[1] 数电基础:时序逻辑电路[2] 电路板厂之PCB制作工艺过程展示!(动图讲解)[3] SoC Verification Flow and Methodologies

作者:Hcoco

文章来源:TrustZone

推荐阅读

更多物联网安全,PSA等技术干货请关注平台安全架构(PSA)专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入PSA技术交流群,请备注研究方向。