在进行模块设计时,我们经常需要统计报文的数量,以供软件(or 主机)读取,有些统计仅仅用于debug,有些统计是协议要求,有些统计是为了便于功能实现。

当需要统计的数量较多时,为了降低功耗和减少面积,我们通常采用RAM去实现。

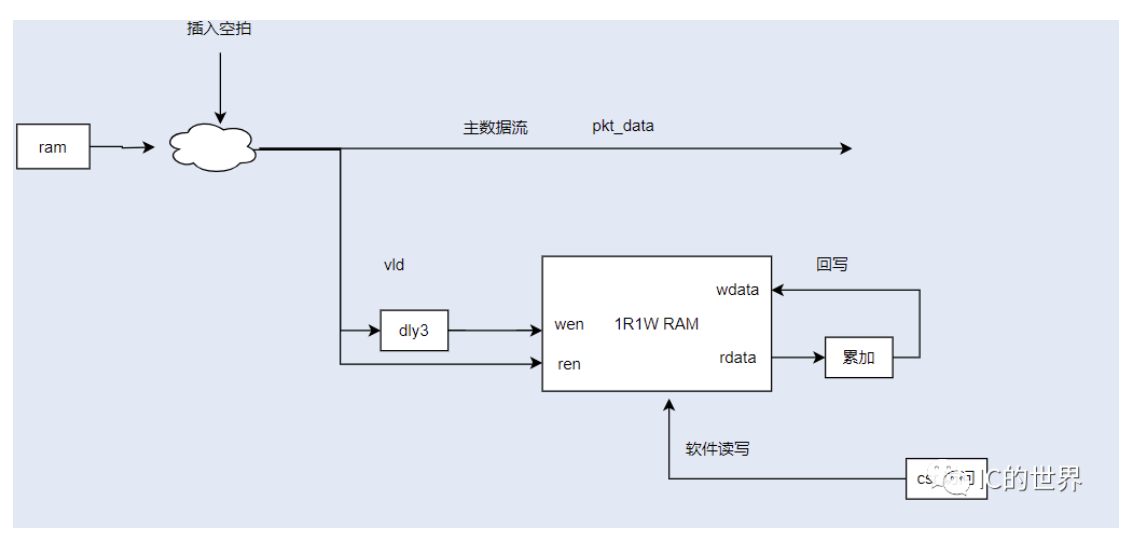

如下案例中,统计有效数据包的个数。

假设数据中存在pkt_id,pkt_id为0~63,则ram的深度为64。pkt_id用于作为读写地址。RAM读延时为3个时钟周期。

有数据来临时,pkt_vld作为读使能,读出当前包计数rdata,三个周期后,rdata加1回写到ram。

如下图所示:需要有三个注意事项

NOTE1:需要有读写保护,因为可能出现连续4个周期内,pkt_vld为1,且pkt_id相同,此时会出现同一个周期对相同的地址进行读写,因此需要RAM需要添加读写保护模块,保证数据能够正确写入,且读出的都是最新值,否则就会出现统计错误。

NOTE2:图中既有软件读、又存在硬件读,且硬件读优先级更高,软件读优先级低,因此为了保证软件读能够在有效周期内得到响应,因此需要在主数据流上插入空拍,避免出现软件读长时间无法响应而产生超时。

作者:IC小鸽

文章来源:IC的世界

推荐阅读

- DDR与PCIe:高性能SoC的双引擎

- 计算机的物理结构

- 用生成式AI设计芯片,实例2:解读时序图

- 用生成式AI设计芯片,实例1:从有限状态机图片直接生成SV代码

- 后端设计PG liberty的作用和增量式生成

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。