NIC NOC CCI CMN CNN NI cmn-700 nic-700 ni-700 MLGB这都是啥玩意?后期博文或视频将会更新这一系列。今天先温习一下CNN的概念,这是来自2014年的文章,然后稍微整理总结一番。

以下是正文....

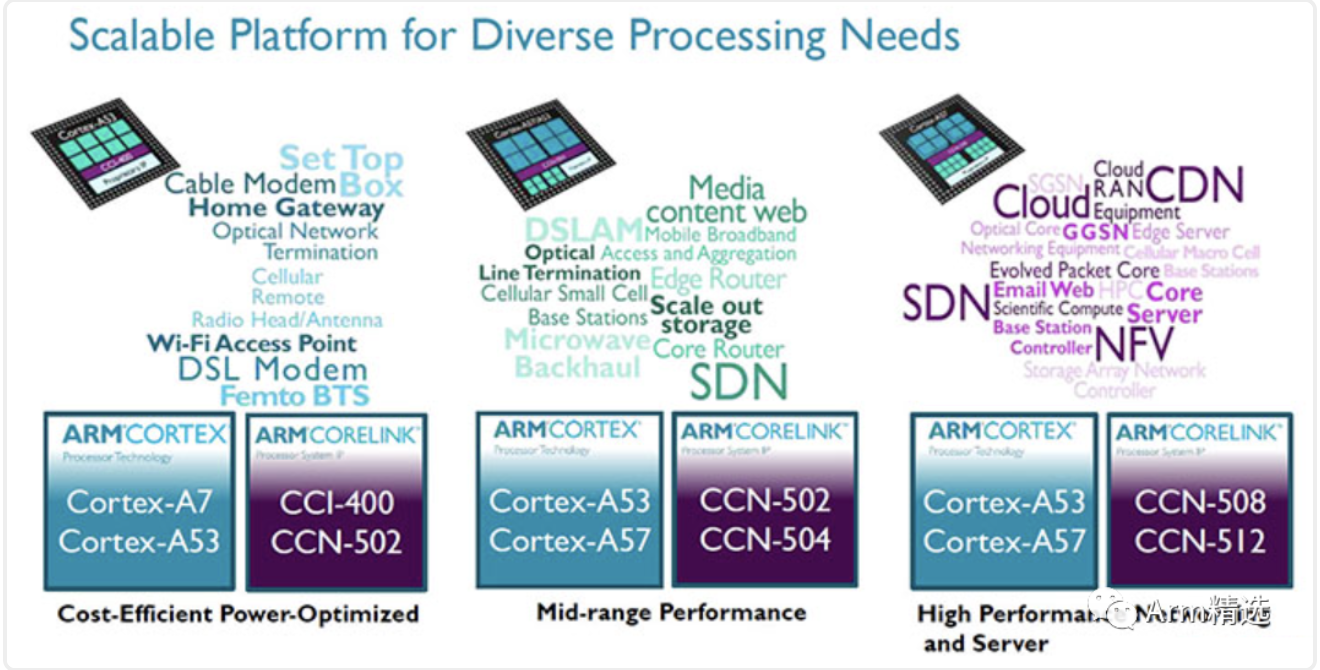

现代主流和优质 ARM 片上系统 (SoC) 产品使用 CoreLink 缓存一致性网络 (CCN) 504 或最近的 508 互连。它们提供对 L3 缓存的访问、用于 I/O 一致性加速器的多个接口以及对 DDR3 或 DDR4 内存的访问,从而将 CPU 与芯片的其余部分联系起来。

作为 SoC 的粘合剂,CCN-504 支持多达 4 个处理器集群(16 个内核)、16MB 的 L3 缓存和 18 个 I/O 接口。与此同时,以数据中心为中心的 CCN-508 将其增加到潜在的 8 个集群和 32 个核心、32MB 的 L3 缓存和 24 个 I/O 接口。

ARM 今天推出了两种新的 CCN 模型,为合作伙伴提供了更多关于 SoC 互连的选择。CCN-502 是一款成本较低、尺寸较小的互连产品,适用于 WiFi 接入点、边缘路由器和基站等产品。与此同时,CCN-512 通过为更多 CPU 内核提供连接来扩展数据中心和 HPC 范围。

(CCN-512)

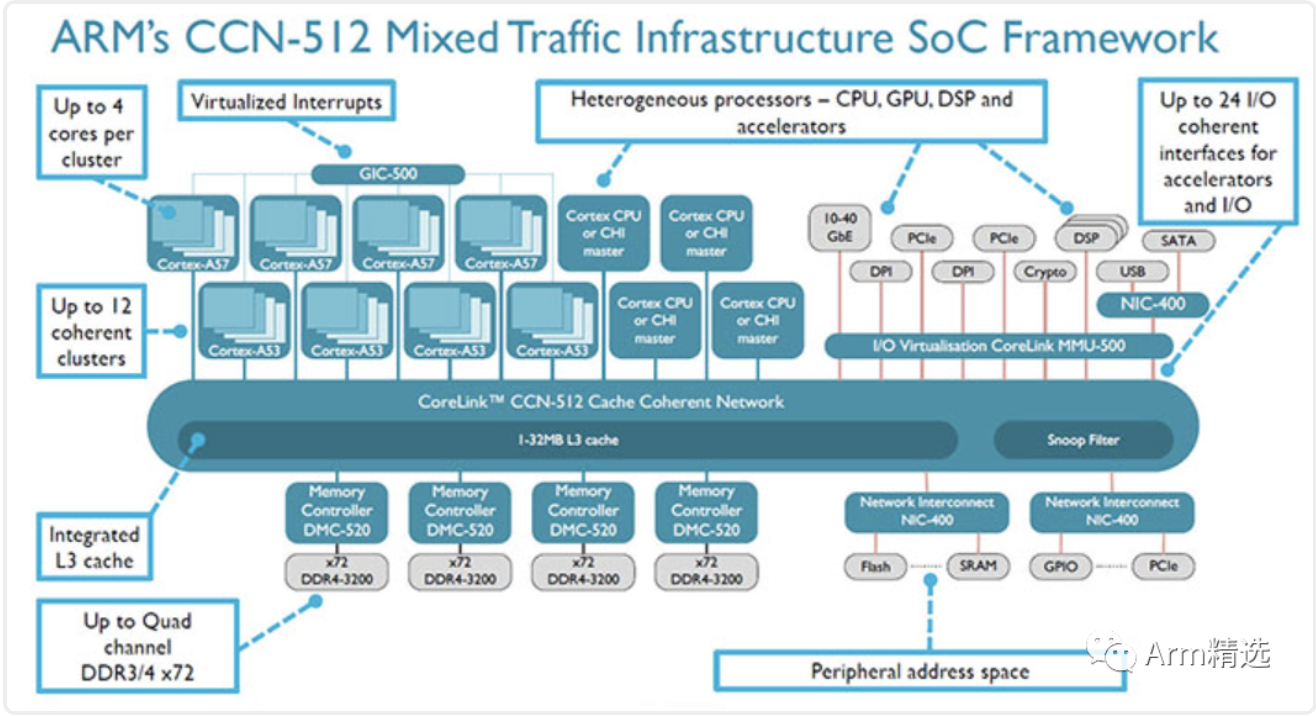

CCN-512互连的拓扑遵循CCN-508所采用的蓝图。ARM 旨在支持数据中心类型环境中的处理器密集型 SoC,现在提供了一种将 CCN-508 的 8 个相干 CPU 集群扩展到该型号上的 12 个,或从最多 32 个内核扩展到 48 个的方法。当然,合作伙伴需要设计此类 SoC - ARM 提供构建模块所需的 IP。

通常,此类目标明确且性能丰富的 SoC 的设计人员倾向于构建自己的互连结构 - 例如,Cavium 就在 ThunderX 产品上实现了48 核支持技术。ARM 凭借 CCN-512 使希望在该领域竞争的合作伙伴能够更快地进入市场,因为他们不需要自行设计和验证。

ARM 意识到,并非所有合作伙伴都需要在密集封装的 SoC 中提供 48 个 Cortex A 系列内核。这就是为什么四个附加集群可以是 Cortex A 系列处理器或连接到专用数字信号处理器、通用处理器或图形的相干集线器接口 (CHI)。请注意,这 12 个集群的处理器可以来自 Cortex-A57 或 Cortex-A53 系列,但两组内核不能在一个集群中共存。

CCN-512 与 CCN-508 的 24 个 I/O 一致加速器接口相匹配,并且还使用相同的四通道 DMC-520 内存控制器。不过,这一次官方支持的速度已提高至每通道 DDR4-3200。计算数据表明 CCN-512 的可用带宽超过 100GB/s。ARM 表示,由于有如此多的处理器内核以及可能存在的大量 I/O 互连,峰值内部带宽速度为 1.8TB/s。

如果您考虑基于 ARM 的 SoC 可能如何在企业领域(其中密集计算和大量 I/O 最为重要)进行开发,那么拥有高带宽互连是必须的。CCN-512 扩展了 CCN-508 的工作。梳理出这样的互连可能意味着 ARM 在某个时候会遇到与带宽相关的问题,但该公司表示,它正在研究未来在单个芯片上相互连接的 CCN 结构。

(CCN-502)

目前可用的 ARM CoreLink CCN-504系统 IP 用于多种用途的多集群 SoC,但对于更基本的芯片来说,它在能源和占用空间方面都被认为是过度杀伤力。为了满足明显的需求,CCN-502 经过重新设计,可提供大部分功能,但面积和能源成本显着降低。

ARM 保持了与 CCN-502 高达 16 核 CPU 的兼容性,但将 I/O 接口的数量减少了一半,达到 9 个,也许对于面积和功耗来说最重要的是,能够完全删除 L3 缓存。考虑到这些潜在的节省,具有 1MB L3 缓存的实现比完整的 CCN-508 小 70%(并且更节能)。

ARM 热衷于指出,这不仅仅是 CCN-504 的缩小版本。相反,它是专门为不同的细分市场而设计的。这种新互连的推出为更尖端的基于 ARM 的 SoC 铺平了道路,并为增加授权数量提供了途径。

总结:CCN看起来像是一个中间产品、过渡产品。介于CCI/CMN之间的过渡产品。CCI最大的缺点就是无法支持更多的CPU和GPU。环状网络CNN是一个过渡方案,而网状网络CMN是一个较为成熟的设计。

作者:baron

文章来源:Arm精选

推荐阅读

欢迎关注ARM精选专栏, 欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。