引言

在同步电路设计中,时序是一个非常重要的因素,它决定了电路能否以预期的时钟速率运行。为了验证电路的时序性能,我们需要进行静态时序分析,即在最坏情况下检查所有可能的时序违规路径,而不需要测试向量和动态仿真。本文将介绍静态时序分析的基本概念和方法,包括时序约束,时序路径,时序裕量,setup检查和hold检查等。

时序路径

同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最坏情况下满足时序要求,我们需要进行静态时序分析,即不依赖于测试向量和动态仿真,而只根据每个逻辑门的最大延迟来检查所有可能的时序违规路径。

时序,面积和功耗是综合和物理实现的主要驱动因素。芯片EDA工具的目标是在最短的运行时间内,用最小的面积和功耗,生成满足时序网表,并进行布局和布线。EDA工具会根据设计者给定的约束条件,在时序,面积,功耗和EDA工具运行时间之间做出权衡。

芯片要想以期望的时钟频率运行,就必须遵守时序约束,因此时序是最重要的设计约束。静态时序分析的核心问题是:

“在所有情况下(multi-mode multi-corner),每个同步设备(synchronous device,例如触发器)的数据输入端,在时钟边沿到达时,是否已经有正确的数据?”

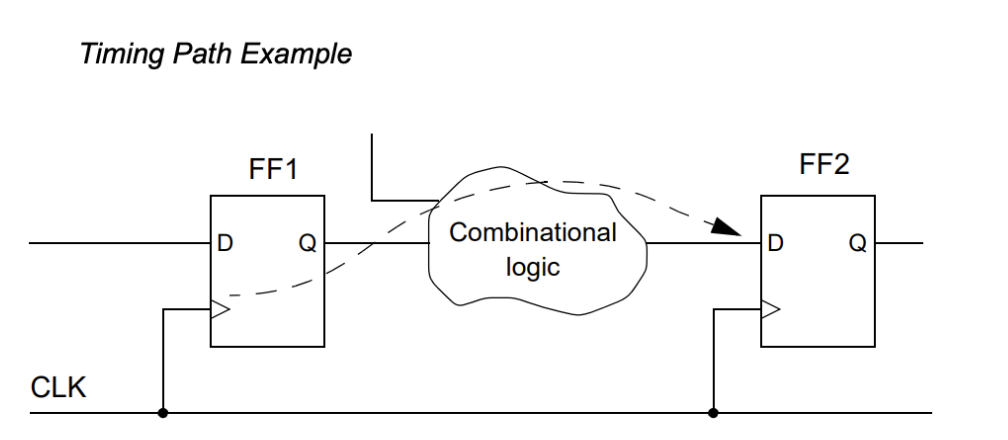

上图中的虚线箭头代表了时序路径。为了保证数据能被准确地锁存,数据信号必须在时钟边沿到达触发器FF2的时钟端之前,传递到触发器FF2的数据端。

setup检查

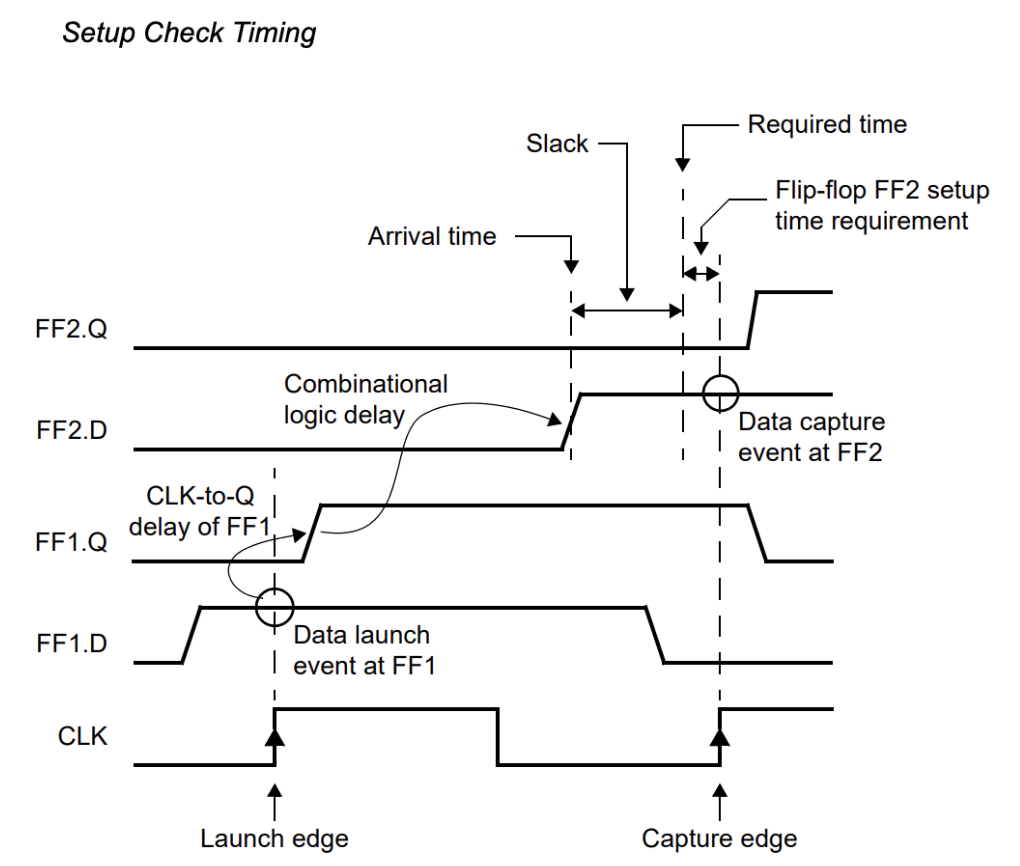

上图展示了这条时序路径的时序情况。当时钟边沿到达FF1时,FF1会锁存FF1.D的数据。经过触发器的CLK-to-Q延迟后,数据会出现在触发器的输出端FF1.Q。这个过程叫做时序路径的launch event。

然后,数据信号经过一定的延迟,通过组合逻辑,到达触发器FF2的输入端FF2.D。数据信号到达这里的时间叫做路径的arrival time。

为了让FF2能正确地锁存数据,FF2.D的值必须在时钟边沿到达FF2的时钟端之前稳定下来,并且提前一定的时间,即触发器的建立时间。这个最小的允许时间叫做路径的required time。FF2锁存数据的过程叫做时序路径的capture event。

时序裕量

时序路径是否满足时序约束,取决于它的时间裕量,即slack。

- 如果数据信号比必要的时间早到达,那么slack就是正值。

- 如果数据信号刚好在required time到达,那么slack就是零。

- 如果数据信号比required time晚到达,那么slack就是负值。

在任何情况下,slack都等于required time减去arrival time。

上面描述的时序检查叫做setup检查,它用来验证数据是否能在每个时钟边沿之前及时到达时序电路。这是综合和时序优化中最常见的一种时序检查类型。

hold检查

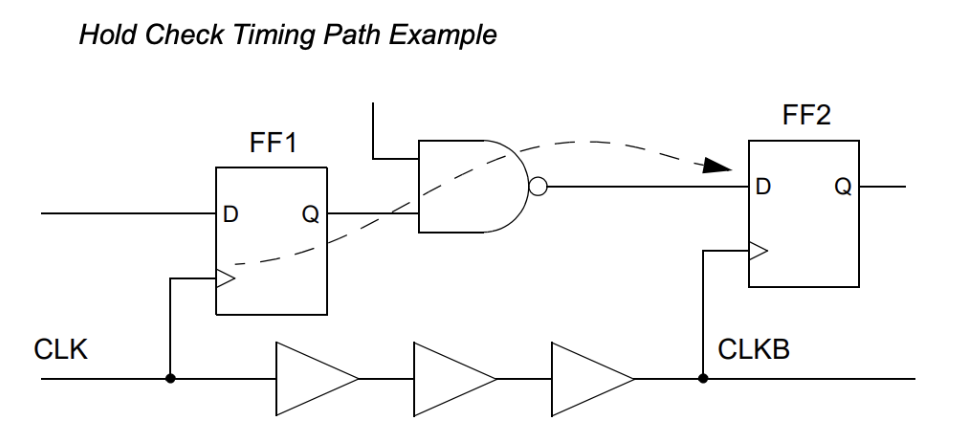

hold检查用来验证数据在时钟边沿到达后,还能保持多久的有效性。如果从launch到capture的数据路径上的组合延迟太短,而从launch到capture的时钟路径上的延迟太长,就有可能出现hold违规。下图给出了这种情况的例子。

上图中,数据从FF1到FF2的时序路径只经过了一个NAND门,组合延迟非常短。而时钟信号从时钟源到FF2的路径上有三个缓冲器,延迟非常长。

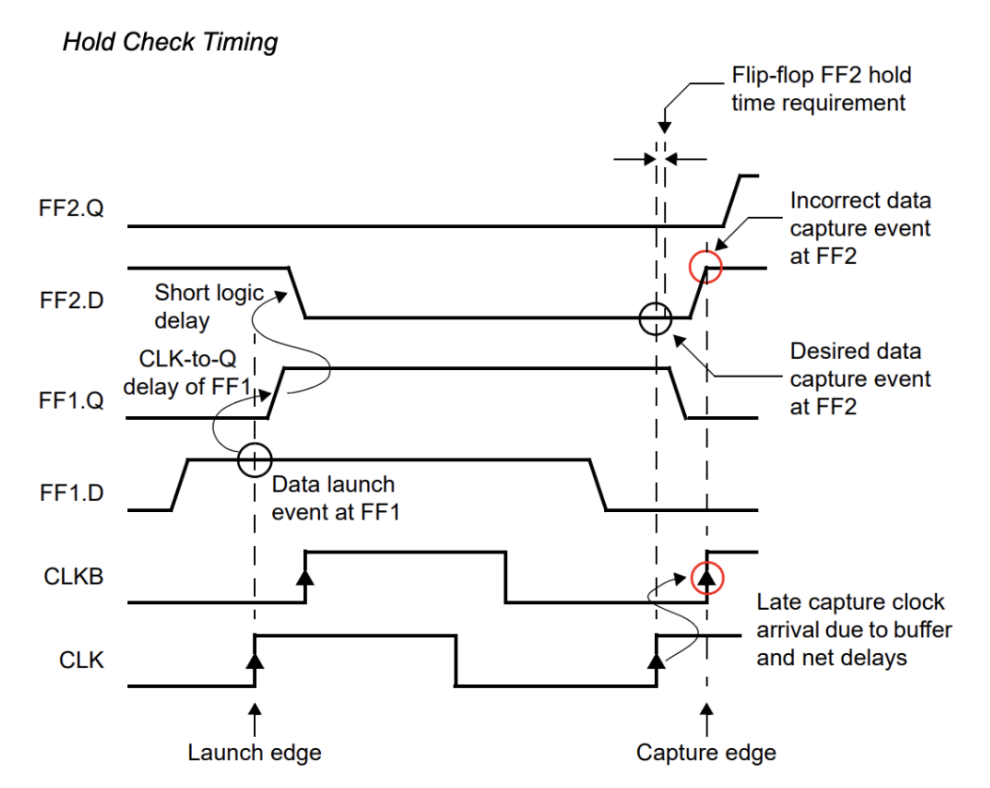

上图显示了这种情况下的可能时序。由于数据在setup time之前到达,所以很容易满足setup约束。然而,问题在于FF2的D输入端的数据不能保持足够长的时间,导致hold约束不能满足。也就是说,数据在时钟CLKB锁存之前发生变化。

为了修复这种类型的违规,我们可以通过缩短时钟线的延迟或增加数据路径的延迟来调整时序。

最坏情况(worst-case conditions)

每种类型的时序检查都考虑了不同的最坏情况(worst-case conditions)。例如,一个setup检查(验证数据是否在时钟边沿之前到达)考虑最长的组合逻辑/最慢的数据路径,以及最早的时钟路径。相反,hold检查(验证数据是否在时钟边沿之后保持有效的时间)考虑最短/最快的数据路径,以及最晚的时钟路径。

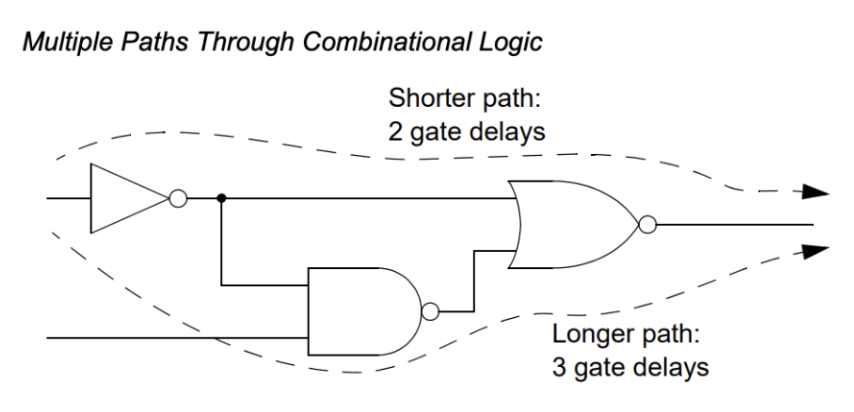

上图显示了通过同一个模块不同组合逻辑路径的示例。在数据路径中,setup检查会考虑较长的延迟(通过三个门),而hold检查将考虑较短的路径(通过两个门)。

配图来源

《Synopsys® Timing Constraints and Optimization User Guide 》

作者:数字芯片

文章来源:数字芯片实验室

推荐阅读

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。