在IC设计中,我们有时会使用深度很大,位宽很小的ram。例如深度为1024,位宽为4bit的ram。此类的ram有个明显的缺点:形状狭长,不利于布局布线、导致读写接口走线过长,不利于时序收敛。

此时为了方便布局布线和时序收敛,我们通常会进行折叠设计。

如下图所示,深度为1024,位宽为4bit的双端口1r1w的ram,有一个读接口,一个写接口,支持同时读写操作,出于以上考虑,我们会进行折叠设计,采用2个128x32的1r1w的ram实现。如图所示:两个2个128x32存储的内容完全一致。

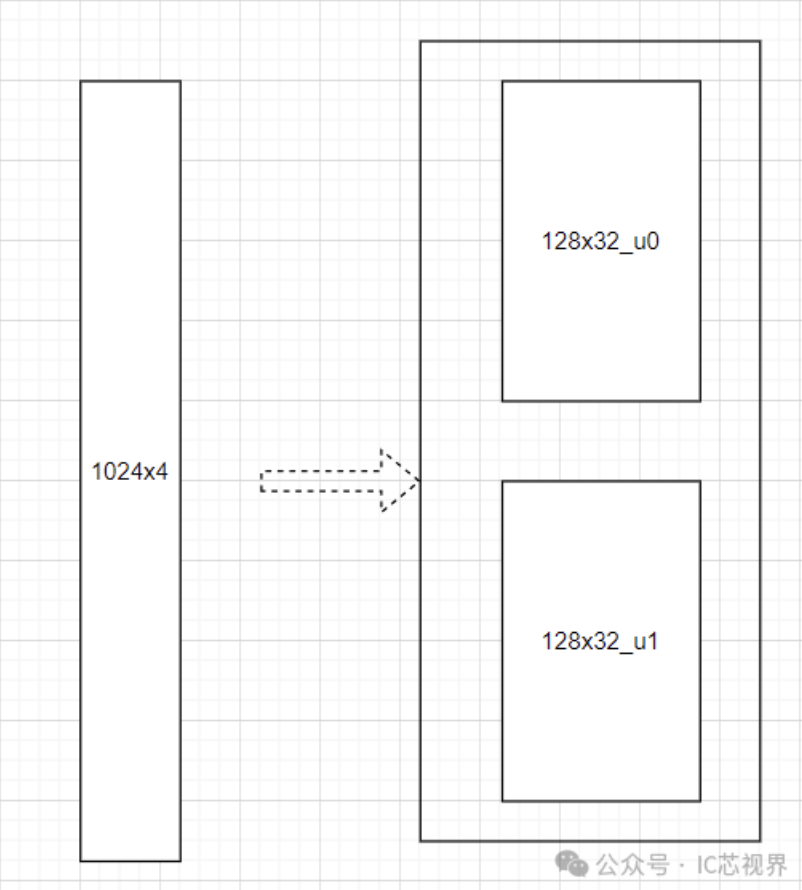

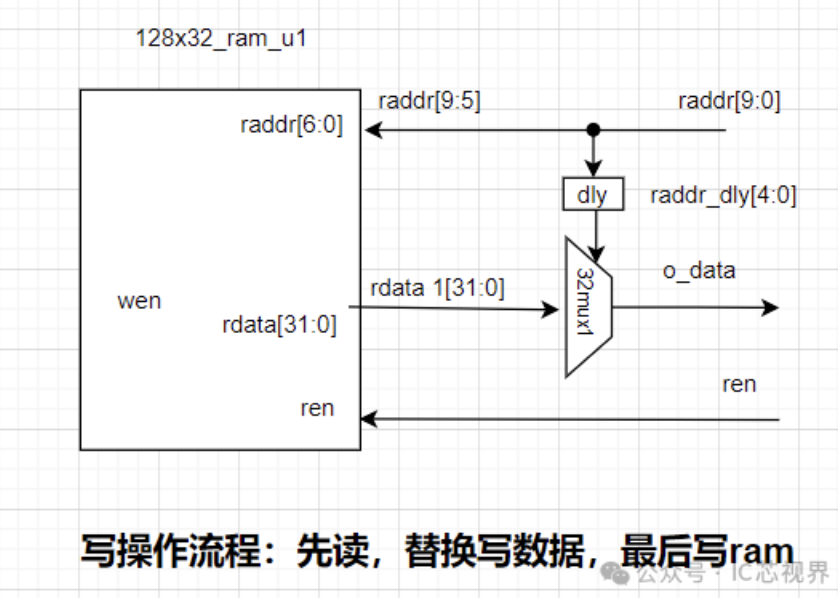

无论是否进行折叠设计,ram接口信号位宽均一致。读写地址位宽为10bit,读写数据位宽为4bit。部分ram读写接口信号如下

进行写操作时:

使用waddr[9:5] 作为读地址,读128x32_ram_u0,获得rdata[31:0]

使用waddr[4:0] 选择rdata[31:0]中一个bit,使用wdata[0:0]进行替换,得到写入数据wdata_inter[31:0]

使用waddr_dly[9:5] 作为写地址,将wdata_inter[31:0]作为写数据同时写入128x32_ram_u0和128x32_ram_u1。

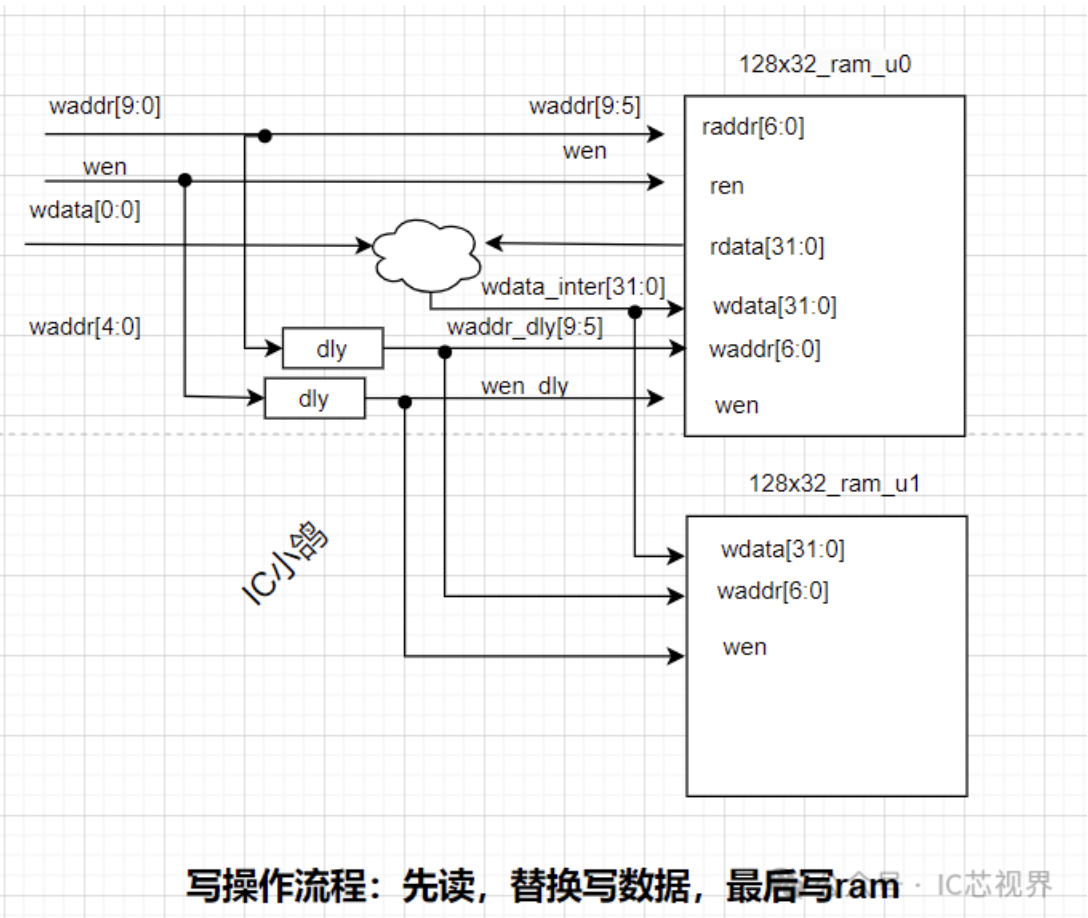

进行读操作时:

使用raddr[9:5] 作为读地址,读128x32_ram_u1,获得rdata1[31:0]

使用raddr[4:0] 选择rdata1[31:0]中一个bit,赋值给o_rdata。

为什么需要用两个128x32的ram?

因为1024x1_1r1w_ram_wrapper需要同时支持读写操作,而在折叠设计中,写操作需要先读ram,读操作也需要读ram,如果仅仅使用1个128x32的ram,就会出现有两个读请求同时产生,因此为了避免出现此冲突,需要2个128x32的ram才能实现。

作者:IC小鸽

文章来源:IC芯视界

推荐阅读

- PCIE定位:PCIe需要的debug设计

- 工作6年半,模拟IC心得感悟(网友分享)

- 2024年真正有实力的IC公司们要发力了!

- 2023年,作为IC工程师的你有哪些高光时刻?

- 干货!还不知道怎么用emac 实现Verilog自动连线?

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。