上周我分享了一份白皮书《基于Chiplet的商业分析-系统与技术》,其实是因为接下来还想发更多的资料。

Chiplet Summit会议资料 (2024&2023)网盘下载

链接:https://pan.baidu.com/s/1y2OCoB2eCSPgW1t0NWCXoQ?pwd=rmix

提取码:rmix

为什么把去年的资料也列在这里?是因为一年前我在《Chiplet Summit_会议资料分享》里发的其实不全。

以今年的会议资料为例,https://chipletsummit.com/ 上能下载到大部分,而OCP网站上还有一些(https://www.opencompute.org/events/past-events/ocp-sponsored-chiplet-summit-tutorial-building-the-chiplet-economy)。

下面挑一些还不错的ppt页面,简单写一点我的解读。

服务器和PC是Chiplet主要市场、HBM内存的推动

上图是以AMD Ryzen作为PC芯片的代表,列了下Chiplet制造流程中的分工。首先,I/O Die、CPU和缓存内存(3D V-Cache)都是由AMD设计;然后到Front-End制造阶段,I/O Die由于制程要求不高在GF生产,CPU和3D V-Cache都是在TSMC台积电做;I/O Die的Back End 0是在马来西亚的TF-AMD完成,而CPU和3D V-Cache的Hybrid Bonding还是在TSMC;最后的CPU成品封测是在马来西亚。

服务器芯片先拿AMD的MI210举例,半导体工艺是TSMC的6nm FinFET。主要可以看下GPU处理器Die与HBM内存之间带有TSV的连接。

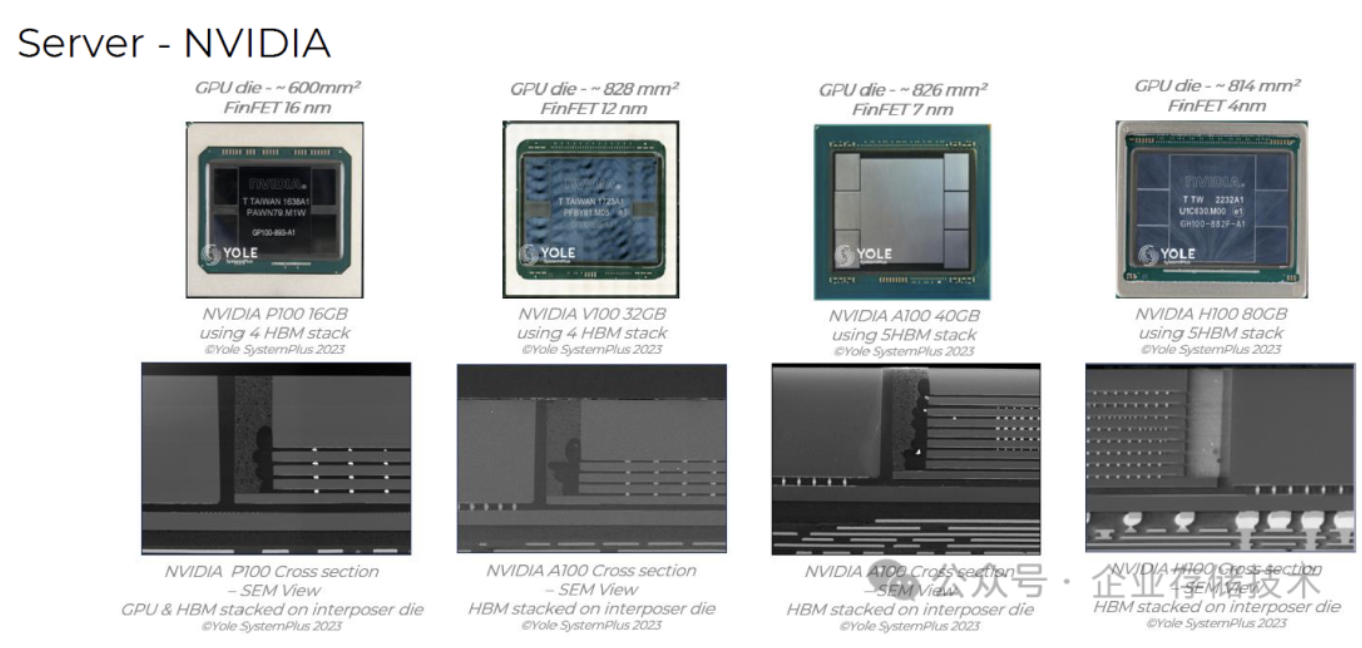

NVIDIA的4代顶级GPU,P100、V100、A100和H100分别采用16nm、12nm、7nm和4nm工艺,它们也都使用了HBM内存(从4片到5片)。

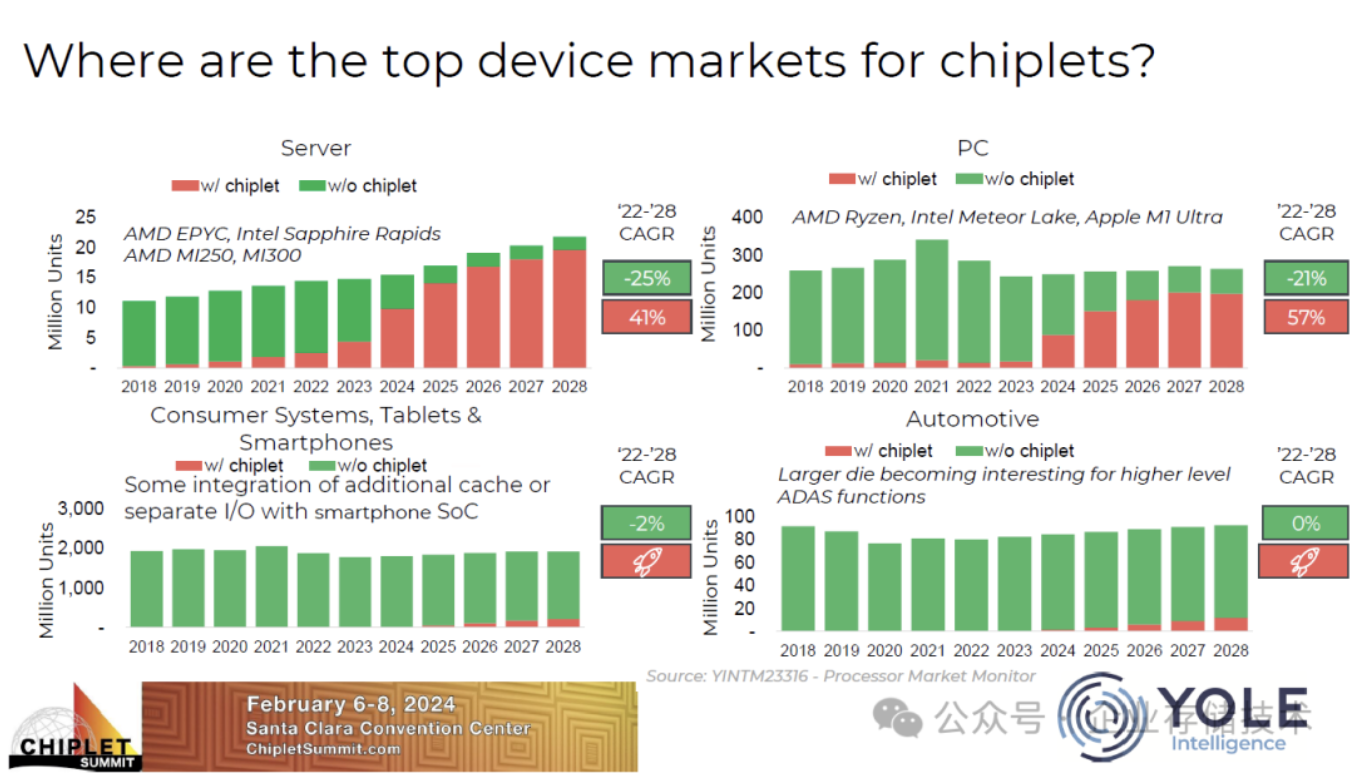

参考上图,Chiplet最大的市场应该是在Server,PC也还不错,而智能手机和自动驾驶领域到2028年渗透率预测也不高。我感觉后两者对芯片整体的面积要求较高,大家想想手机里寸土寸金的密度,能集成度更高显然更好。Automotive对功耗的限制也是较高的。

反而越是大型、复杂的,功耗不断提高的芯片,像服务器CPU和GPU,越喜欢Chiplet。具体好处除了我在前一篇分享中列出的之外,Winnie Shao博士的大作《多Die封装:Chiplet小芯片的研究报告》写得更好。

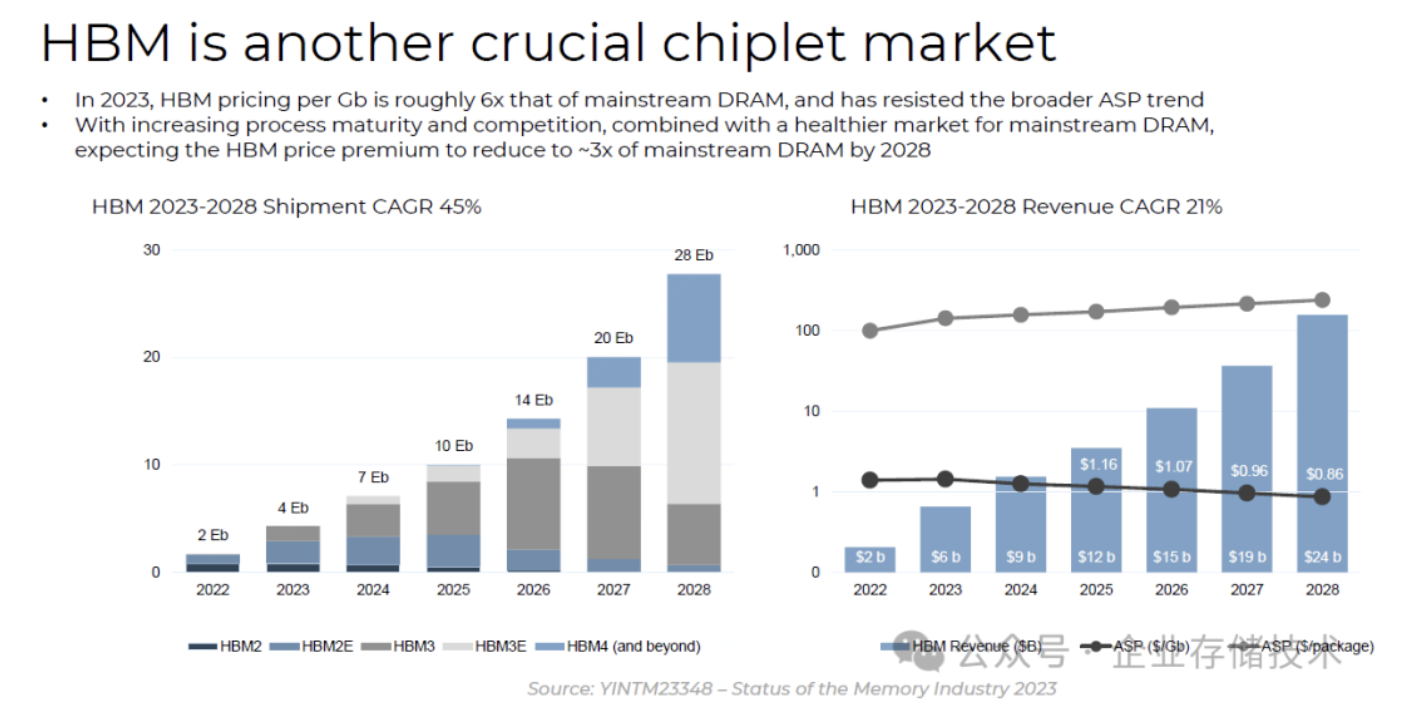

HBM是另一个重要的Chiplet市场。上图中有出货容量和销售额的预测,大致做个参考吧。

从MI300看3-10年后的GPU芯片规模

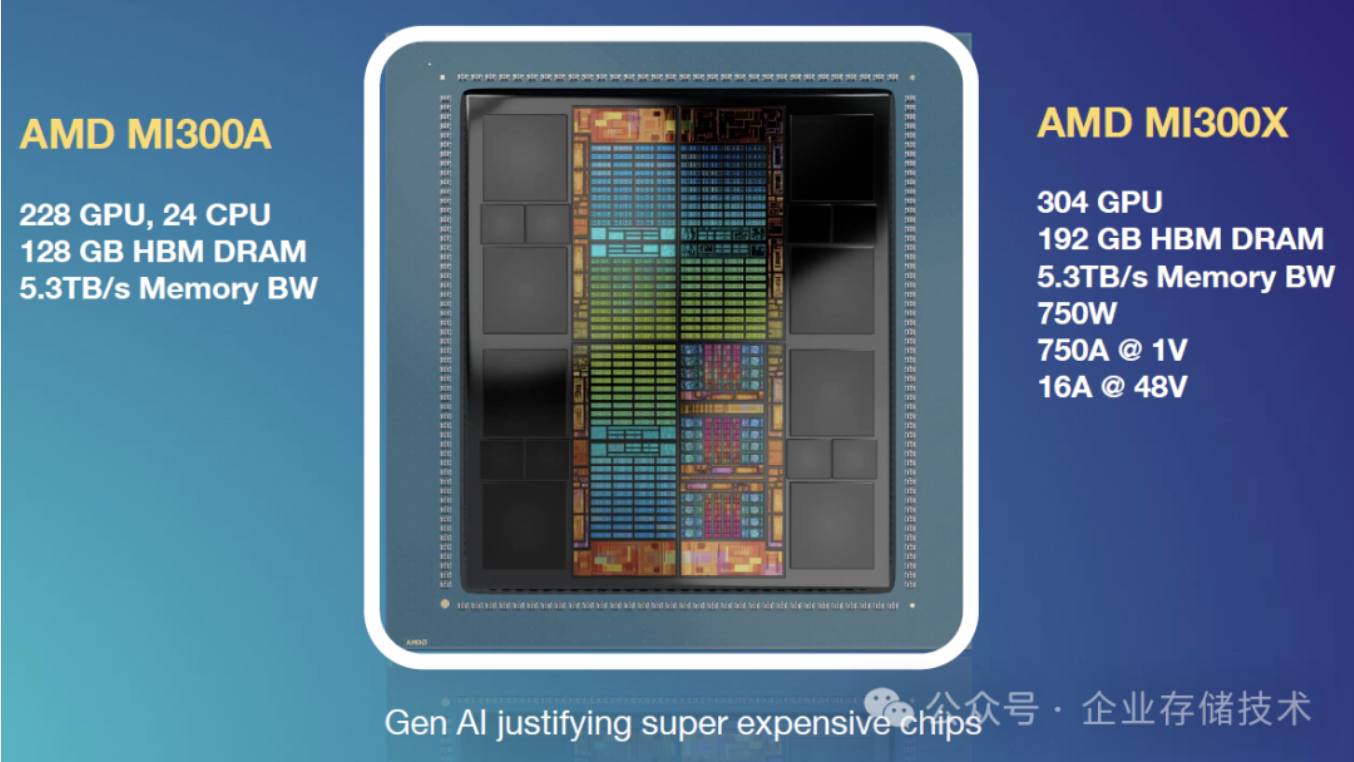

AMD这一代通用计算芯片分为MI300X(纯GPU)和MI300A(GPU+CPU的单芯片UMA架构)两款。

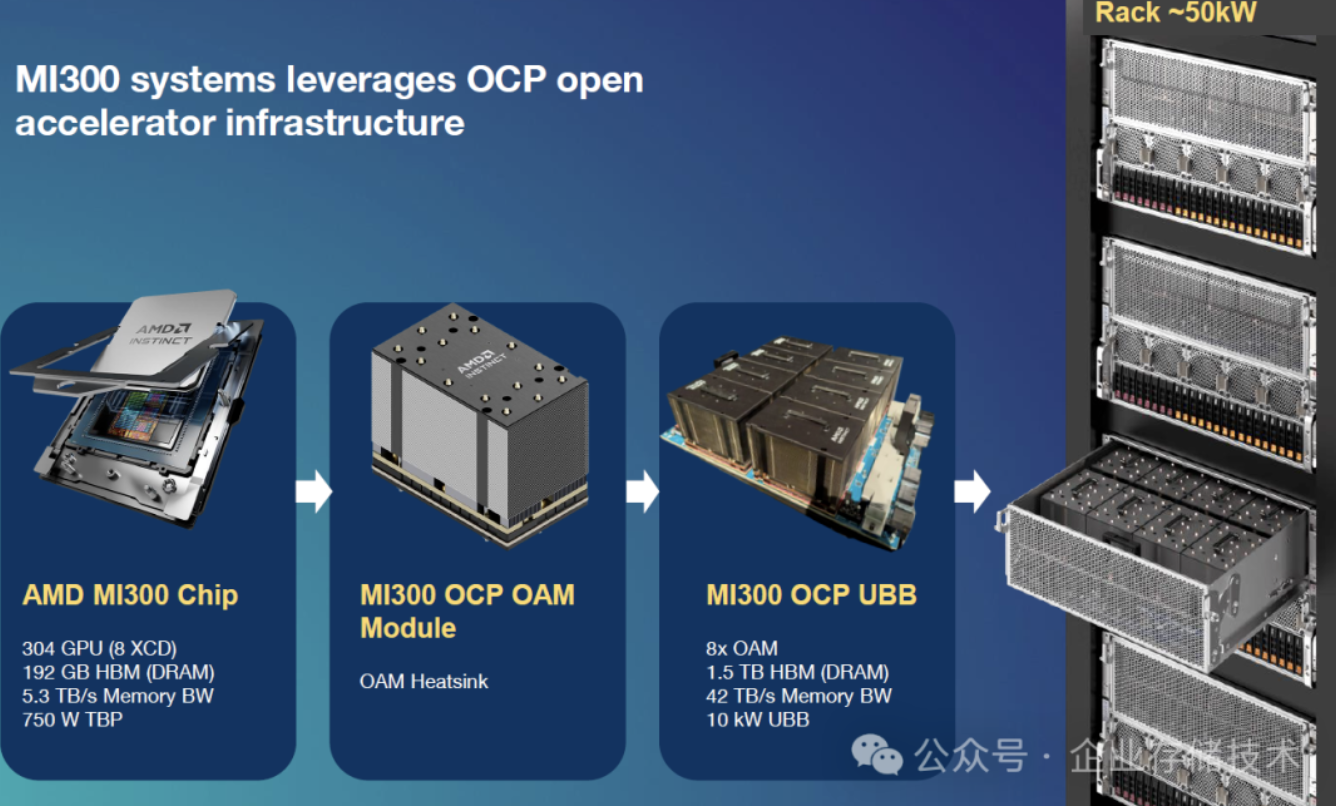

所谓MI300芯片的304个GPU处理单元,分布在8个XCD小芯片上。每颗MI300做成一个OCP OAM模组,然后8个OAM安装在一块UBB主板上。这样的一个机架,耗电大约在50kW左右,所以液冷是现在数据中心里的热门技术。

未来芯片还会越做越大,即使NVIDIA暂时还不转向Chiplet?B100/GeForce 5090的功耗也会继续提高。下文中我还会接着讨论这个话题。

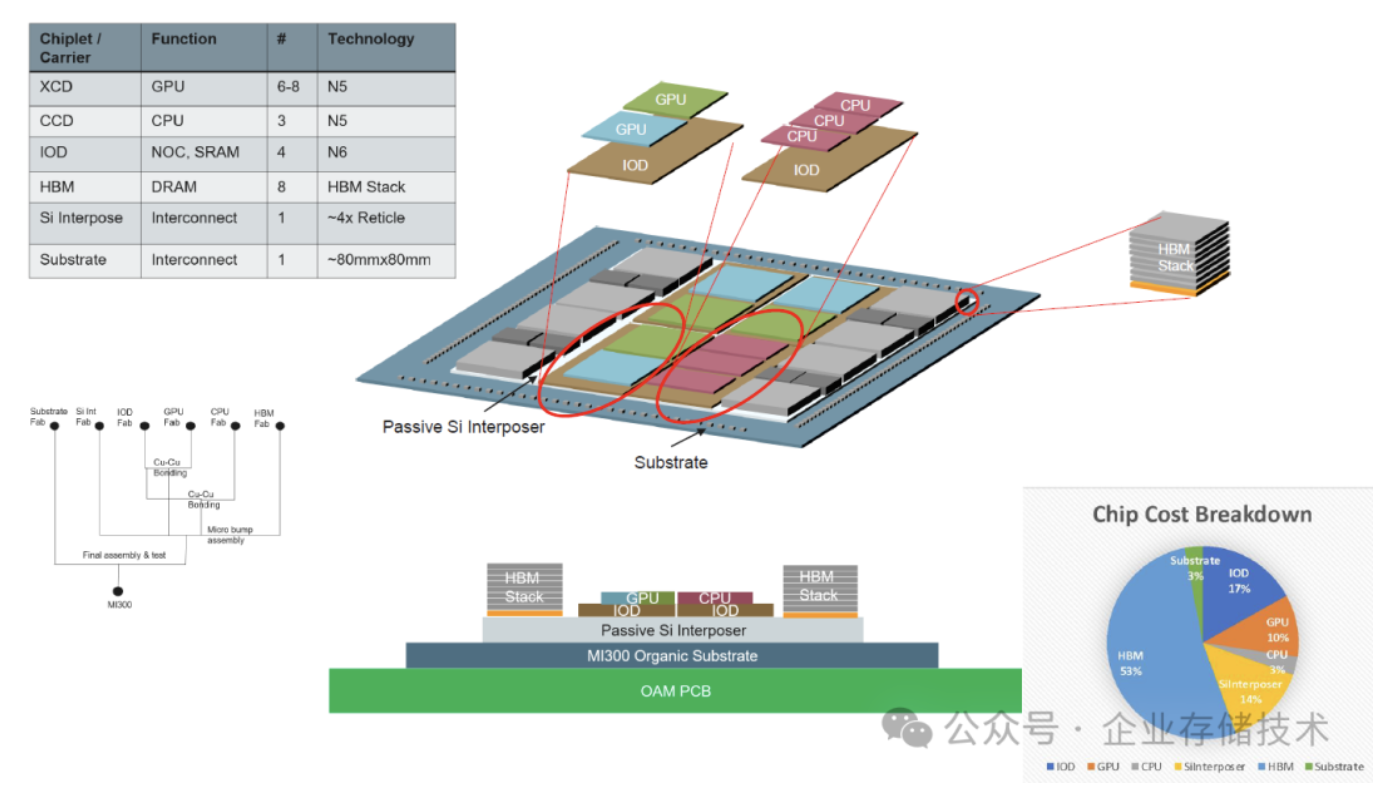

上图分解了MI300(A)的CPU、GPU、I/O Die和HBM Stack等,它们是层叠堆在OAM PCB基板上。6-8片GPU XCD、3片CPU CCD应该都是台积电N5工艺;这里的4个IOD(含NOC和SRAM)是N6工艺,周围HBM内存一共8颗。

右下角的芯片成本Breakdown显示,HBM占比达到53%。

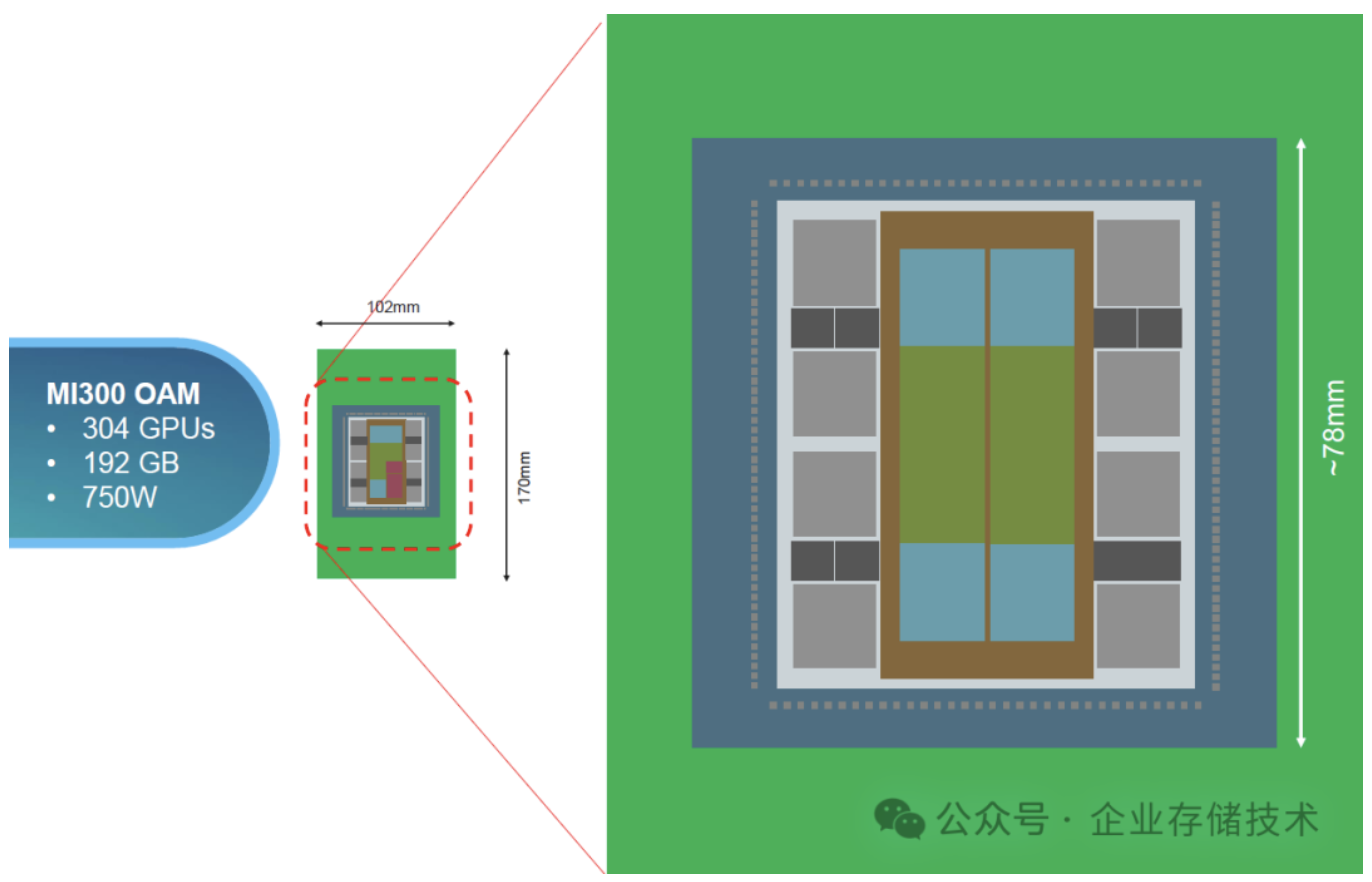

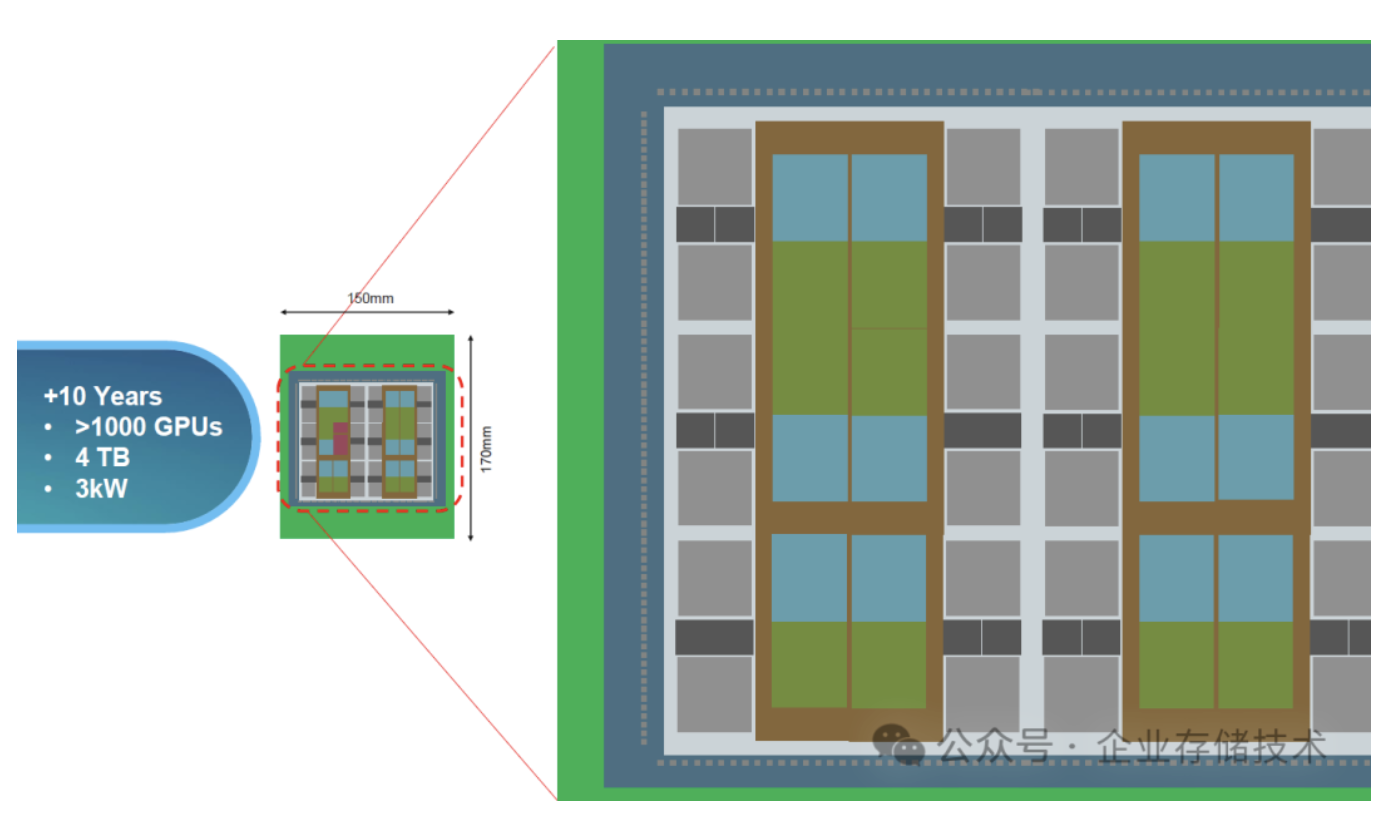

我们先记一下几个数字:MI300 OAM的基板尺寸是102mm*170mm,中间Chiplet部分的边长约为78mm,HBM内存容量192GB,TDP功耗是750W。

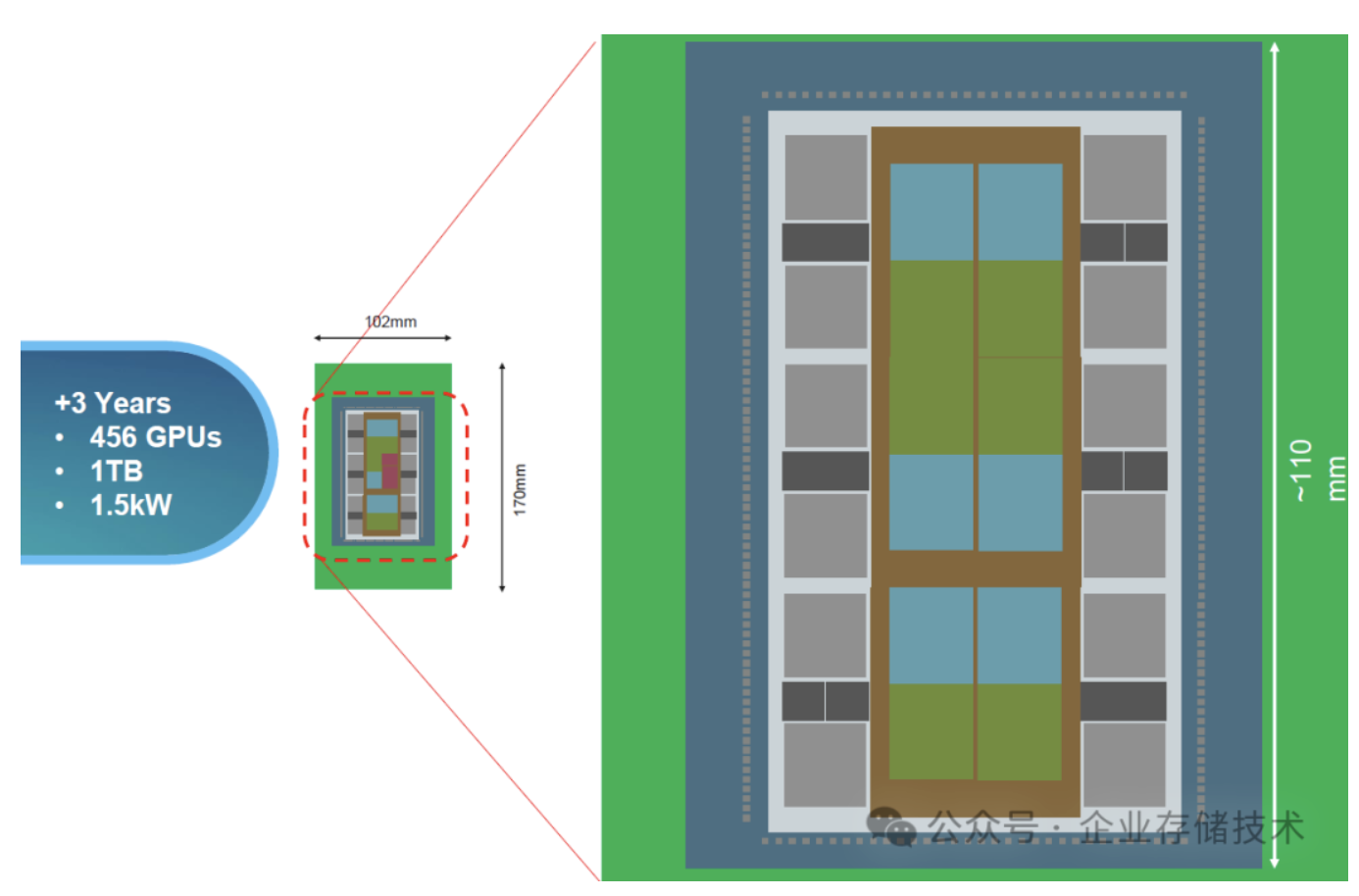

预计3年之后,AMD芯片中GPU处理单元可能增加到456个,HBM内存达到1TB(大模型训练会推动这点吧),整个芯片功耗翻倍至1.5kW。此时OAM基板面积不变,但Chiplet部分的边长增加到约110mm。

继续预测10年后,芯片中增加到1000个GPU处理单元,HBM内存可能达到4TB,OAM模块的功耗将增加到3kW(到时用冷板还是2相浸没液冷技术呢?)。对应的OAM PCB基板面积也增大到150mm * 170mm。

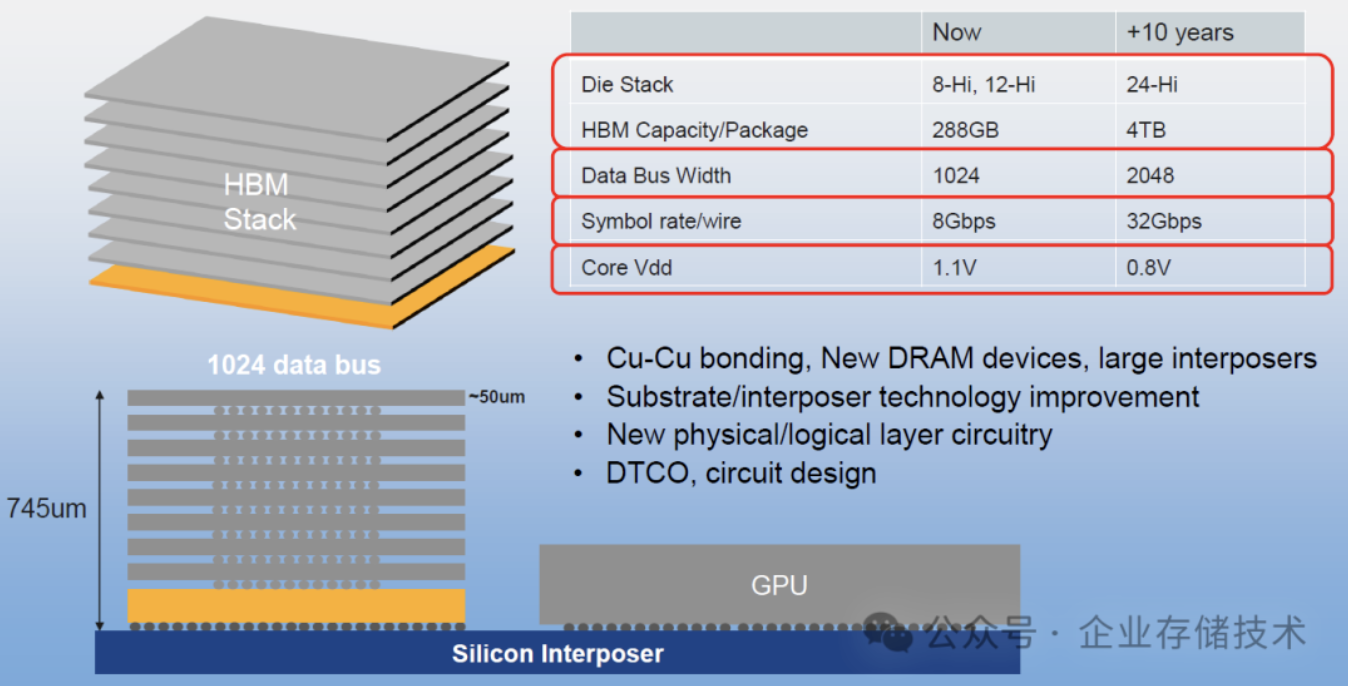

最后也展望下10年后的HBM内存吧:Die堆叠封装的层数预计从今天的8-Hi、12-Hi提高到24Hi;数据总线位宽从1024增加到2048;rate/wire速率从8Gbps提高到32Gbps——最后这一点看上去变化最大,估计也是受益于半导体工艺的发展。

先写这么多,更多资料大家可以从网盘下载参考:)

作者:唐僧 huangliang

原文:企业存储技术

推荐阅读

欢迎关注企业存储技术极术专栏,欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。