快速连接

👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈

引流关键词:缓存,高速缓存,cache, CCI,CMN,CCI-550,CCI-500,DSU,SCU,L1,L2,L3,system cache, Non-cacheable,Cacheable, non-shareable,inner-shareable,outer-shareable, optee、ATF、TF-A、Trustzone、optee3.14、MMU、VMSA、cache、TLB、arm、armv8、armv9、TEE、安全、内存管理、页表…

cache的很多结构、缓存替换策略、协议都是和硬件相关的,很多也都是更改不了的。对于不同的架构不同的core,可能都是不一样的。那么这些信息是如何告诉操作系统的呢?

操作系统需要知道以下信息:

- 有多少级缓存?

- cacheline有多大?

- 缓存中有多少set,多少way?

- 对于清零操作,有多少数据将清零?

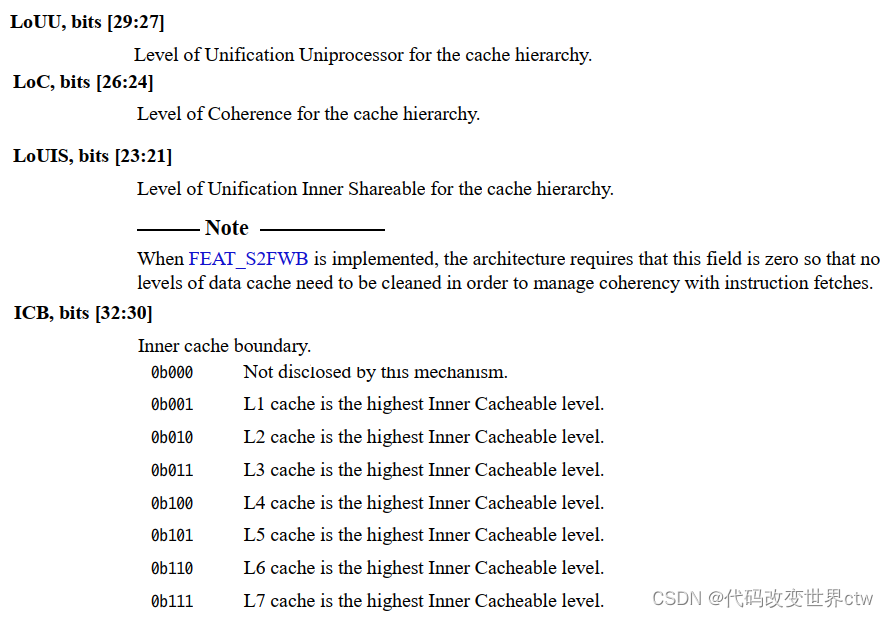

CLIDR_EL1 : Cache Level ID Register

(注意,没有CLIDR_EL0 、CLIDR_EL2 、CLIDR_EL3 , 只有CLIDR_EL1 。)

提供cache的层级关系,以及Inner cache的定义。

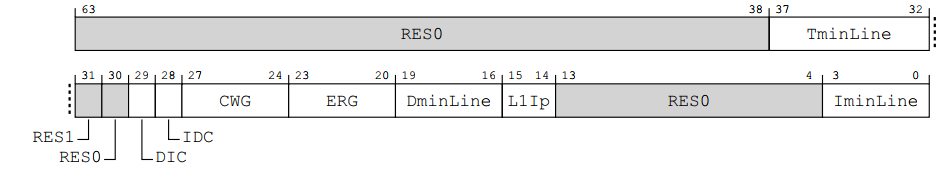

CTR_EL0 : Cache Type Register

(注意,没有CTR_EL1、CTR_EL2、CTR_EL3, 只有CTR_EL0。)

获取cache的一些信息,如cache line的大小

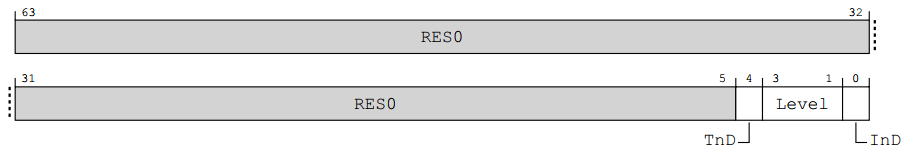

CCSIDR_EL1 和 CSSELR_EL1

(这两个寄存器,也是只有EL1,没有EL0/2/3后缀)

CSSELR_EL1写入cache level值,然后从CCSIDR_EL1中读取该level cache的 set、way信息

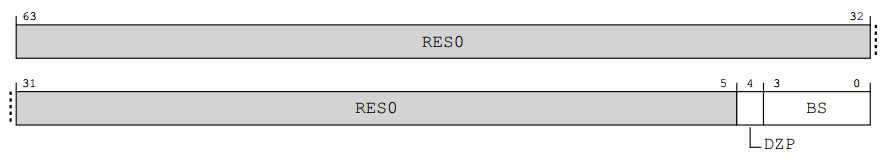

(CSSELR_EL1)

(CCSIDR_EL1 )

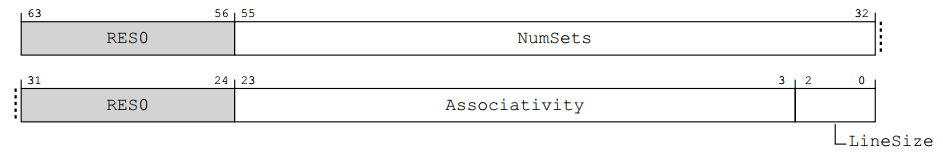

DCZID_EL0 : Data Cache Zero ID Register

(注意,没有DCZID_EL1、DCZID_EL2、DCZID_EL3, 只有DCZID_EL0。)DC ZVA, 按照虚拟地址数据清零,那么是给多少size的数据清零呢,由DCZID_EL0配置。

BS, bits [3:0]--Log2 of the block size in words.

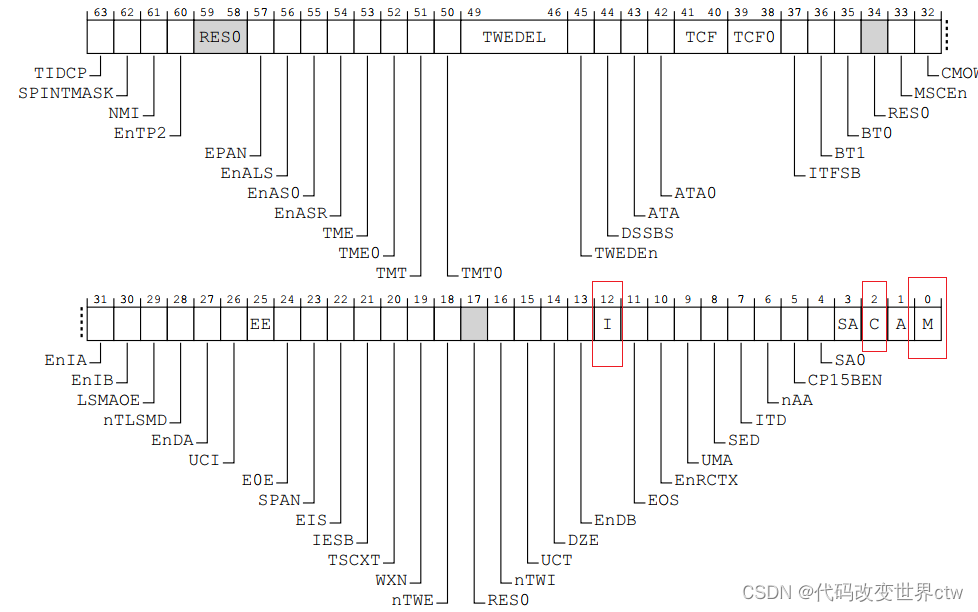

SCTLR_ELx

(注意,有SCTLR_EL1、SCTLR_EL2、SCTLR_EL3, 没有SCTLR_EL0。)

SCTLR.I : disable or enable I-Cache

SCTLR.C: disable or enable D-CacheSCTLR.M: disable or enable MMU

关注"Arm精选"公众号,备注进ARM交流讨论区。