快速连接

👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈

关键词: Non-cacheable,,Cacheable, non-shareable,inner-shareable,outer-shareable, optee、ATF、TF-A、Trustzone、optee3.14、MMU、VMSA、cache、TLB、arm、armv8、armv9、TEE、安全、内存管理、页表…

- 如果将block的内存属性配置成Non-cacheable,那么数据就不会被缓存到cache,那么所有observer看到的内存是一致的,也就说此时也相当于Outer Shareable。

其实官方文档,也有这一句的描述:

在B2.7.2章节 “Data accesses to memory locations are coherent for all observers in the system, and correspondingly are treated as being Outer Shareable” - 如果将block的内存属性配置成write-through cacheable 或 write-back cacheable,那么数据会被缓存cache中。write-through和write-back是缓存策略。

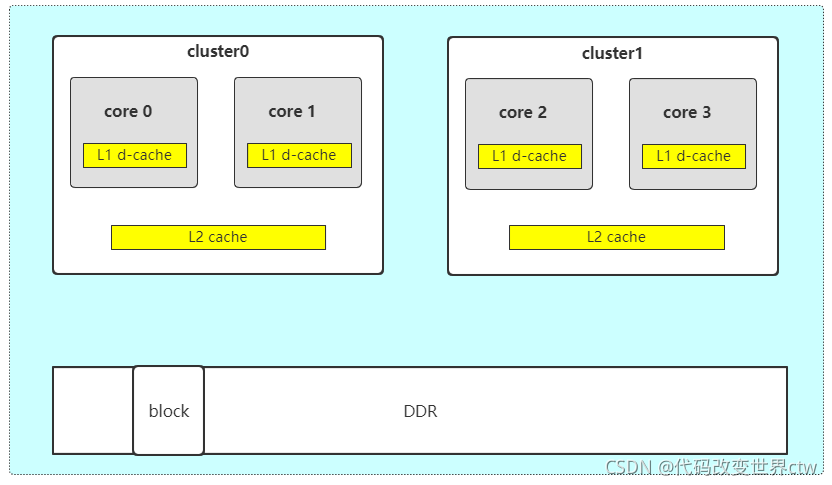

- 如果将block的内存属性配置成 non-shareable, 那么core0访问该内存时,数据缓存的到Core0的L1 d-cache 和 cluster0的L2 cache,不会缓存到其它cache中

- 如果将block的内存属性配置成 inner-shareable, 那么core0访问该内存时,数据只会缓存到core 0和core 1的L1 d-cache中, 也会缓存到clustor0的L2 cache,不会缓存到clustor1中的任何cache里。

- 如果将block的内存属性配置成 outer-shareable, 那么core0访问该内存时,数据会缓存到所有cache中

| Non-cacheable | write-through cacheable | write-back cacheable | |

|---|---|---|---|

| non-shareable | 数据不会缓存到cache (对于观察则而言,又相当于outer-shareable) | Core0读取时,数据缓存的到Core0的L1 d-cache 和 cluster0的L2 cache, 如果core0和core1都读写过该内存,且在core0 core1的L1 d-cache中都缓存了该内存。那么core0在读取数据的时候,core0的L1 Dcache会更新,但core 1的L1 Dcache不会更新 | 同左侧 |

| inner-shareable | 数据不会缓存到cache (对于观察则而言,又相当于outer-shareable) | Core0读取时,数据缓存的到Cluster0中所有cache | 同左侧 |

| outer-shareable | 数据不会缓存到cache (对于观察则而言,又相当于outer-shareable) | Core0读取时,数据缓存的到所有cache | 同左侧 |

关注"Arm精选"公众号,备注进ARM交流讨论区。