快速连接

👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈

一些质疑

网上的好多篇博文,一提Cache的多核一致性就必然提到MESI、MOESI ,然后就开始讲MESI、MOESI维护性原理?试问一下,您是真的不理解MES吗?您真的需要学习MESI?你不理解的是架构对吧,而不是学什么鬼协议!

既然您要学了MESI,那么这里也提出几个问题:

(1)、ARM架构中真的使用MESI了吗?

(2)、MESI是一个协议? 是谁来维护的?总得有个硬件实现这个协议吧,是在ARM Core中? CCI-400中?SCU中?DSU中?

(3)、MESI的四种状态,分别记录在哪里的?

怎样去维护多核一致性

然后,是有三种机制可以保持一致性:

- 禁用缓存是最简单的机制,但可能会显着降低 CPU 性能。为了获得最高性能,处理器通过管道以高频率运行,并从提供极低延迟的缓存中运行。缓存多次访问的数据可显着提高性能并降低 DRAM 访问和功耗。将数据标记为“非缓存”可能会影响性能和功耗。

- 软件管理的一致性是数据共享问题的传统解决方案。在这里,软件(通常是设备驱动程序)必须清除或刷新缓存中的脏数据,并使旧数据无效,以便与系统中的其他处理器或主设备共享。这需要处理器周期、总线带宽和功率。

- 硬件管理的一致性提供了一种简化软件的替代方案。使用此解决方案,任何标记为“共享”的缓存数据将始终自动更新。该共享域中的所有处理器和总线主控器看到的值完全相同。

燃鹅,我们使用的却是第三种 硬件管理的一致性, 意思就是:做为一名软件工程师,我们啥也不用管了,有人帮我们干活,虽然如此,但我们还是希望理解下硬件原理。

再讲原理之前,我们先补充一个场景:

假设在某一操作系统中运行了一个线程,该线程不停着操作0x4000_0000地址处内存(所以我们当然期望,它总是命中着),由于系统调度,这一次该线程可能跑在cpu0上,下一次也许就跑在cpu1上了,再下一次也许就是cpu4上了(其实这种行为也叫做CPU migration)

或者举个这样的场景也行:

在Linux Kernel系统中,定义了一个全局性的变量,然后多个内核线程(多个CPU)都会访问该变量.

在以上的场景中,都存在一块内存(如0x4000_0000地址处内存)被不同的ARM CORE来访问,这样就会出现了该数据在main-memory、SCU-0的L2 cache、SCU-1的L2 cache、8个Core的L1 cache不一致的情况。

既然出现了数据在内存和不同的cache中的不一致的情况,那么就需要解决这个问题(也叫维护一致性),那么怎么维护的呢,上面也说了“使用 硬件管理的一致性”,下面就以直接写答案的方式,告诉你硬件是怎样维护一致性的。

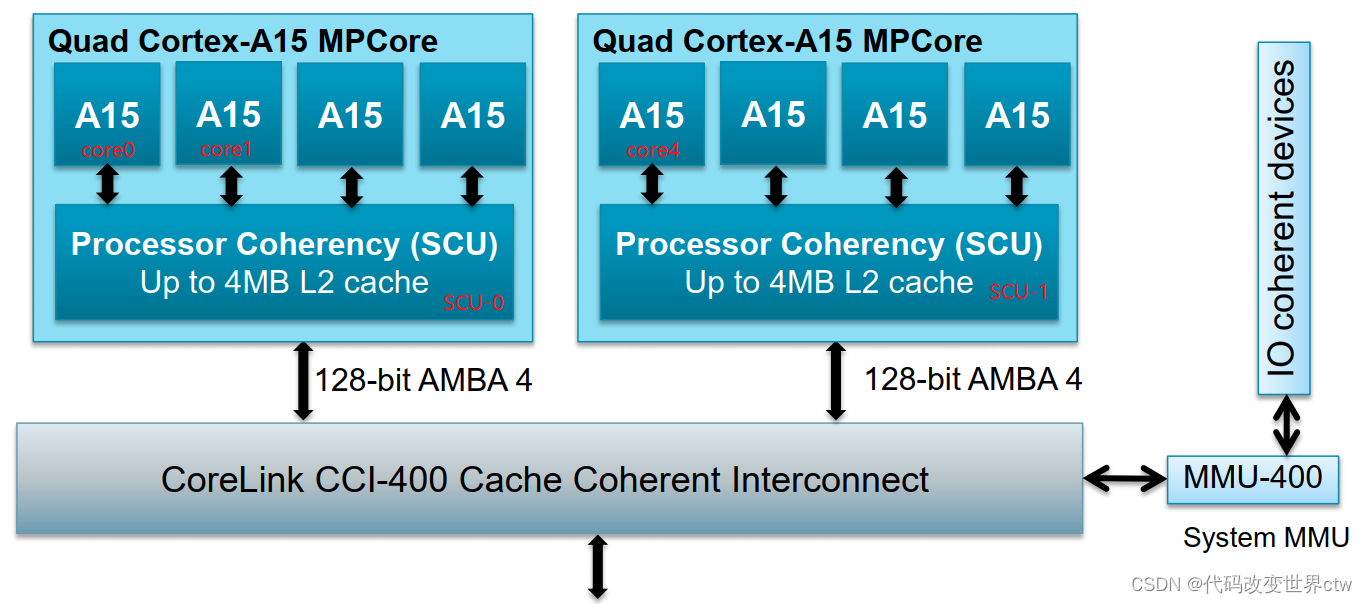

我们先看一张老的图(bit.LITTLE架构的)吧

- core1、core1、SCU-0的cache的一致性,是由SCU-0来维护的(至于这里是不是遵守了MESI协议,答案:YES)

- SCU-0、SCU-1、main-memory的一致性,是由于CCI-400来维护的(至于这里是不是遵守了MESI协议,答案:我也不知道)

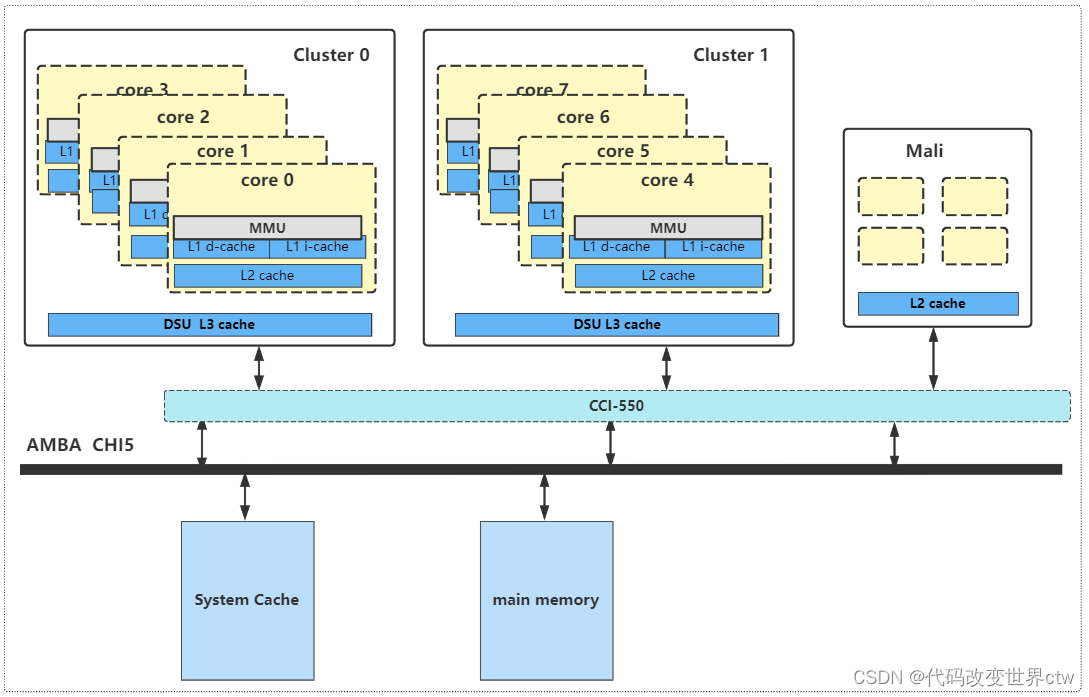

再看一张比较新的图(DynamIQ架构的)吧 - core 0的L2 cache、core 1的L2 cache、DSU-0 L3 cache的一致性 由DSU-0来维护(至于这里是不是遵守了MESI协议,答案: YES)

DSU-0 L3 cache、DSU-1 L3 cache、Mali的L2 cache、system cache、main-memory的一致性是由于CCI-550来维护的(至于这里是不是遵守了MESI协议,答案:我也不知道)

MESI、MOESI 的介绍

既然您一味着坚持要学习

MESI、MOESI,那么咱也不能不介绍对不,紧跟着大佬们步伐,网上抄一抄(注意:那不叫抄,那叫借鉴)

首先是Modified Exclusive Shared Invalid (MESI) 协议中定义了4个状态:

| MESI State | Definition | |

|---|---|---|

| Modified (M) | 这行数据有效,数据已被修改,和内存中的数据不一致,数据只存在于该高速缓存中 | |

| Exclusive (E) | 这行数据有效,数据和内存中数据一致,数据只存在于该高速缓存中 | |

| Shared (S) | 这行数据有效,数据和内存中数据一致,多个高速缓存有这行数据的副本 | |

| Invalid (I) | 这行数据无效 |

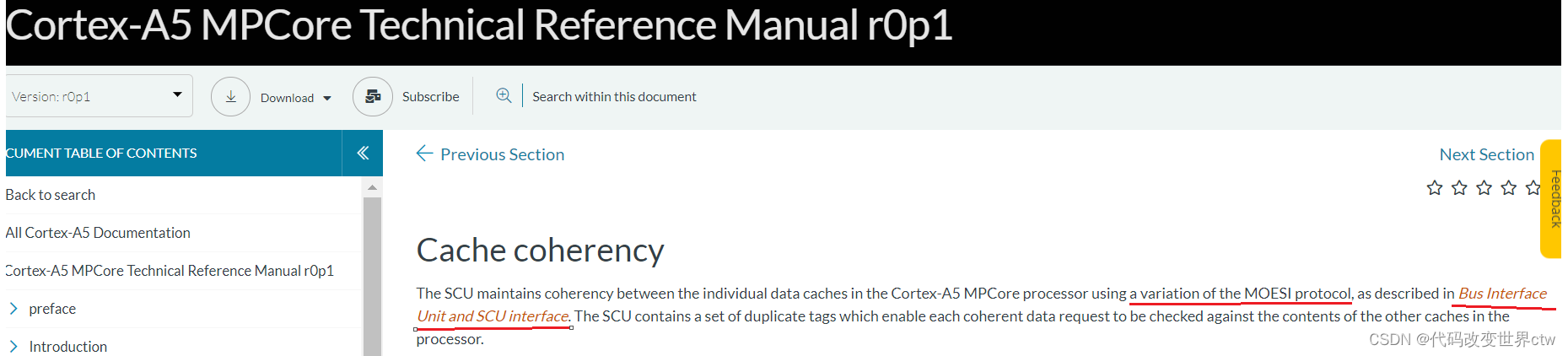

其次,在ARM的很多core中,定义了第五种状态Shared Modified,这种称之为MOESI 协议. 而ARM使用的则是MOESI的变体(啥叫变体,咋变的,变的哪些,文当它没有说)

然后我们通过数据流图的方式,观看下MESI这四种状态的情况:

MESI状态之间的切换:

Events:

RH = Read Hit

RMS = Read miss, shared

RME = Read miss, exclusive

WH = Write hit

WM = Write miss

SHR = Snoop hit on read

SHI = Snoop hit on invalidate

LRU = LRU replacement

Bus Transactions:

Push = Write cache line back to memory

Invalidate = Broadcast invalidate

Read = Read cache line from memory

总结

看完以上信息,我们再次总结一下,我们学习cache一致性,我们最大的困惑或瓶颈是啥,是不理解MESI吗?应该还是对架构的理解和认知。学习MESI,不如去学习DSU、CCI-550原理吧。

关注"Arm精选"公众号,备注进ARM交流讨论区。