快速连接

👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈

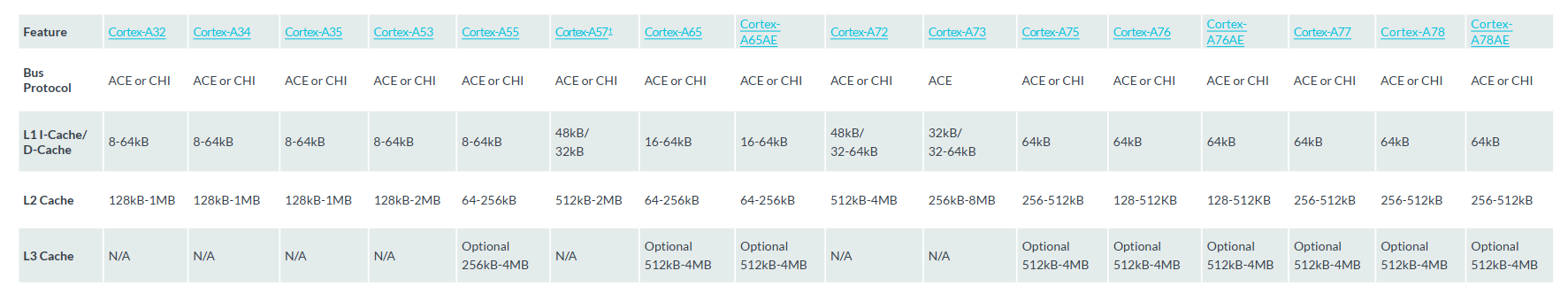

我们知道每一个Arm core的L1/L2/L3的cache是多大的,要么是IP定死的,要么是ASIC可配置的。那么从性能角度来说,是不少配置的越大越好呢? 配置大了对功耗会有哪些影响呢?

增大缓存配置可以提高系统的性能,但同时也会增加功耗。这是因为较大的缓存需要更多的存储单元和更复杂的电路来实现,从而消耗更多的能量。

以下是大缓存配置可能对性能功耗产生的影响:

- 增加访问延迟:较大的缓存需要更长的访问路径和更多的电路来支持数据的读取和写入。这可能导致访问延迟的增加,因为数据需要在更复杂的电路中传输和处理。

- 增加动态功耗:较大的缓存需要更多的存储单元来存储数据,这意味着更多的存储单元需要进行充电和放电操作,从而增加了动态功耗的消耗。

- 增加静态功耗:较大的缓存需要更多的电路和存储单元来支持其功能,这导致了较高的静态功耗。即使在不活跃状态下,这些电路和存储单元也需要一定的能量供应。

- 散热和散热需求:较大的缓存会产生更多的热量,需要更好的散热系统来保持芯片的温度在安全范围内。这可能需要增加散热器的尺寸和功率管理技术来控制温度。

在设计缓存系统时,需要进行权衡和优化,以平衡性能和功耗之间的关系。根据具体的应用需求,可能需要在缓存大小、访问延迟和功耗之间做出合适的折衷。此外,还可以通过使用更高效的缓存算法、调整缓存层次结构以及采用先进的功耗管理技术等方式来减少功耗的影响。

关注"Arm精选"公众号,备注进ARM交流讨论区。