快速连接

👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈

思考:在页表的Descriptors中的Lower attributes中的AttrIndx中指向的MAIR_EL1寄存器中有配置cacheable属性, 在TCR_EL1寄存器中有cacheable属性位ORGN0、IRGN0、ORGN1、IRGN1,这两种cacheable属性有啥区别呢?

概念定义

总结如下:

- 一个Inner Shareability domain中包含一组observers,这些observers去访问Inner Shareable attribute的内存时,内存是一致的。

- 一个OuterShareability domain中包含一组observers,这些observers去访问OuterShareable attribute的内存时,内存是一致的。

关注"Arm精选"公众号,备注进ARM交流讨论区。

添加vx : arm_2023,备注进ARM交流讨论区。

以上总结还是有点绕,现在用人话/白话再次总结下:

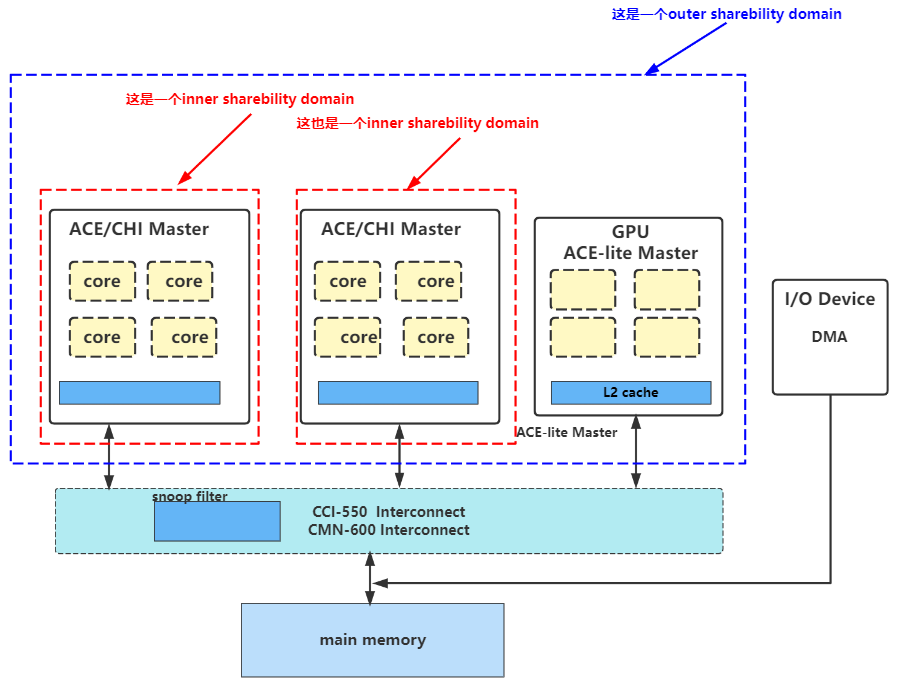

- 首先把一个小范围内的cpu,划定在Inner Shareability domain中。然后你把一块内存配置成Inner Shareable,那么这个domain中的所有cpu看到的这块内存是一致的。

- 然后把更大范围内的cpu,划定在Outer Shareability domain中。然后你把一块内存配置成Outer Shareable,那么这个domain中的所有cpu看到的这块内存是一致的。

另外Inner Shareability domain 是 Outer Shareability domain的一个子集

最后最后最最后,再一次的总结:

1、Inner Shareability domain、OuterShareability domain 描述的是一个集合,即ASIC硬件在设计的时候,定义一些cpu属于一个Inner domain,更大范围的一些cpu属于Outer domain

2、Inner Shareable 、OuterShareable 描述的内存属性,即这块内存在哪些domain域中,由硬件自动维护其一致性

示例练习

在页表中,将一个page的属性配置成Outer Shareable, 那么意味着一个Outer shareability domain域中的所有observers访问此内存时,硬件会自动维护其一致性。

在页表中,将一个page的属性配置成Inner Shareable, 那么意味着一个Inner shareability domain域中的所有observers访问此内存时,硬件会自动维护其一致性。

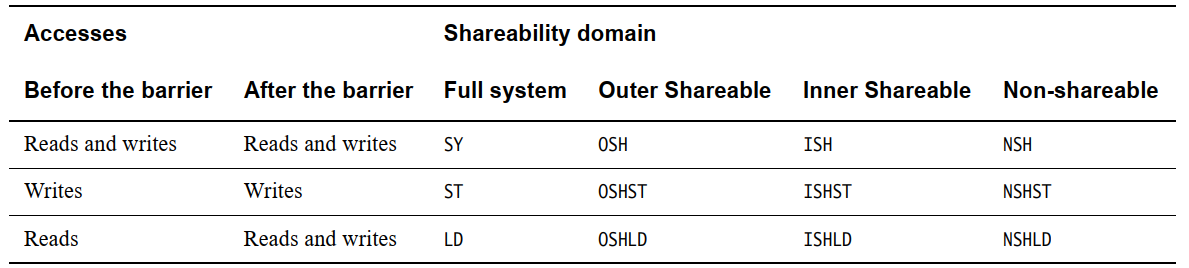

如图所示示例中,在DSB/DMB指令中,会使用到以下限定符,如果使用OSH,则表示outer shareable,其实就是说该指令限定的范围是在outer shareability domain域中,即等待outer shareability domain中惯有观察着都看到了内存的操作后,再继续往下执行。

另外再来一个提醒,ARM推荐,将在一个操作系统中跑的所有cpu,设计到一个Inner Shareable domain。目前绝大数SOC也都是这么设计的。也就是说,哪些cpu在一个Inner Shareable domain中,是SOC设计时决定的。

最后

如果您已经订阅此付费专栏,请务必加我微信(coding_the_world),备注"姓名+职业方向+ARM专栏",我拉您如ARMv8/ARMv9讨论群。

也可以从下述链接找到群号扫码进入:

https://www.processon.com/view/link/641321133524617475ff9b8a

关注"Arm精选"公众号,备注进ARM交流讨论区。