快速连接

👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈

10 访问cache

Cortex-A720核心提供一种机制,通过IMPLEMENTATION DEFINED系统寄存器可以读取L1缓存、L2缓存和Translation Lookaside Buffer(TLB)。当缓存数据与系统内存数据之间的一致性异常时,您可以使用此机制来调查任何问题。

只有在EL3中才可以访问内部内存(cache)。在所有其他异常级别中,执行这些指令会导致未定义指令异常。

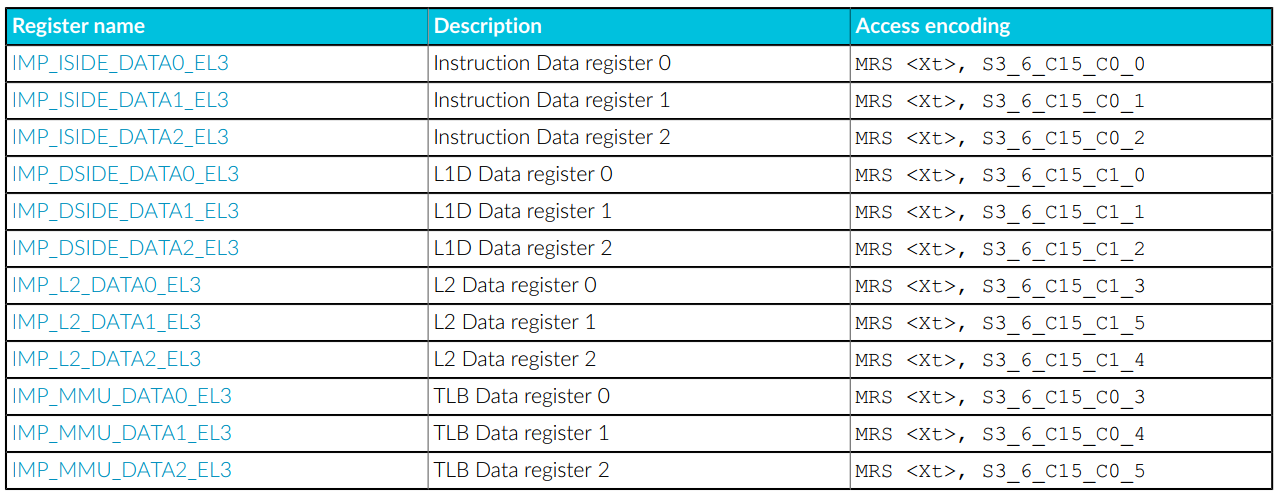

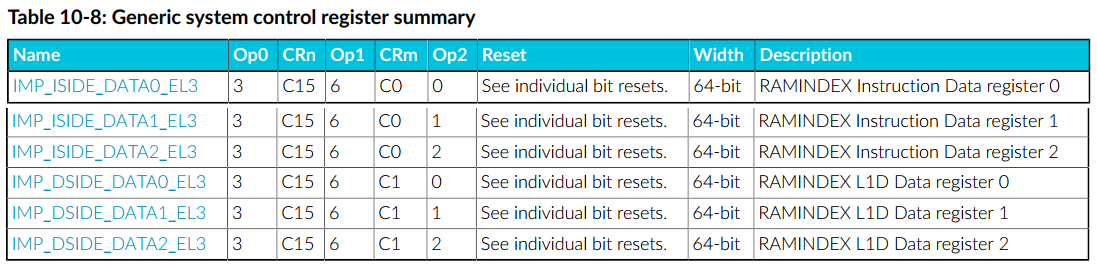

您可以使用下表中的十二个只读(RO)系统寄存器来访问内部内存,表格标题为“用于访问内部内存的系统寄存器”。通过使用以下SYS指令来选择内部内存,可以通过编程IMPLEMENTATION DEFINED RAMINDEX寄存器进行选择:

注意:

• 所有系统寄存器都是只读(RO)且64位宽

• 寄存器复位值,请参阅各个位的复位

• 对数据寄存器的任何访问都会返回数据

10.1 L1 cache编码

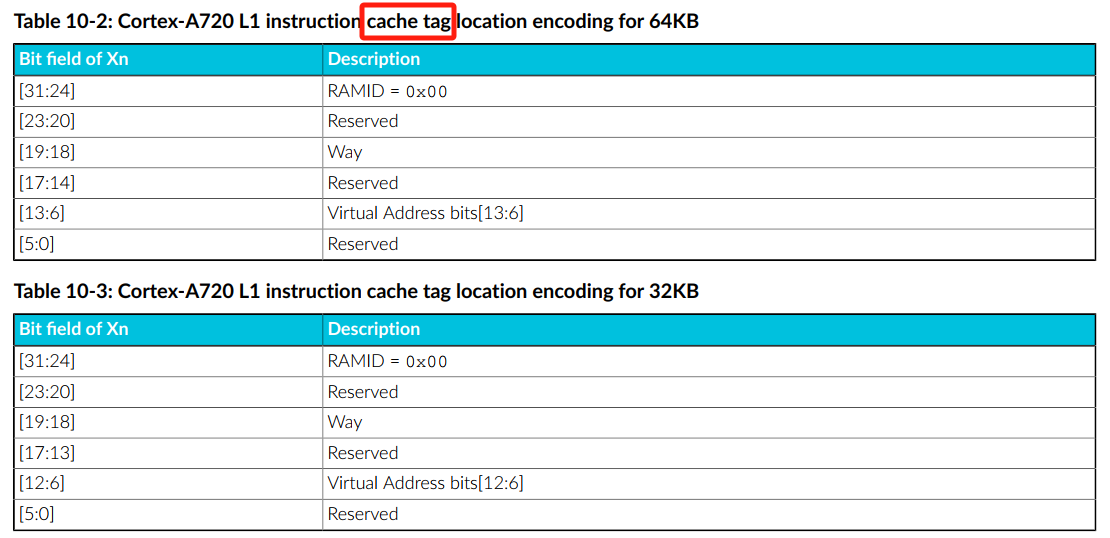

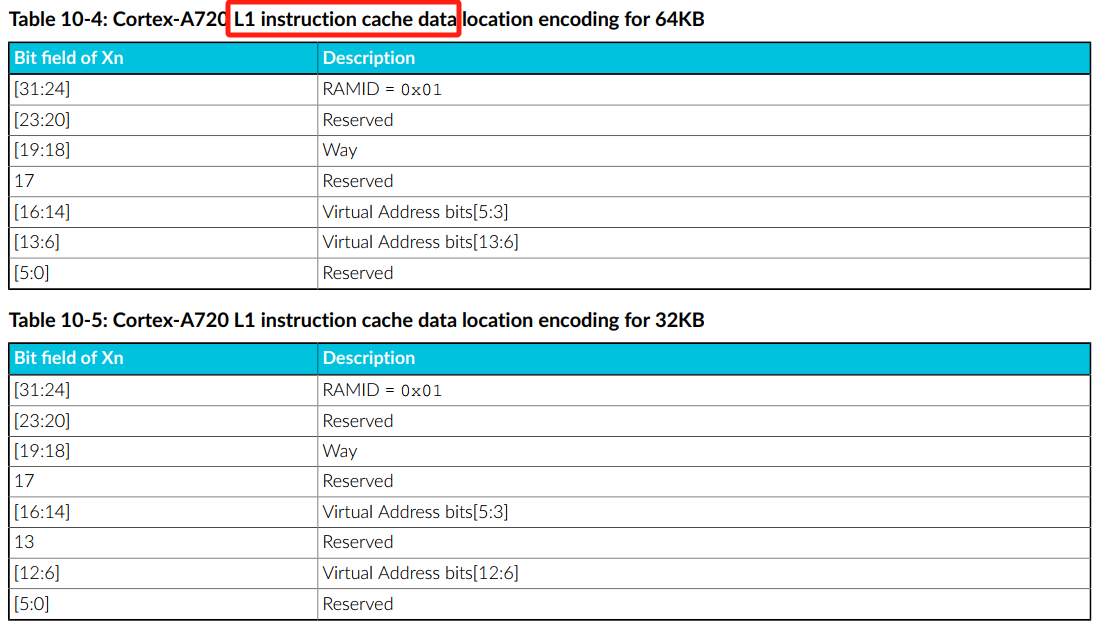

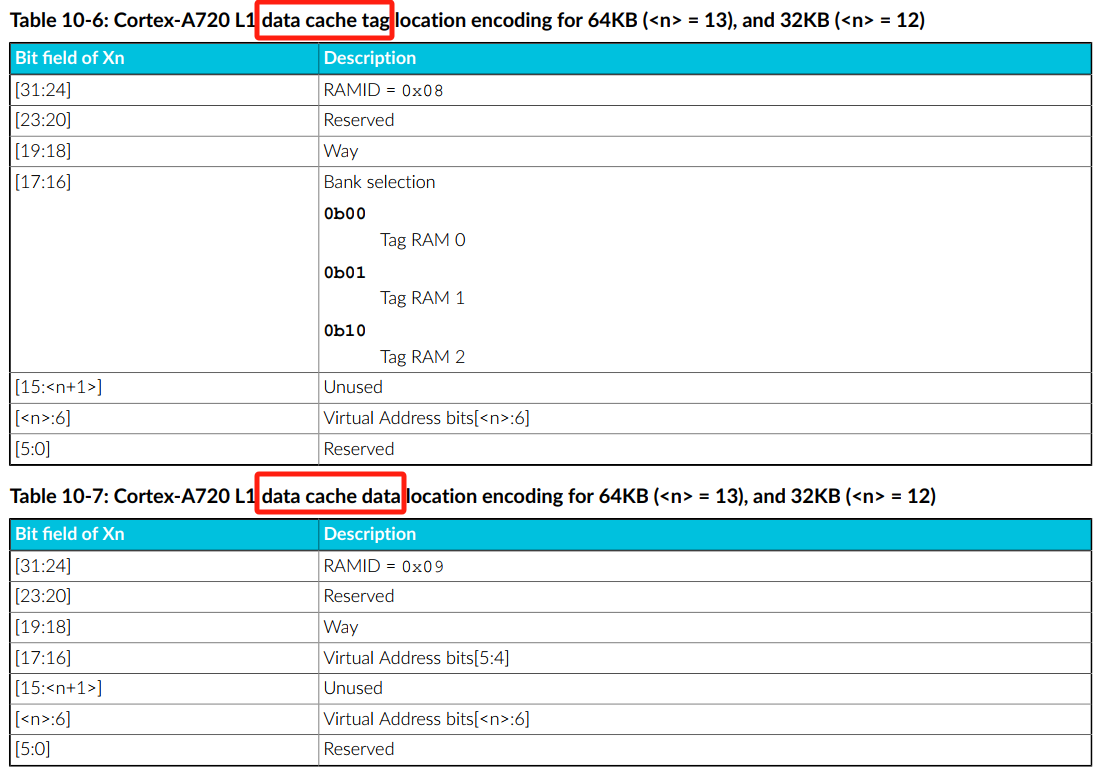

L1数据缓存和指令缓存均为4路组关联。

配置的缓存大小确定了每路中的组数。用于查找标签和数据存储器的缓存数据条目的编码在适当的SYS指令中的Xn中设置。对于标签和数据RAM访问,编码类似。

以下表格显示了用于定位和选择给定缓存行所需的编码。

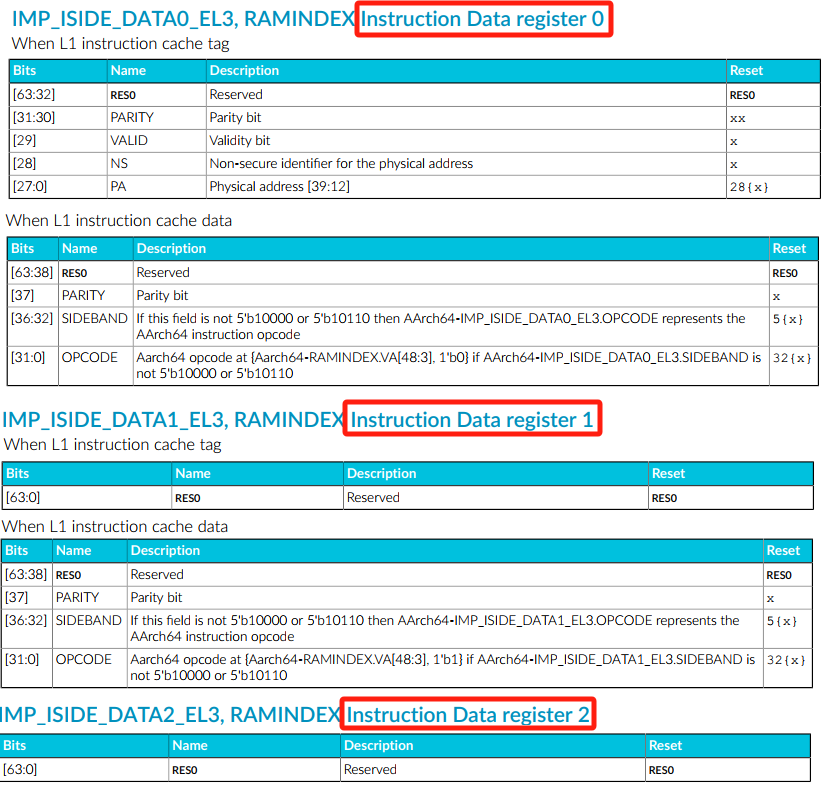

10.1.1 L1 RAM返回的数据

对于每个寄存器,对L1 RAM的任何访问都会返回数据。

单击以下表格中的寄存器名称,以查看有关返回数据格式的详细信息。

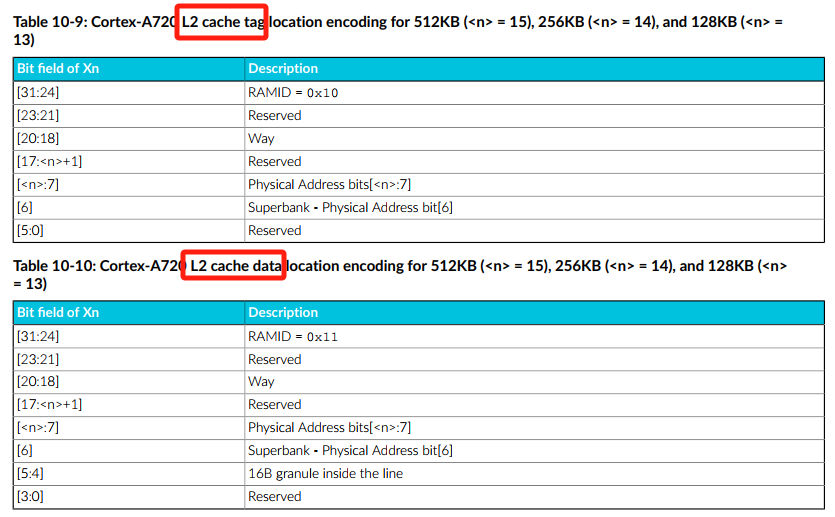

10.2 L2缓存编码

L2缓存为8路组关联。

配置的缓存大小确定了每路中的组数。用于查找标签和数据存储器的缓存数据条目的编码在适当的SYS指令中的Xn中设置。对于标签和数据RAM访问,编码类似。

以下表格显示了用于定位和选择给定缓存行所需的编码。

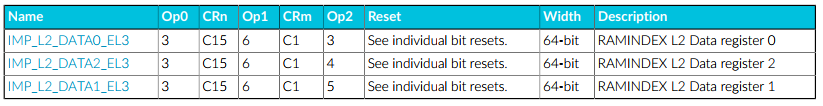

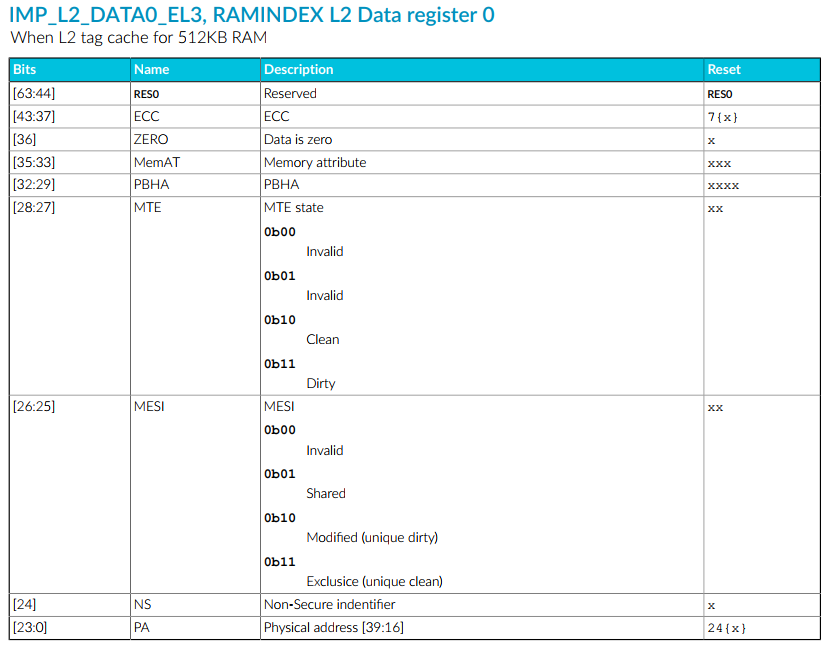

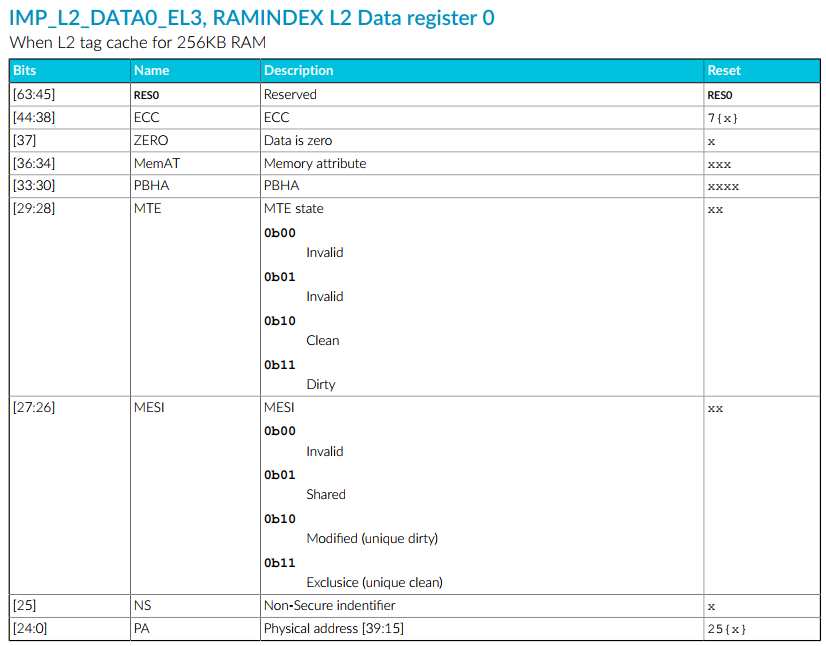

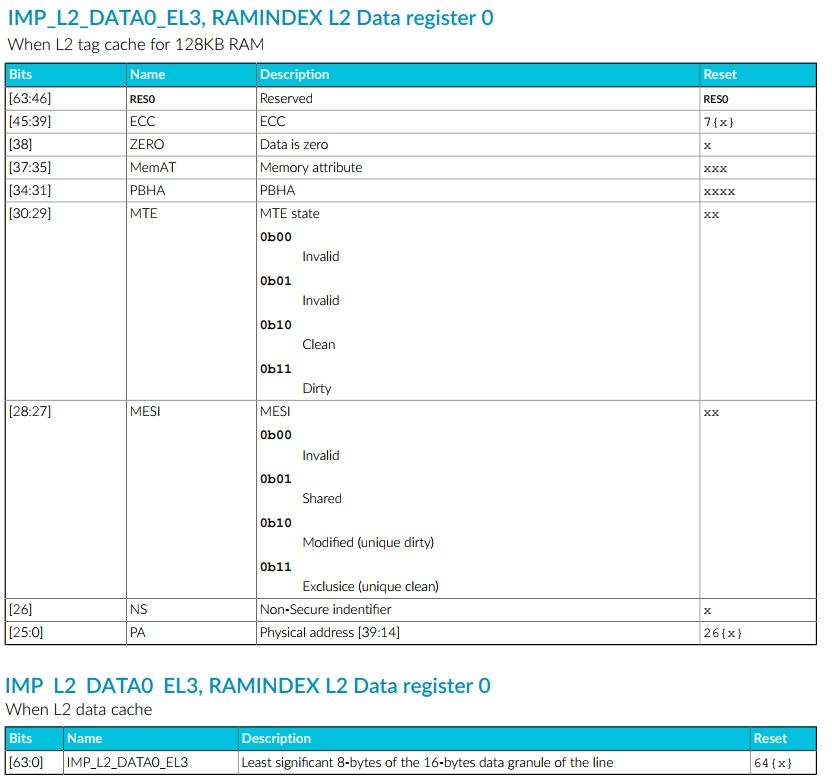

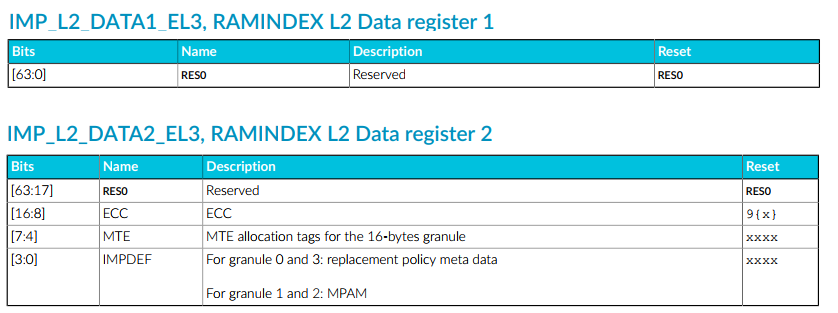

10.2.1 L2 RAM返回的数据

对于每个寄存器,对L2 RAM的任何访问都会返回数据。

单击以下表格中的寄存器名称,以查看有关返回数据格式的详细信息。

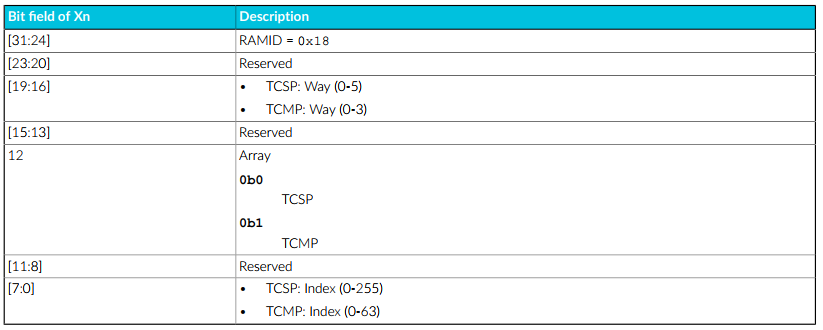

10.3 L2 TLB编码

L2 TLB RAM(小页面的TCSP)为6路组关联,L2 TLB RAM(中页面的TCMP)为4路组关联。

以下表格显示了用于定位和选择给定缓存行所需的编码。

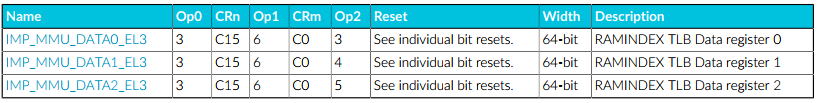

10.3.1 L2 TLB RAM返回的数据

对于每个寄存器,对L2 TLB RAM的任何访问都会返回数据。

单击以下表格中的寄存器名称,以查看有关返回数据格式的详细信息。

关注"Arm精选"公众号,备注进ARM交流讨论区。