快速连接

👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈

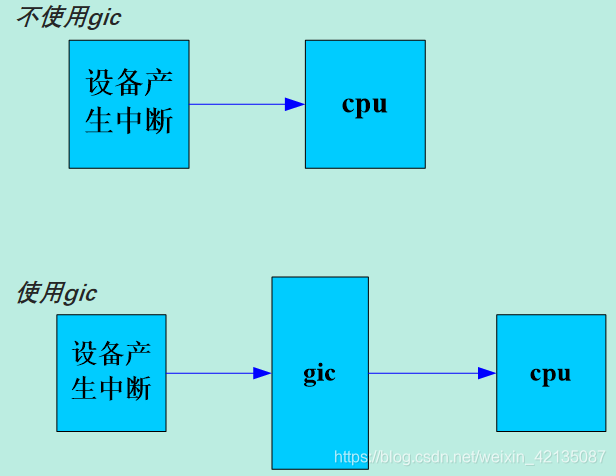

1、gic概念

gic : general interrupt controller

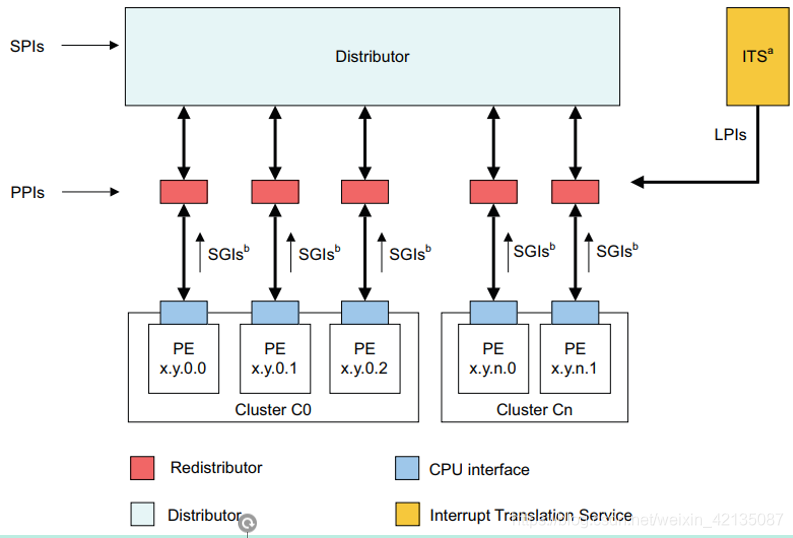

(1)、模型

(2)、分类

GIC中断控制器的分类:gicv1(已弃用),gicv2,gicv3,gicv4

◾gic400,支持gicv2架构版本。

◾gic500,支持gicv3架构版本。

◾gic600,支持gicv3架构版本

(3)、核心功能

gic的核心功能,就是对soc中外设的中断源的管理,并且提供给软件,配置以及控制这些中断源。

◾当对应的中断源有效时,gic根据该中断源的配置,决定是否将该中断信号,发送给CPU。如果有多个中断源有效,那么gic还会进行仲裁,选择最高优先级中断,发送给CPU。

◾当CPU接受到gic发送的中断,通过读取gic的寄存器,就可以知道,中断的来源来自于哪里,从而可以做相应的处理。

◾当CPU处理完中断之后,会告诉gic,其实就是访问gic的寄存器,该中断处理完毕。gic接受到该信息后,就将该中断源取消,避免又重新发送该中断给cpu以及允许中断抢占

(4)、gicv3较gicv2的特点

GICv3架构是GICv2架构的升级版,增加了很多东西。变化在于以下:

◾使用属性层次(affinity hierarchies),来对core进行标识,使gic支持更多的core

◾将cpu interface独立出来,用户可以将其设计在core内部

◾增加redistributor组件,用来连接distributor和cpu interface

◾增加了LPI,使用ITS来解析

◾对于cpu interface的寄存器,增加系统寄存器访问方式

2、中断的一些概念

(1)、中断的分类、分组

中断触发方式

◾edge-triggered: 边沿触发,当中断源产生一个边沿,中断有效

◾level-sensitive:电平触发,当中断源为指定电平,中断有效

中断类型(<font color=red size=3>红色是gicv3特有</font>)

◾PPI:(private peripheral interrupt),私有外设中断,该中断来源于外设,但是该中断只对指定的core有效。

◾SPI:(shared peripheral interrupt),共享外设中断,该中断来源于外设,但是该中断可以对所有的core有效。

◾SGI:(software-generated interrupt),软中断,软件产生的中断,用于给其他的core发送中断信号

◾LPI : (Locality-specific Peripheral Interrupt)

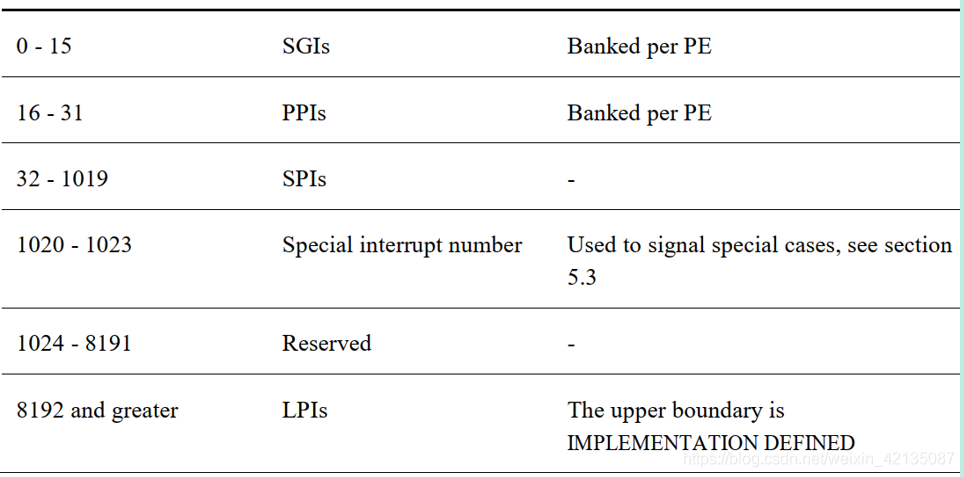

中断号(红色是gicv3特有)

◾ID0-ID15,分配给SGI (一般会将0-7给REE,8-15给TEE)

◾ID16-ID31,分配给PPI

◾ID32-ID1019,分配给SPI

◾ID1020-ID1023,特殊中断号

◾ID1024-ID8191,reserved

◾8192及其以上,LPI

Group分组(GICD_IGROUPRn) -- gicv2

◾group0:安全中断,由nFIQ驱动

◾group1:非安全中断,由nIRQ驱动

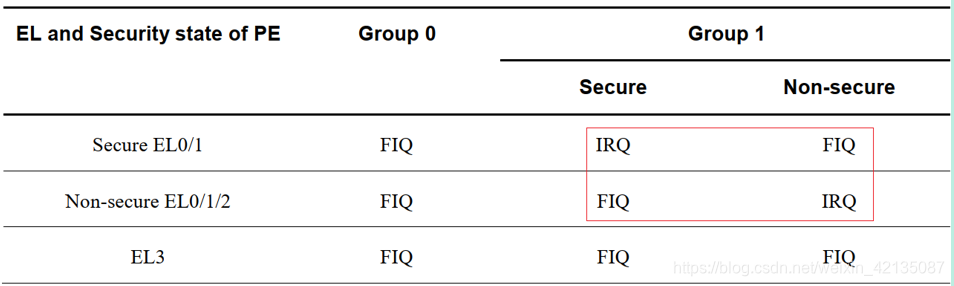

Group分组(GICD_IGROUPRn)-- gicv3

◾group0:安全中断

◾non-secure group1:非安全中断

◾secure group1:安全中断

gicv3的irq、fiq的标记

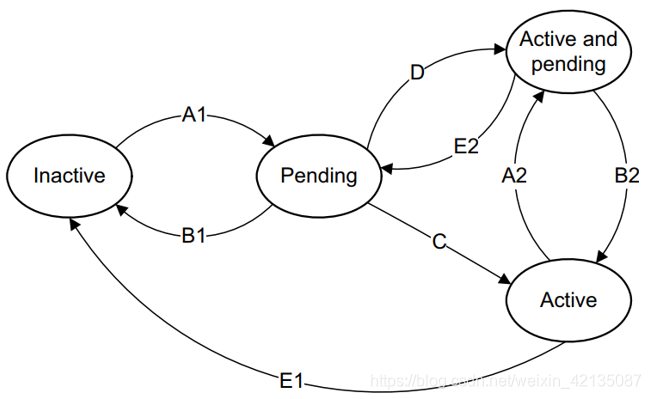

(2)、中断的状态

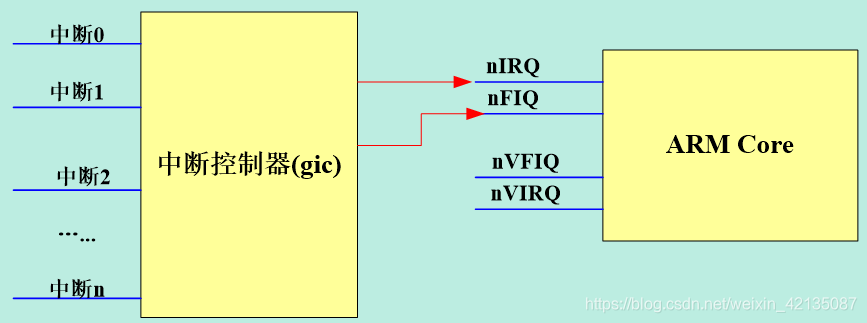

3、gic和ARM Core的连接

(1)、gicv2和ARM Core的连接

ARM cortex-A系列处理器,提供了4个管脚给soc,实现外界中断的传递

◾nIRQ: 物理普通中断

◾nFIQ: 物理快速中断

◾nVIRQ: 虚拟普通中断

◾nVFIQ: 虚拟快速中断

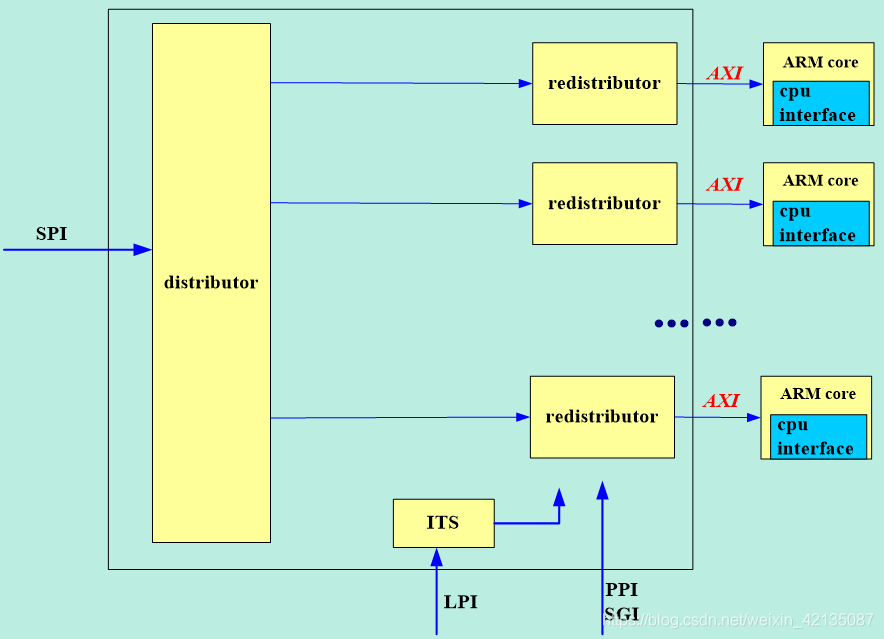

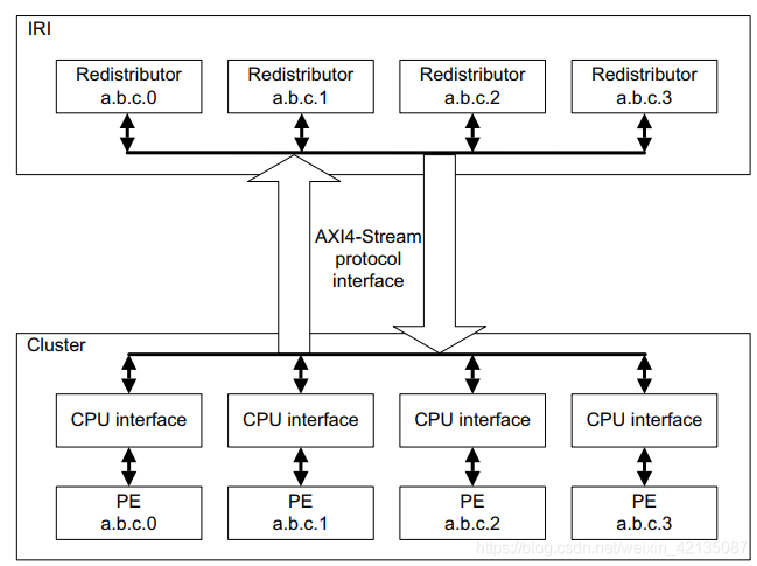

(2)、gicv3和ARM Core的连接

gicv3 AXI-stream协议

◾gic stream协议,是基于AXI-stream协议。用于gic的IRI组件,和cpu interface之间,传输信息。

◾distributor,redistributor和ITS,统称为IRI组件(interrupt routing infrastructure)。

◾gic stream协议,包含以下2个接口:

(1)下行AXI-stream接口:用于IRI向cpu interface传递信息,连接

(2)上行AXI-stream接口:用于cpu interface向IRI传递信息

4、gic的组件

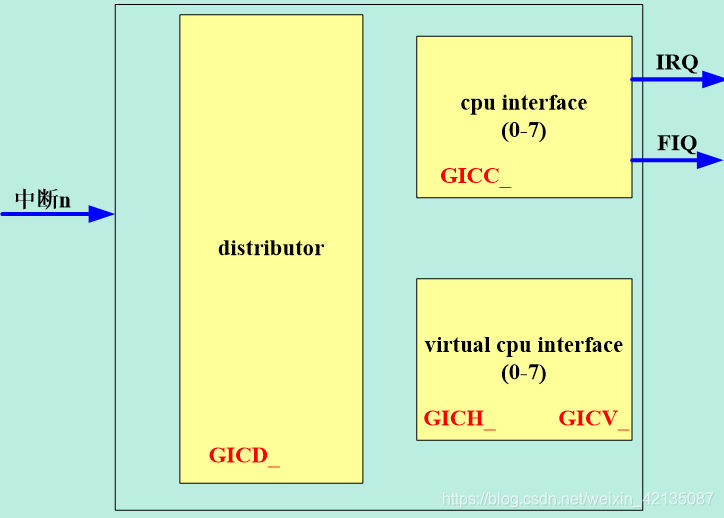

(1)、gicv2的组件

在GICv2中,最大支持8个core

◾distributor:实现中断分发,对于PPI,SGI是各个core独有的中断,不参与目的core的仲裁,SPI是所有core共享的,根据配置决定中断发往的core。最后选择最高优先级中断发送给cpu interface。寄存器使用 GICD_ 作为前缀。一个gic中,只有一个GICD。

◾cpu interface:将GICD发送的中断信息,通过IRQ,FIQ管脚,传输给core。每一个core,有一个cpu interface。

◾virtual cpu interface:将GICD发送的虚拟中断信息,通过VIRQ,VFIQ管脚,传输给core。每一个core,有一个virtual cpu interface。

(2)、gicv3的组件

◾distributor:SPI中断的管理,将中断发送给redistributor

◾redistributor:PPI,SGI,LPI中断的管理,将中断发送给cpu interface

◾cpu interface:传输中断给core. (实现在core内部的)

◾ITS (Interrupt Translation Service components ):用来解析LPI中断.

4、gic的寄存器

(1)、gicv2的寄存器

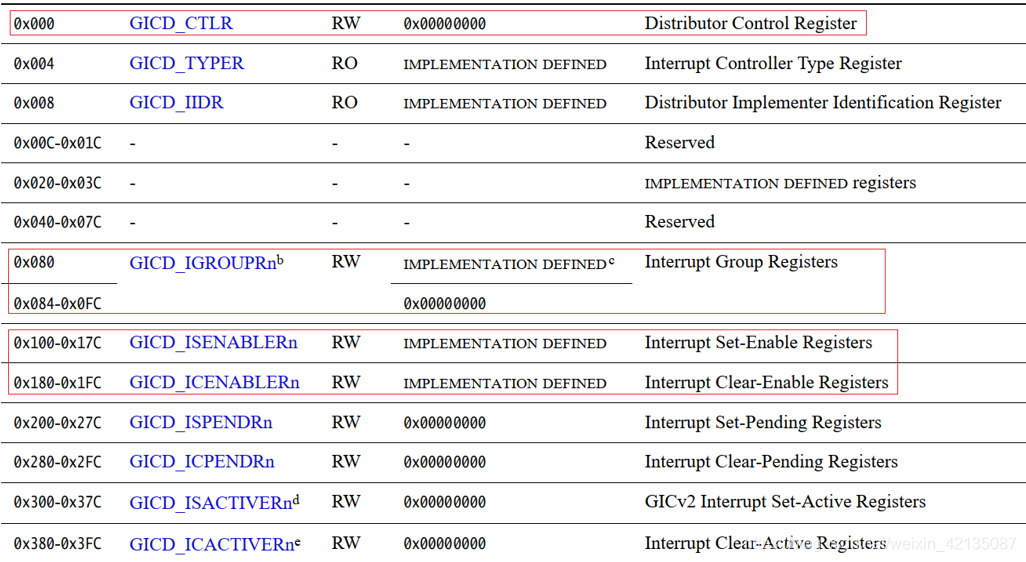

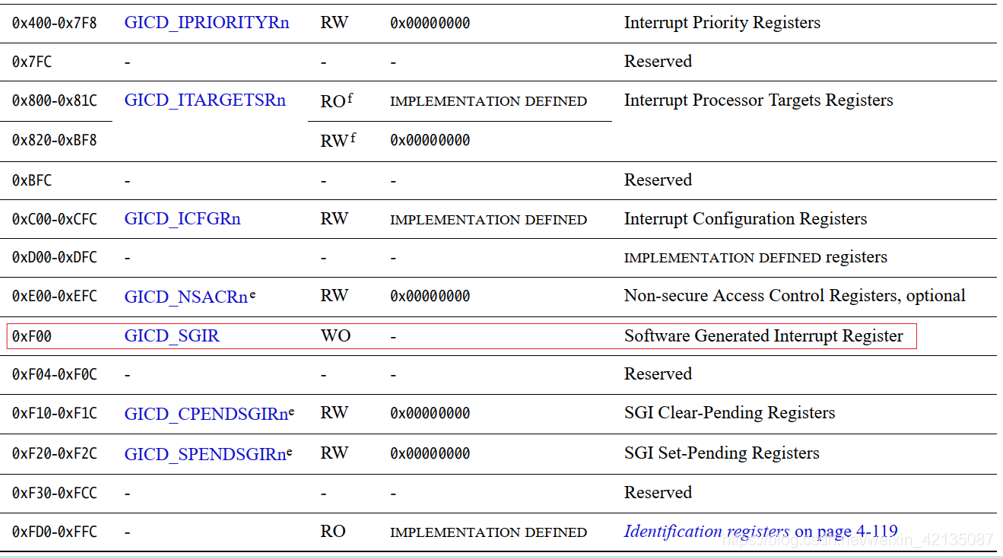

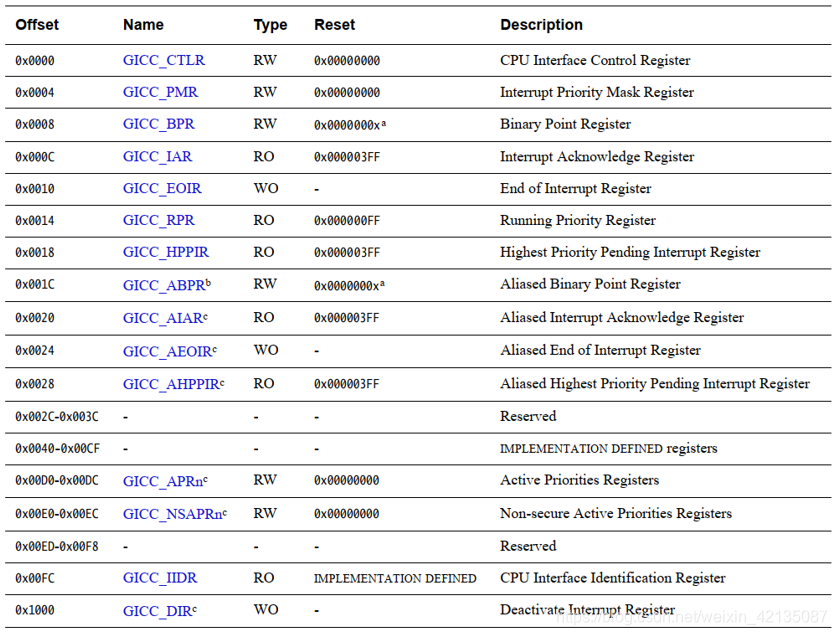

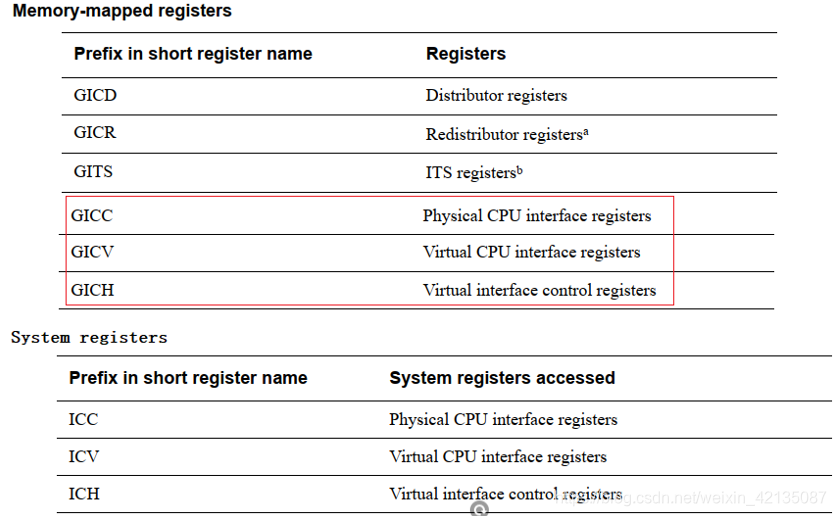

gicv2寄存器,都是使用memory-mapped的方式去访问的

◾GICD_*: distributor的寄存器

◾GICH_*: 虚拟interface的控制寄存器

◾GICV_*:虚拟interface的控制寄存器

◾GICC_*: 虚拟cpu interface的寄存器

Distributor register

0x100-0x17C --- > GICD_ISENABLERn

这个地址范围内一共可以表示32个32bit的寄存器(n=0x7c/4+1)

所以n的值为0-31,共可以表示32*32=1024个中断

cpu interface register

(2)、gicv3

提供了2种访问方式,一种是memory-mapped的访问,一种是系统寄存器访问

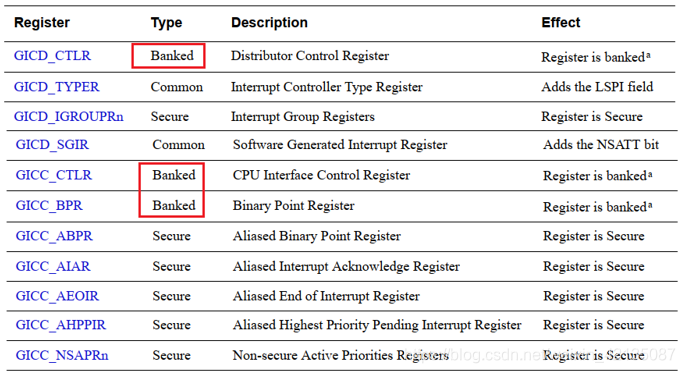

5、Banking registers

什么是banking register?

Register banking refers to providing multiple copies of a register at the same address. The properties of a register access determine which copy of the register is addressed

一个寄存器一个地址,有多份拷贝. 根据寄存器的权限属性来决定访问这个地址的哪个拷贝

gic的banked寄存器有两类:

For Security Extensions, some registers are banked to provide separate Secure and Non-secure copies of the registers.

For multiprocessor system, some registers are banked.

6、gicv3的LPI中断

◾在gicv3中,引入了一种新的中断类型。message based interrupts,消息中断

外设,不在通过专用中断线,向gic发送中断,而是写gic的寄存器,来发送中断。

这样的一个好处是,可以减少中断线的个数,为了支持消息中断,gicv3,增加了LPI,来支持消息中断。并且为他分配了特别多的中断号,从8192开始,移植到16777216

LPI的中断的配置,以及中断的状态,是保存在memory的表中,而不是保存在gic的寄存器中的。

◾GICR_PROPBASER:(64bit)保存LPI中断配置表的基地址

◾GICR_PENDBASER: (64bit)保存LPI中断状态表的基地址

当外部发送LPI中断给redistributor,redistributor首先要查该表,也就是要访问memory来获取LPI中断的配置。为了加速这过程,redistributor中可以配置cache,用来缓存LPI中断的配置信息。

因为有了cache,所以LPI中断的配置信息,就有了2份拷贝,一份在memory中,一份在redistributor的cache中。如果软件修改了memory中的LPI中断的配置信息,需要将redistributor中的cache信息给无效掉。

LPI实现的两种方法:

◾使用ITS,将外设发送到eventID,转换成LPI 中断号

◾forwarding方式,直接访问redistributor的寄存器GICR_SERLPIR,直接发送LPI中断

7、gicv2的bypass功能

GICv2支持中断旁路模式,也就是gic外部的FIQ,IRQ直接接到core的FIQ,IRQ上,相当于gic是不使能的。也就是CFGSDISABLE是有效的,将GIC给无效掉。

gicv2支持bypass功能,这样gic就不起作用了,core的中断管脚,直接由soc的其他部门信号驱动

关注"Arm精选"公众号,备注进ARM交流讨论区。