快速连接

👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈

原理介绍:

废话不多说,看图,看懂的给赞!

内核没有提供指定SPIs中断到特定cpu的接口。那代码我们就胡乱的看一下吧

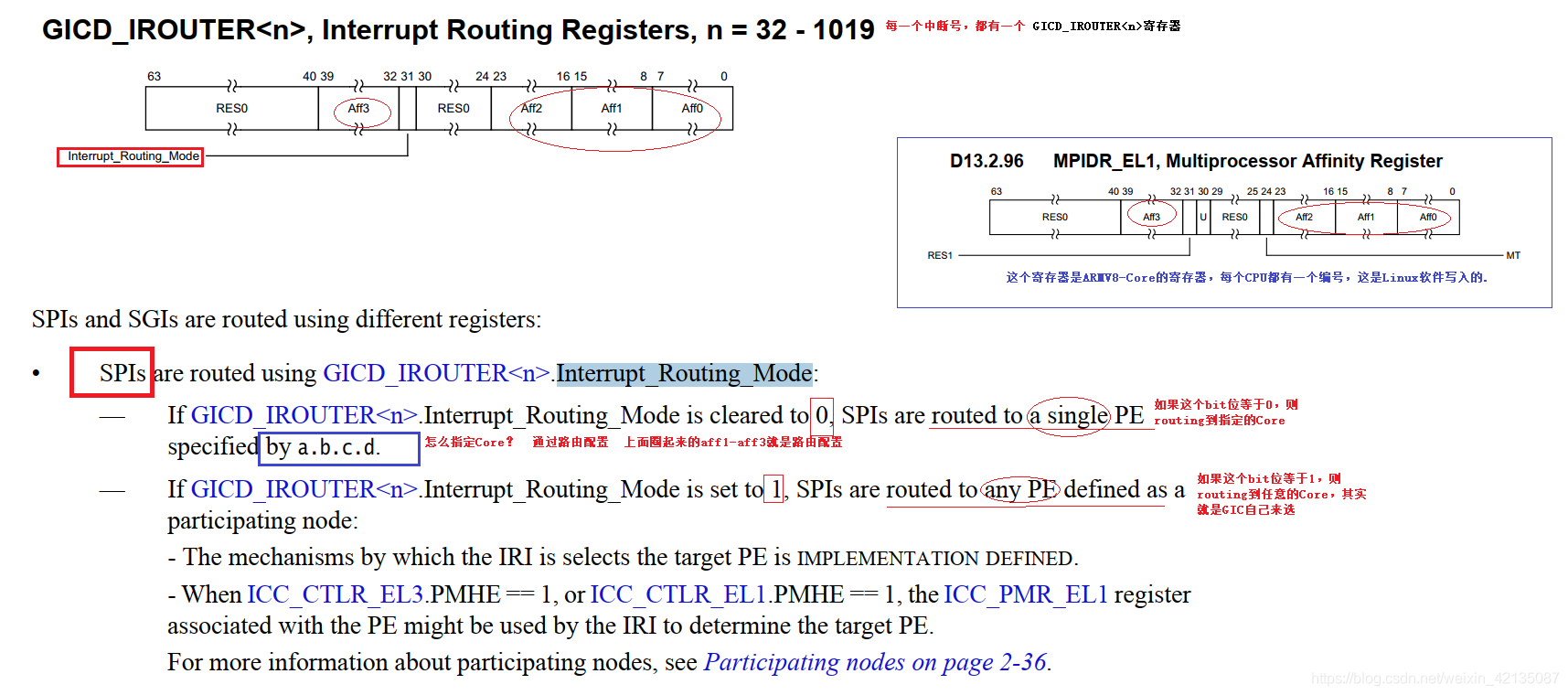

static int gic_set_affinity(struct irq_data *d, const struct cpumask *mask_val,

bool force)

{

unsigned int cpu = cpumask_any_and(mask_val, cpu_online_mask);

struct irq_desc *desc = container_of(d, struct irq_desc, irq_data);

void __iomem *reg;

int enabled;

u64 val;

if (cpu >= nr_cpu_ids)

return -EINVAL;

if (gic_irq_in_rdist(d))

return -EINVAL;

/* If interrupt was enabled, disable it first */

enabled = gic_peek_irq(d, GICD_ISENABLER);

if (enabled)

gic_mask_irq(d);

reg = gic_dist_base(d) + GICD_IROUTER + (gic_irq(d) * 8);

val = gic_mpidr_to_affinity(cpu_logical_map(cpu));

gic_write_irouter(val, reg);

/*

* If the interrupt was enabled, enabled it again. Otherwise,

* just wait for the distributor to have digested our changes.

*/

if (enabled)

gic_unmask_irq(d);

else

gic_dist_wait_for_rwp();

return IRQ_SET_MASK_OK;

}- val = gic_mpidr_to_affinity(cpu_logical_map(cpu)); //读出cpu的id值

gic_write_irouter(val, reg); //将这个值,写入到GICD寄存器

关注"Arm精选"公众号,备注进ARM交流讨论区。