快速连接

👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈

思考:

1、我们知道arm有2个执行状态:aarch32/aarch64,他们之间是如何跳转,如何切换的/

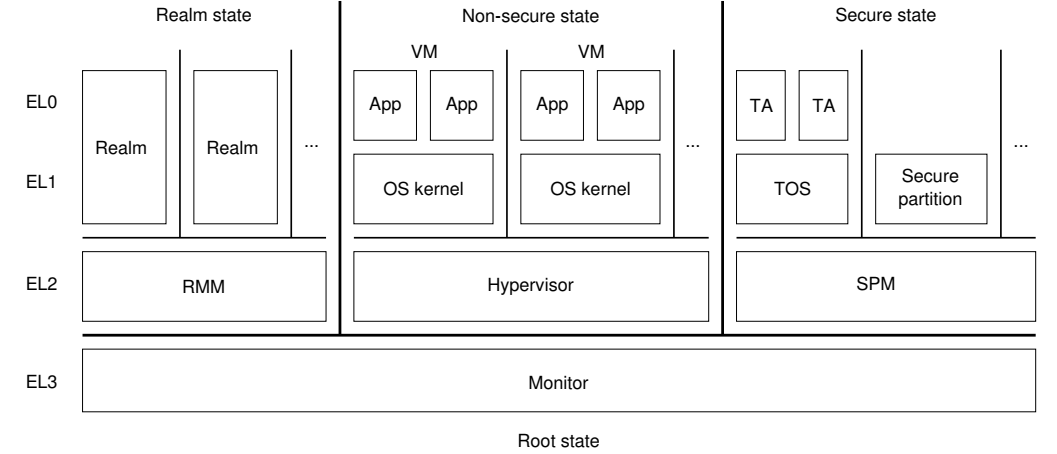

2、我们知道arm有4个安全状态:secure security/non-secure security/ Root/ Realm,他们之间是如何跳转,如何切换的?

3、我们知道arm有4个特权级别:secure security/non-secure security,他们之间是如何跳转,如何切换的?

4、在开机启动是,有着不同的阶段,如bootrom、bootloader、kernel,他们都是64位的? 他们之间都是怎样跳转和切换的?

5、uboot怎样切换到Linux Kernel的?

说明:

1、以下知识点,看似简单和清晰,实则零散在整个10000多页的ARM TRM之中,另外也有许多理论知识在实践中不常见。所以也许会有描述不准确的地方(但但致都是准确的),精确的学习还是请以ARM TRM官方文档为准。

2、本文注重讲解基础原理。实战经验中,真的没办法去说,因为很多SOC厂家会视为他们的启动流程为机密吧,受到NDA保护。

如果你看到了这里 :,那么恭喜你,您已经看到了ARM最最最最精髓的地方了。我早就说过:学习安全其实就是学习ARM架构、学习ARM架构其实就是学习4个特权等级、4个安全状态、2个执行状态之间是如何切来切去的. 本文将详细介绍这些知识点。

1、前言

注意本文标题所说的“程序之间的跳转模型”,主要讲解如下这么样子的大系统大程序之中:

- 启动时镜像之间是如何跳转的

- runtime是镜像之间是如何跳转的

阅读本文需要一点点基础,请自行补习:

- 4个特权等级、4个安全状态、2个执行状态

- 启动模型中的BL1 BL2 BL31 BL32 BL33的概念

2、4个特权等级/4个安全状态之间的跳转模型

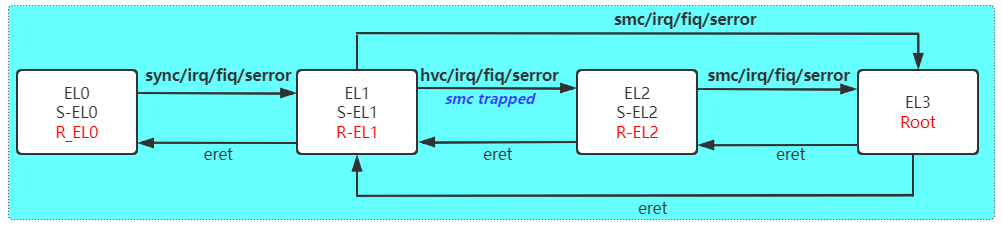

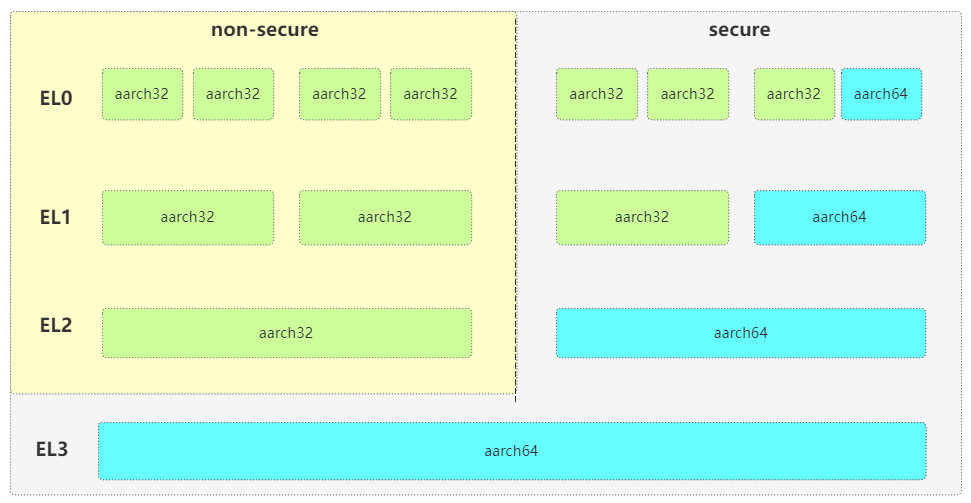

先弄懂最最最基础的本质原理,10000多页的ARM TRM文档散装了很多场景, 我们总结之后再总结,最后浓缩成了下面这一张框图,通常我们也只要理解下面这张图就可以了:

其中:

- EL0的所有异常(同步异常和异步异常)都可以将core切到EL1中

- EL1的所有异步异常、hvc/smc指令 都可以将core切到EL2中

- EL2的所有异步异常、smc指令 都可以将core切到EL3中

- 所有的返回指令,都是ERET

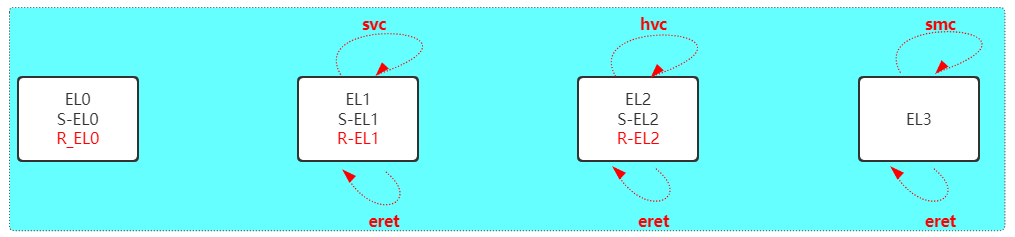

其实呢,下面这种情况也是可以出现的,(只不过呢查略大多数代码,我都没有找到这样使用的例子)

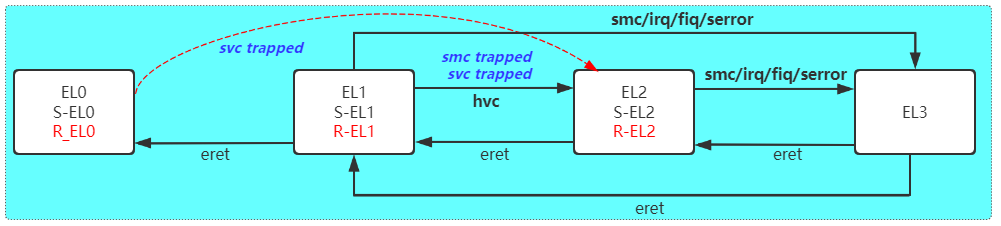

另外呢svc也是可以被trapped到EL2的,EL3调用ERET返回EL1时,也是可以被EL2 trapped的,即下面这种情况也是可以出现的, (只不过呢查略大多数代码,我也没有找到这样使用的例子)

3、启动时镜像之间的跳转模型

由于这些底层的东西,都会和具体的SOC厂家的设计强相关,所以我们也就只好介绍common的场景。

很多人都学习过Secure Boot或是即将学习Secure boot,他们的重点也许都放在了如何签名验签的地方。

那么你知道BL1到BL2是怎样跳转? uboot到kernel是怎样跳转的吗?

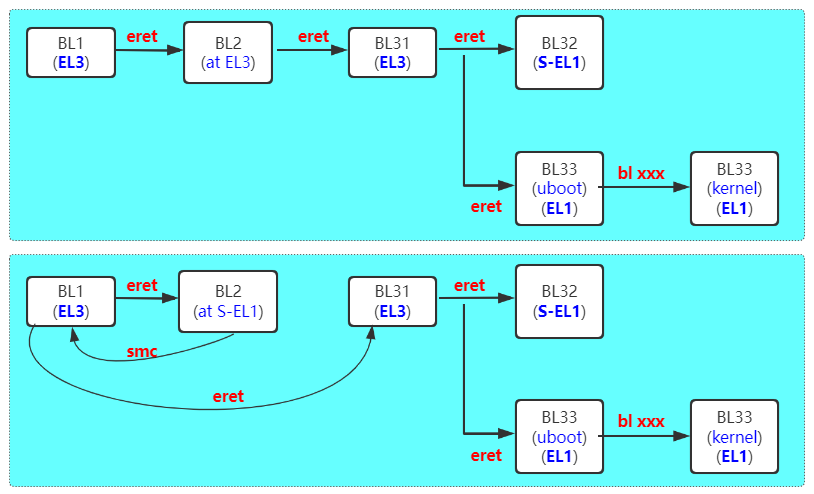

以下是参在TF-A代码做出的总结,当然了也是比较理想的场景:

可是在你的实际使用中:

- BL32可能不是S-EL1,也是有可能是S-EL2的

- BL33可能不是EL1,也是有可能是EL2的

- BL1 BL2 BL33 BL32 BL33 每一级镜像,也许不是aarch64的,也许是aarch32的

如上的场景中,看似也就那么回事吧,无非就是不同特权等级之间,调用同步异常指令或返回指令,切来切去而已。那么如果是相同的特权等级,那么如何切换呢?

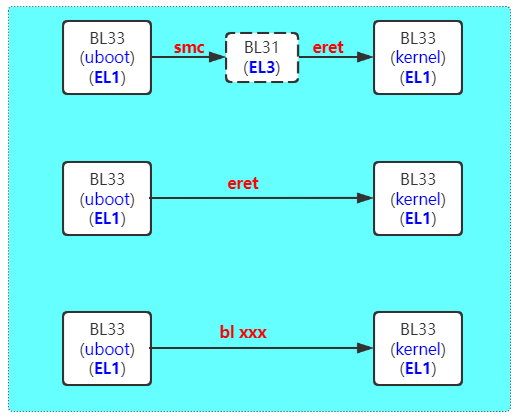

如uboot(EL1)到kernel(EL1), 至少有以下三种方式(其实我还能列出第4种第5种,这里留给大家思考):

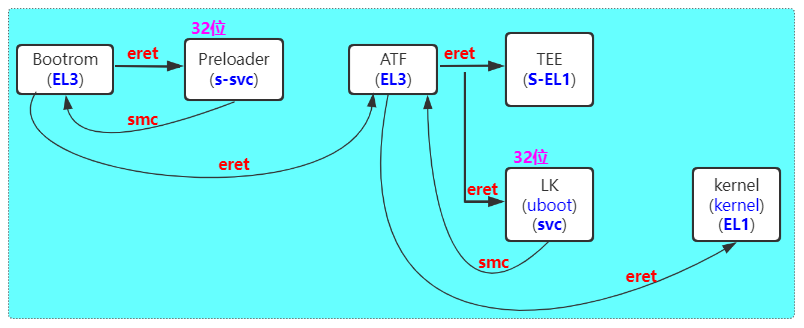

如下再展示了一个稍微复杂的场景,aarch64和aarch32掺杂地使用,也许你的SOC就是这样设计的哦:

4、runtime程序之间的跳转模型

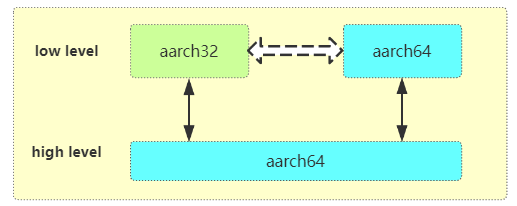

在runtime模型中,你的cpu可能会同时在aarch32和aarch64之间运行,aarch32和aarch64之间的切换,其实也很好理解,模型如下所示,就是进入高特权等级,切换一下cpu context而已。

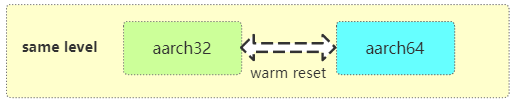

燃鹅,以上依然是最理想的场景吧。在实际使用中,也许你会有各种各样的需求,例如:我不想跳转特权等级,但还想切换执行状态。

比如你的SOC实现定义了EL3,你的EL3既aarch32的程序,也有aarch64的程序,那么两个程序是如何切换的呢?

这个时候,利用同步异常/异步异常的知识点已经无法满足需求了,可能就得利用架构中的warm reset技术了。

例如,你可以在aarch32的程序中去写RMR_EL3的相关比特,触发warm reset, cpu复位进入提前设置好的RVBAR_EL3的地址出,进入aarch64程序。 其实还真有很多厂家,使用这种方式完成的镜像之间的跳转。

关注"Arm精选"公众号,备注进ARM交流讨论区。