快速连接

👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈

背景:为什么会有执行状态的切换

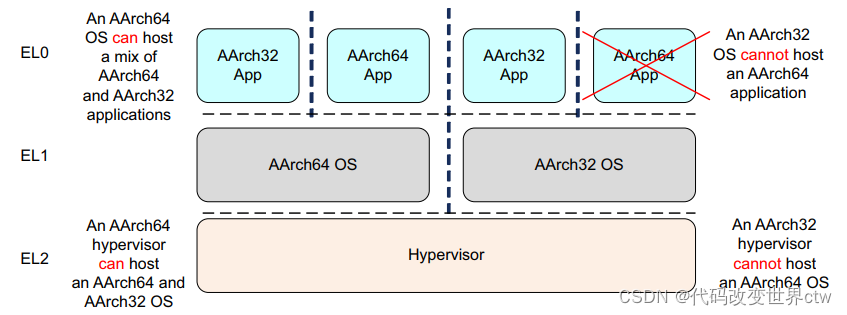

在一个大系统中,我们所说这它是64位的,还是32位的,往往说的是kernel内核。事实上,在这么的一个大系统中,有着多级镜像,并非全都是64位的,也并非全都是32位的。如下一张图,便展示了某SOC系统中常用的一个执行状态

Interprocessing :执行状态切换

术语:AArch64和AArch32执行状态之间的交互称为interprocessing。

ARMV8/ARMV9的执行状态(Execution state) 有两种:aarch64和aarch32,它们的切换的方式只有两种:

- (1) reset

- (2) changing Exception level

它们的切换规则是:

- aarch32到aarch64的切换,必需是触发异常,产生的low exception level 到 high exception level的切换。

- aarch64到aarch32的切换,必需是异常返回,产生的high exception level 到 low exception level的切换。

- 在 exception level不变的情况下,产生的异常和异常返回,都不能改变excution state.

再简而言之,总结起来其实就是:

- high exception level如果是aarch64,那么low exception level 可以是aarch64或aarch32

- high exception level如果是aarch32,那么low exception level 只能是aarch32

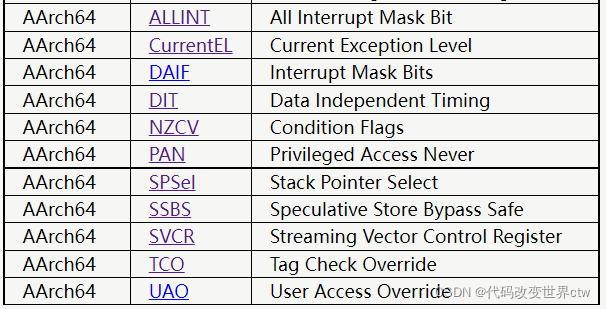

寄存器介绍

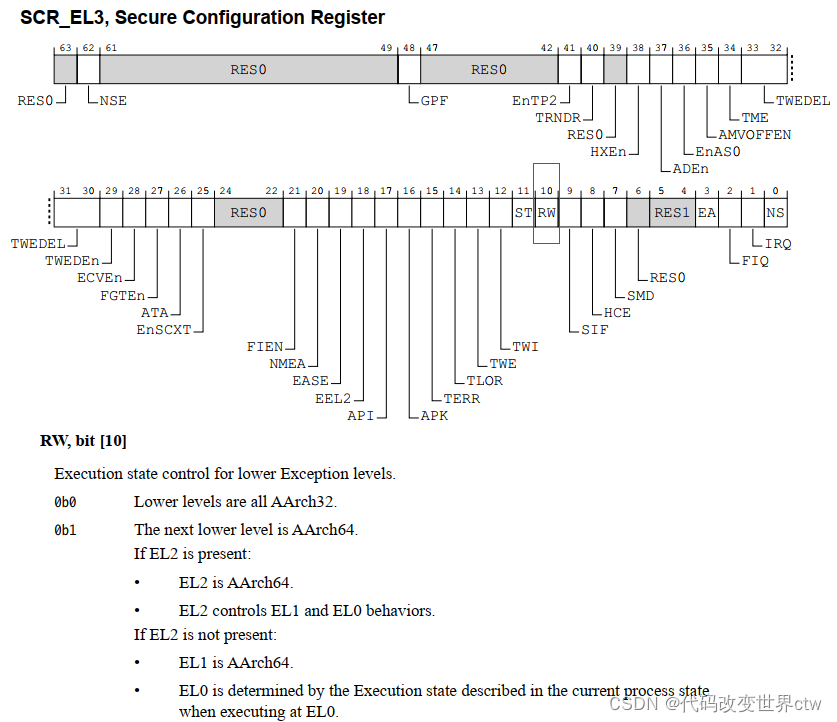

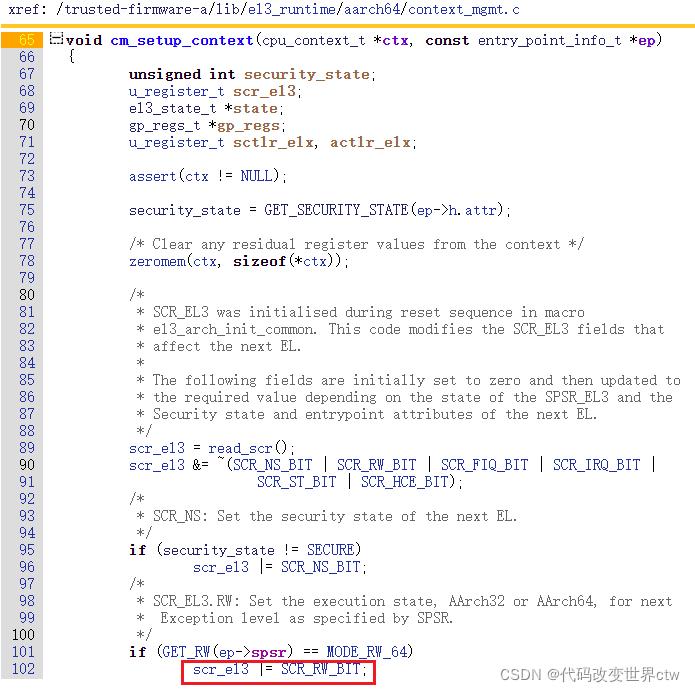

SCR_EL3

如果实现了EL3,那么PE复位后将直接是aarch64.SCR_EL3.RW 将决定着lower exception level的执行状态

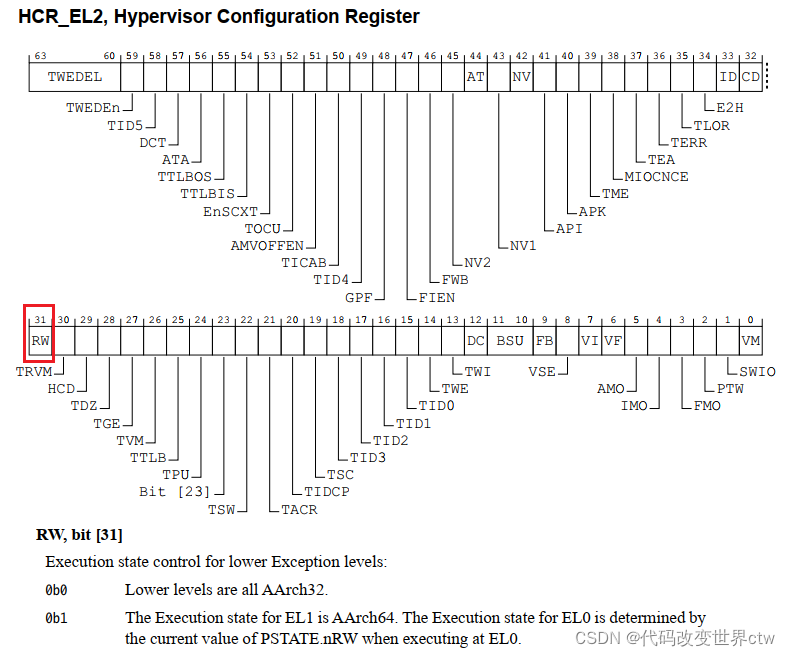

HCR_EL2

如果实现了EL2,且EL2的执行状态是aarch64.HCR_EL2.RW 将决定着EL1的执行状态

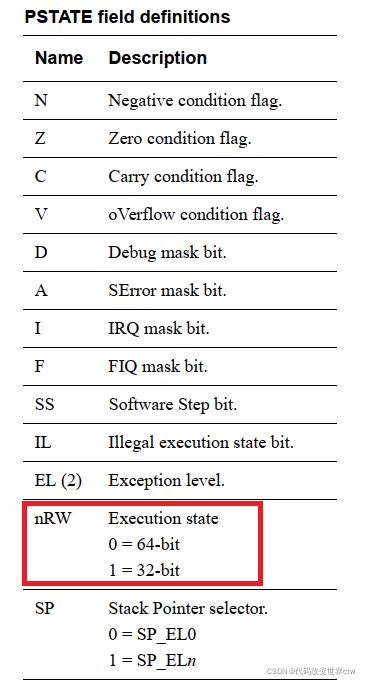

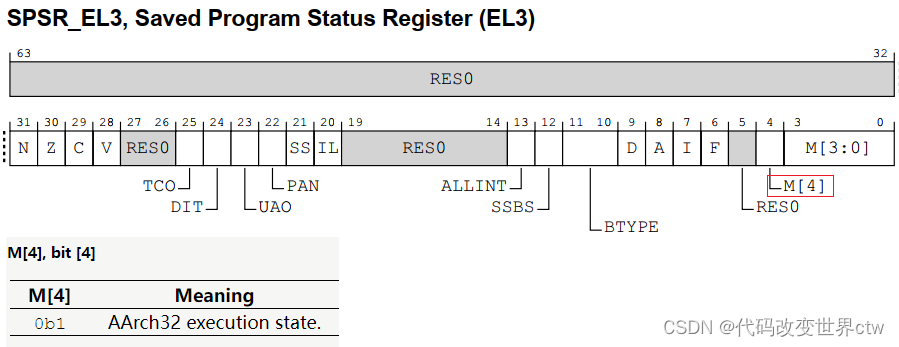

PSTATE和SPSR_ELx

如果EL1是aarch64,那么SPSR_EL1.M[4] 将决定着EL0的执行状态

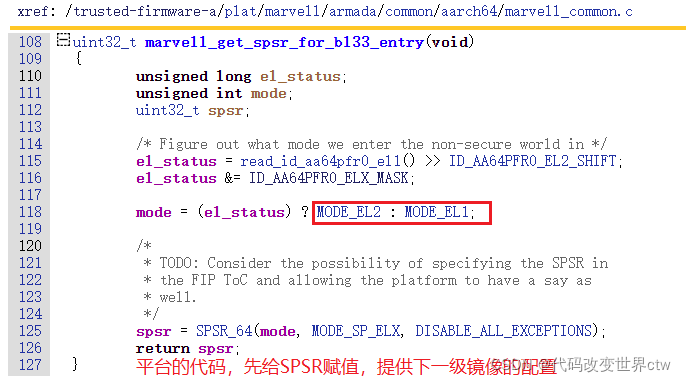

代码导读

关注"Arm精选"公众号,备注进ARM交流讨论区。