快速连接

👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈

思考:

如果硬件是这种连接cpu-->tzc-->dmc-->ddr, 那么配置某块region对cpu的nsaid权限后,cpu再次读写该region范围的内存时,cache中已经缓存了该数据,那么这个数据流在cache中就完成了,不会经过TZC,那么是怎么保证安全的呢?

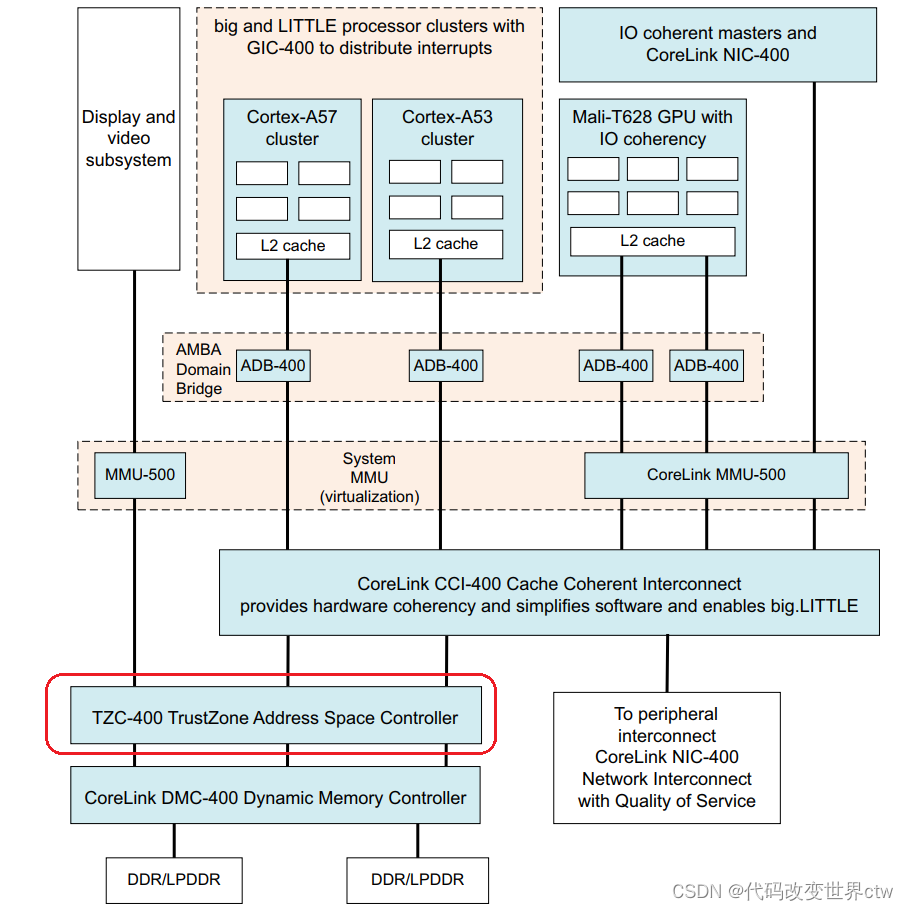

1、系统架构图

我们先看一张系统架构图,了解一下TZC400的作用或位置,其实就是下core和DDR(DMC)之间,添加了一个TAC, 其作用其实就是memory Filter。

2、tzc400的硬件框图

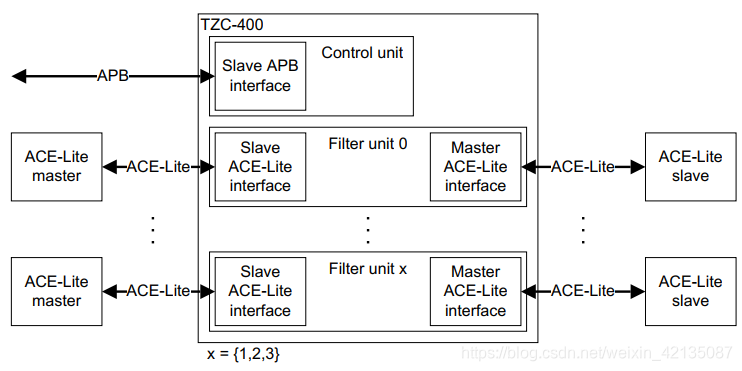

从图中可以看出

- apb接口 : 用于cpu读写tzc-400的寄存器;

- ACE-Lite接口 : TZC400的通过ACE-Lite接口接到Master和DDR中间,

对Master访问DDR进行filter控制 : 一块TZC400支持0-x个filter,x一般是1、2、3 - 也就是说,tzc400中,有一个control unit单元、x个filter unix单元;

- 一个TZC400,支持9个region(包含region0)

那么最多支持4个Filter和最多支持9个region, Filter和Region到底是什么关系呢?

什么关系都不是!!!

Filter就是Filter,Region就是Region,无论您是几个Filter,一个TZC最多只支持9个region。

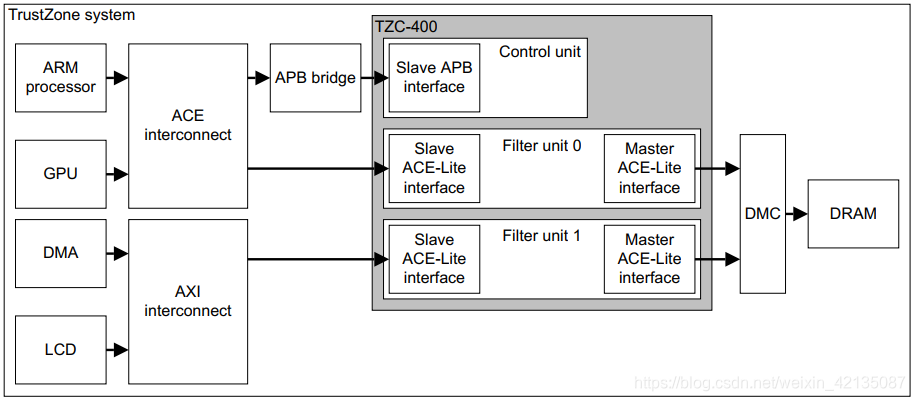

因为有着不同类型的Master,都需要连接到TZC上,所以才需要的多个Filter。 如下图所示便有一个示例:

- Core和GPC 通过ACE接口与Filter0相连

DMA/LCD 通过AXI接口与Filter1相连

3、FPIDs and NSAIDs

对应每一个filter unit, TZC400提供了两种identity path :FPIDs和NSAIDs

- Fast Path IDentity

Non-secure Access IDentity

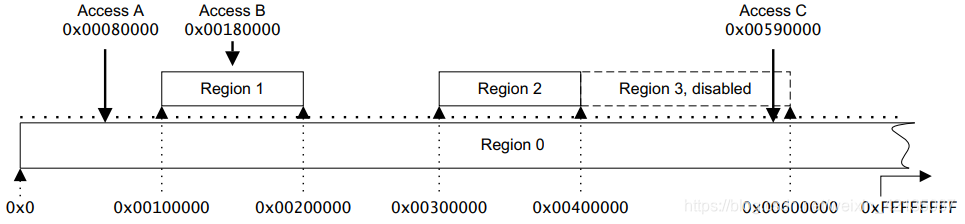

4、region setup

Region 0 永远是enable的,整块DDR中未设置region的区域,都属于region 0.

建立一块region,需要配置:Top address、Base address、Region enables、Secure access permissions、Non-secure ID filtering

region的overlap规则:

- 不在Regionx(x=1-8)范围内的地址,属于region0

- 在同一个Filter中,Regionx(x=1-8)不能有互相覆盖的情况,

如果进行了overlap的配置,那么当访问该地址时,将产生一个中断,暗示 overlapping access - 不同Filter中的Regionx(x=1-8)可以相互overlap

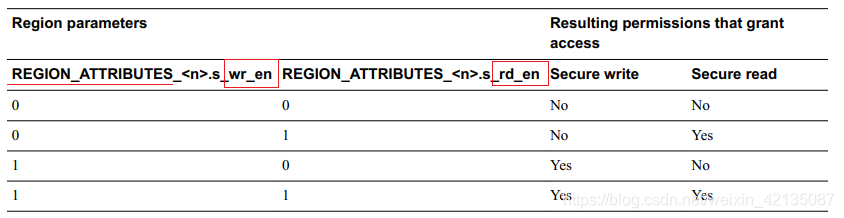

secure access permissions的权限参见 region_attributes寄存器

nsaid权限访问的路由规则 : 先检查Master的身份,若是secure发起的访问,则去检查Secure access permissions, 如果是non-secure发起的访问,则取检查nsaid权限

5、NSAID

对于Non-Secure的访问,NSAID从何而来?

其实如果是Non-Secure发起的访问(NSAccess_Identifiers为True),那么AWNSAID 和 ARNSAID的接口就必需提供.

- 如果Master支持nsaid,那么它会自动提供AWNSAID 或ARNSAID,

- 如果Master不支持nsaid,那么可以在SOC设计的时候,在系统寄存器种增加NSAID标志位,该Master发起读写时,则自动传送相关NSAID value

如下是AMBA-AXI总线协议中nsaid相关的bit位

与之对应的TZC400接口,每个Filter都有NSAIDR0[3:0]、NSAIDW0[3:0]、NSAIDRx[3:0]、NSAIDWx[3:0]、

关注"Arm精选"公众号,备注进ARM交流讨论区。