快速连接

👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈

1、DBG、DMB、DSB 和 ISB指令介绍

调试指令、数据内存屏障指令、数据同步屏障指令和指令同步屏障指令。

语法

- DBG{cond} {#option}

- DMB{cond} {option}

- DSB{cond} {option}

- ISB{cond} {option}

cond : 是一个可选的条件代码(请参阅条件执行)。

option : 对提示操作的可选限制。

说明:如果指令未实现,则与 NOP 效果相同

- (1)、DBG : 调试提示可向调试系统及其相关系统发送提示。

(2)、DMB :数据内存屏障可作为内存屏障使用。 它可确保会先检测到程序中位于 DMB 指令前的所有显式内存访问指令,然后再检测到程序中位于 DMB 指令后的显式内存访问指令。它不影响其他指令在处理器上的执行顺序

option 的允许值为:SY, 完整的系统DMB 操作。 这是缺省情况,可以省略

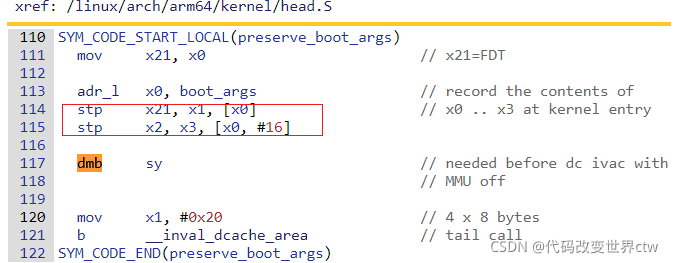

举个例子: 如下的操作,确保dmb之前的内存访问已经完成了,即数据读到了x1、x2、x3、x21,然后后面的inval_dcache_aera会使用这些参数。

(3)、DSB : 数据同步屏障是一种特殊类型的内存屏障。 只有当此指令执行完毕后,才会执行程序中位于此指令后的指令。 当满足以下条件时,此指令才会完成:

位于此指令前的所有显式内存访问均完成。

位于此指令前的所有缓存、跳转预测和 TLB 维护操作全部完成允许的值为:

SY : 完整的系统 DSB 操作。 这是缺省情况,可以省略。

UN : 只可完成于统一点的DSB 操作。

ST : 存储完成后才可执行的DSB 操作。

UNST : 只有当存储完成后才可执行的DSB 操作,并且只会完成于统一点(4)、ISB : 指令同步屏障可刷新处理器中的管道,因此可确保在 ISB 指令完成后,才从高速缓存或内存中提取位于该指令后的其他所有指令</font>。这可确保提取时间晚于 ISB 指令的指令能够检测到 ISB 指令执行前就已经执行的上下文更改操作的执行效果,例如更改ASID 或已完成的 TLB 维护操作,跳转预测维护操作以及对 CP15 寄存器所做的所有更改。

此外,ISB 指令可确保程序中位于其后的所有跳转指令总会被写入跳转预测逻辑,其写入上下文可确保 ISB 指令后的指令均可检测到这些跳转指令。这是指令流能够正确执行的前提条件。

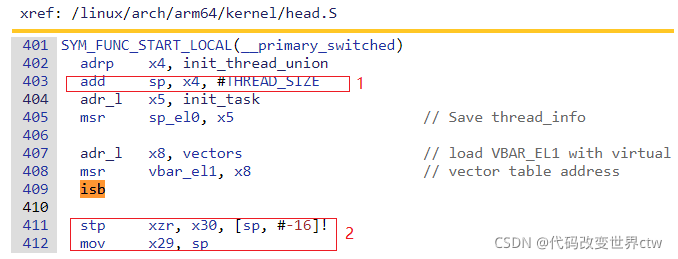

举个例子:如果上述代码中1和2处的之类,同时从icache中取的,那么2处位置sp的值感测不到1处对sp的修改。那么有了isb之类后,保证1处操作完成之后,再进行2处取指令,这样就不会乱了。

2、Linux Kernel中的smp_mb()、smp_rmb()、smp_wmb()、mb()、wmb()、rmb()

smp_mb()、smp_rmb()、smp_wmb()在底层调用的都是dmb

#define __smp_mb() dmb(ish) #define __smp_rmb() dmb(ishld) #define __smp_wmb() dmb(ishst) #ifndef smp_mb #define smp_mb() __smp_mb() #endif #ifndef smp_rmb #define smp_rmb() __smp_rmb() #endif #ifndef smp_wmb #define smp_wmb() __smp_wmb() #endif

mb()、wmb()、rmb()在底层调用的也都是dmb

#define mb() asm volatile("dmb ish" ::: "memory")

#define wmb() asm volatile("dmb ishst" ::: "memory")

#define rmb() asm volatile("dmb ishld" ::: "memory")问:smp_mb()、smp_rmb()、smp_wmb() 和 mb()、wmb()、rmb()到底有什么区别吗

关注"Arm精选"公众号,备注进ARM交流讨论区。