在进行后仿真时,经常会看到工具反标时提示存在负延迟,并且这些负延迟经常出现在 SETUP、HOLD、INTERCONNECT 和 IOPATH 中。出现负延迟的原因很多,除了路径以外,还跟串扰(crosstalk)和噪声(noise)有关,下面我们就简要聊叙下这四种负延迟到底怎么回事。

1 HOLD

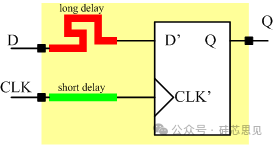

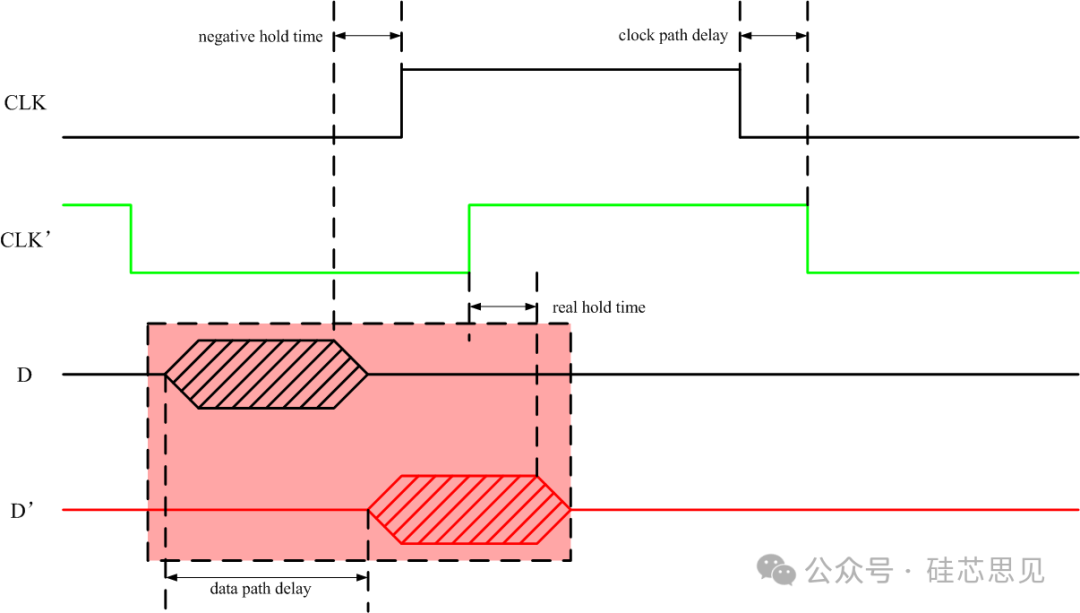

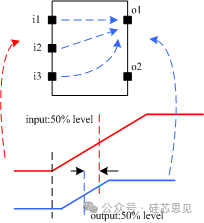

为了说明问题,我们以以下触发器模型(内部主要由锁存器构成)说明标准单元的负延迟。当 D 从 pin 到锁存器的延迟大于 CLK 从 pin 到锁存器 CLK’端的延迟,那么就可能出现下面的情况:在电路外观测到的 D 虽然出现在 CLK 之前(hold 为负值),但是经过电路内延迟后,由于 D 到达锁存器 D’的延迟大于 CLK 到达 CLK’的延迟,在锁存器端口 D’就会出现在 CLK’跳边沿两侧的情况,即此时 CLK’采样数据 D’时,其 hold 值为正值。因此,其实 hold 为负值是针对 pin 端而言,也就是触发器外部而言。如下图所示:

2 SETUP

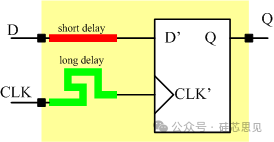

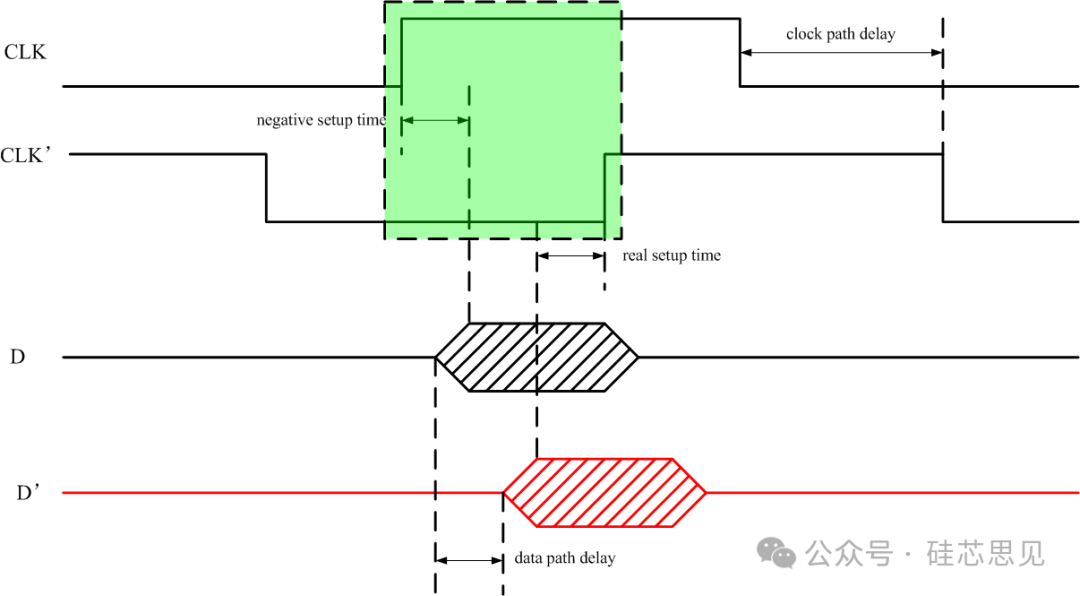

当 D 从 pin 到锁存器的 D’延迟小于 CLK 从 pin 到锁存器 CLK’端的延迟,那么就有可能会出现如下情况:在电路外观测到的 D 虽然出现在 CLK 之后(setup 为负值),但是经过电路内延迟后,由于 D 到达锁存器 D’的延迟小于 CLK 到达 CLK’的延迟,在锁存器端口 D’就会出现在 CLK’跳边沿两端,即此时 CLK’采样数据 D’时,其 setup 实际上是正值。其实 setup 为负值是针对 pin 端而言,也就是触发器外部而言。

3 IOPATH

IOPATH 描述每个单元(如逻辑门等)从输入引脚到输出引脚的延迟。属于逻辑单元内部延迟,由器件的物理特性所主导,并且随着工艺的进步,其时序特性也会得到改善。IOPATH 为负值的原因实际上就是在电平转换过程中,虽然输出的变化起始于输入变化之后,但输出可能会比输入先到达阈值电压,从而形成负延迟。影响 IOPATH 产生负延迟的主要原因有:

- 晶体管开关速度、内部 RC 等物理特性;

- 输出端连接的负载,负载很小时,可能会导致负载电压先达到阈值;

- 工艺水平直接会影响到晶体管的导通速度和延迟;

- 输入信号的斜率(Slew),也就是输入信号的 transition time,输入信号的上升和下降时间;

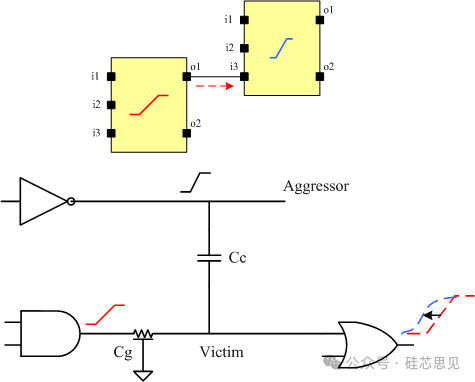

4 INTERCONNECT

INTERCONNECT 描述了从驱动单元的输出引脚到被驱动单元输入引脚之间的连线延迟。属于逻辑单元之间的延迟,有布局布线和 RC 参数主导。INTERCONNECT 负延迟一般由于串扰(crosstalk)引起,在分析 crosstalk 时,受影响的信号我们称之为 victim,施加影响的信号称之为 aggressor。影响负延迟的因素主要有:

- RC 延迟,即信号传输延迟;

- 导线长度,导线越长,延迟越大;

- 在先进工艺条件下,导线的宽度和导线间距会对电阻和耦合电容产生显著影响;

- 布局布线时线间的互相屏蔽等;

5 负值处理示例

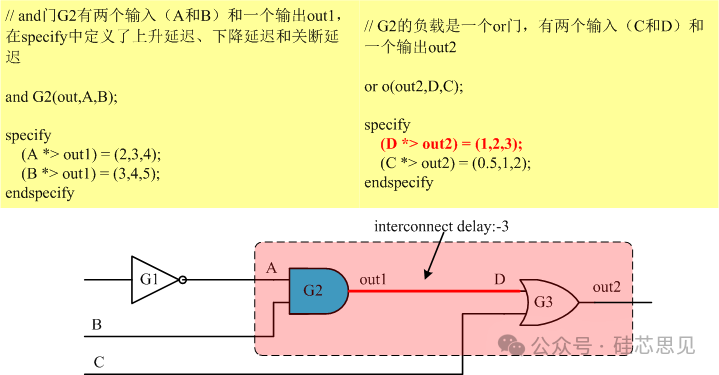

5.1 INTERCONNECT 负值处理

标时,工具会对关联的 interconnect 和 iopath 进行计算(要求 interconnect+iopath >= 0),如下例:

示例中,iopath 选取 G2 中最小的 iopath 延迟或者最大可调整幅度(最大延迟-最小延迟),本例中为+2,因为 interconnect 为-3,所以“+2-3=-1<= 0”,不满足 interconnect+iopath >= 0,产生的“剩余延迟”-1 需要补偿掉,此时工具会使用最后一级逻辑单元 G3 的 IOPATH 延迟进行补偿,此时通过 G3 的 D 端对应的 IOPATH 延迟的补偿后,interconnect+iopath >= 0,所以此时工具会给出“负值调整成功的信息(不同工具给出信息可能不同)”,如果 G3 的 IOPATH 延迟不能补偿“剩余延迟”,则工具会提示将“剩余延迟”清零。

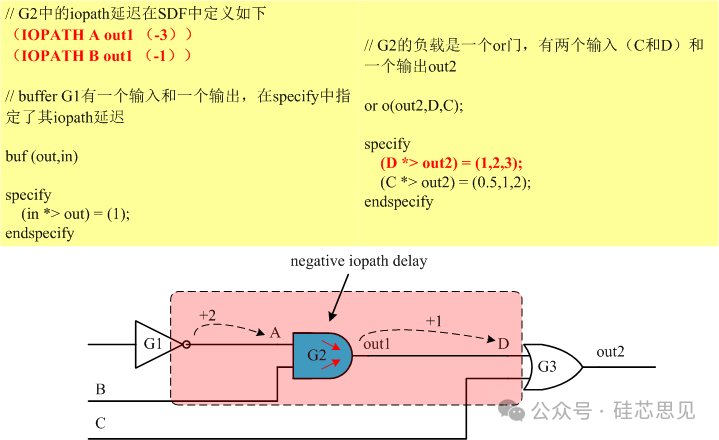

5.2 IOPATH 负值处理

示例中,选取 G2 中的 A->out1 路径的 IOPATH 延迟,延迟值为-3。对于该延迟,工具首先会根据连接 A 端的 INTERCONNECT 延迟进行调整,interconnect+iopath =+2-3=-1=<0,不满足 interconnect+iopath >= 0,然后工具会根据 G2 负载端的 INTERCONNECT 进行时间调整,因为此时 G2 负载端的 INTERCONNECT 为+1,可以补偿掉“剩余延迟”-1,满足 interconnect+iopath >= 0,所以此时工具会给出“负值调整成功的信息(不同工具给出信息可能不同)”,如果负载端的 INTERCONNECT 不能补偿掉“剩余延迟”,则工具会提示将“剩余延迟”清零。

END

作者:nanoty

文章来源:硅芯思见

推荐阅读

- cocotb 仿真加速——合并

- 手把手教你从零设计一款算力超过 1000Tops 的智能驾驶芯片

- 深入了解 PCIe 协议

- 当机器人学会扫堂腿:一场踢向万亿市场的芯片机遇

- 递归设计:高效实现前导 0 计算电路

更多 IC 设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。