半导体技术已经成为推动科技发展的核心动力,从手机到超级计算机,从自动驾驶汽车到人工智能系统,芯片的性能、功耗和成本直接影响着整个行业的创新速度。

摩尔定律的放缓,传统的单片集成方式已经难以满足日益增长的计算需求。芯片模块化(Chiplets)作为一种新兴的技术范式,正迅速崛起为推动计算架构革新和产业变革的核心力量。

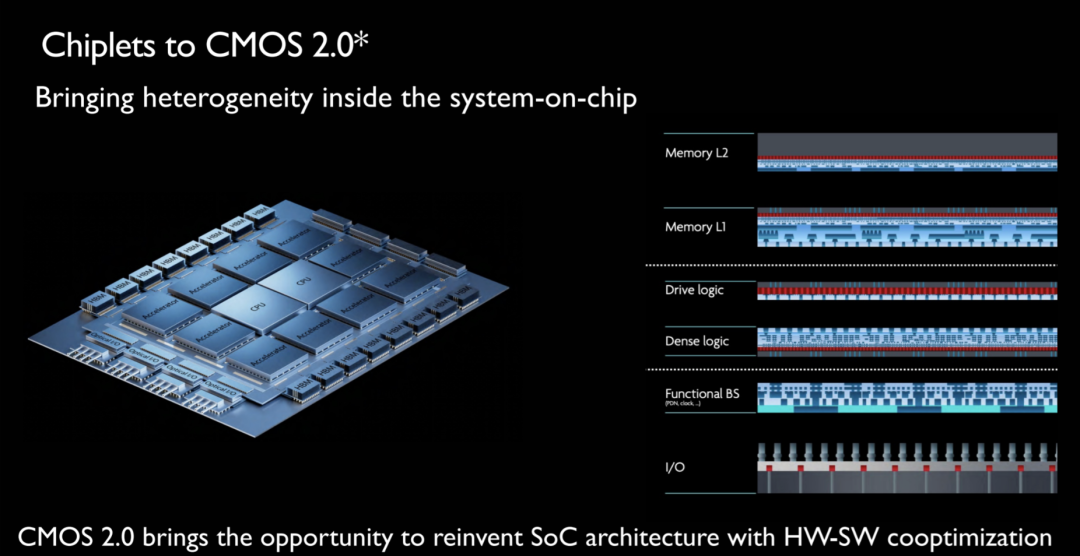

随着摩尔定律逐渐放缓,传统单片集成芯片在性能、成本和功耗等方面面临严峻挑战,而 Chiplet 技术通过将复杂系统分解为多个独立模块,提供了全新的解决方案,Chiplet 技术如何重塑计算架构并推动产业向 CMOS 2.0 时代迈进。

Part 1.Chiplet 技术的背景与优势

半导体行业数十年来依赖摩尔定律,通过不断缩小晶体管尺寸实现性能提升和成本降低。

● 随着工艺节点接近物理极限(如 3nm 以下),摩尔定律的步伐显著放缓,传统单片集成芯片(Monolithic Die)设计面临多重困境:

◎ 制造成本激增:随着工艺节点的缩小,光刻设备的复杂性和制造成本呈指数级增长。例如,从 7nm 到 3nm,每平方毫米的制造成本可能增加 50%以上。

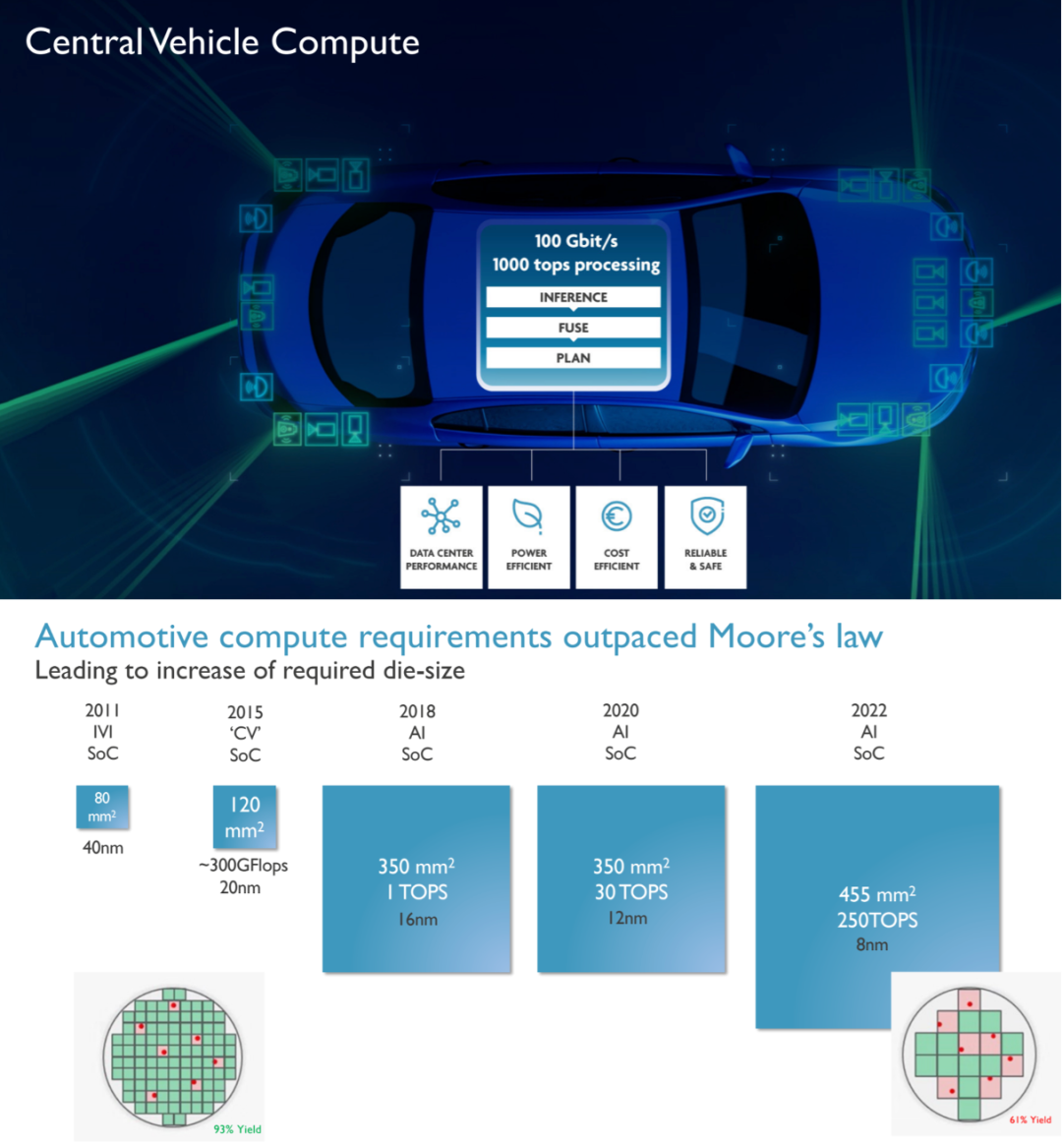

◎ 良率问题:芯片尺寸越大,制造过程中的缺陷率越高,导致良率下降。以 14nm 工艺为例,300 平方毫米的芯片良率可能高达 90%,而 500 平方毫米时可能降至 60%以下。

◎ 性能瓶颈:单片芯片受限于光刻技术的极限(Reticle Limit),无法无限扩展面积,导致性能提升受阻。

◎ 功耗挑战:为追求更高性能,芯片功耗显著增加,散热设计成为移动设备和数据中心的关键难题。

● Chiplet 技术的出现为这些问题提供了突破口。

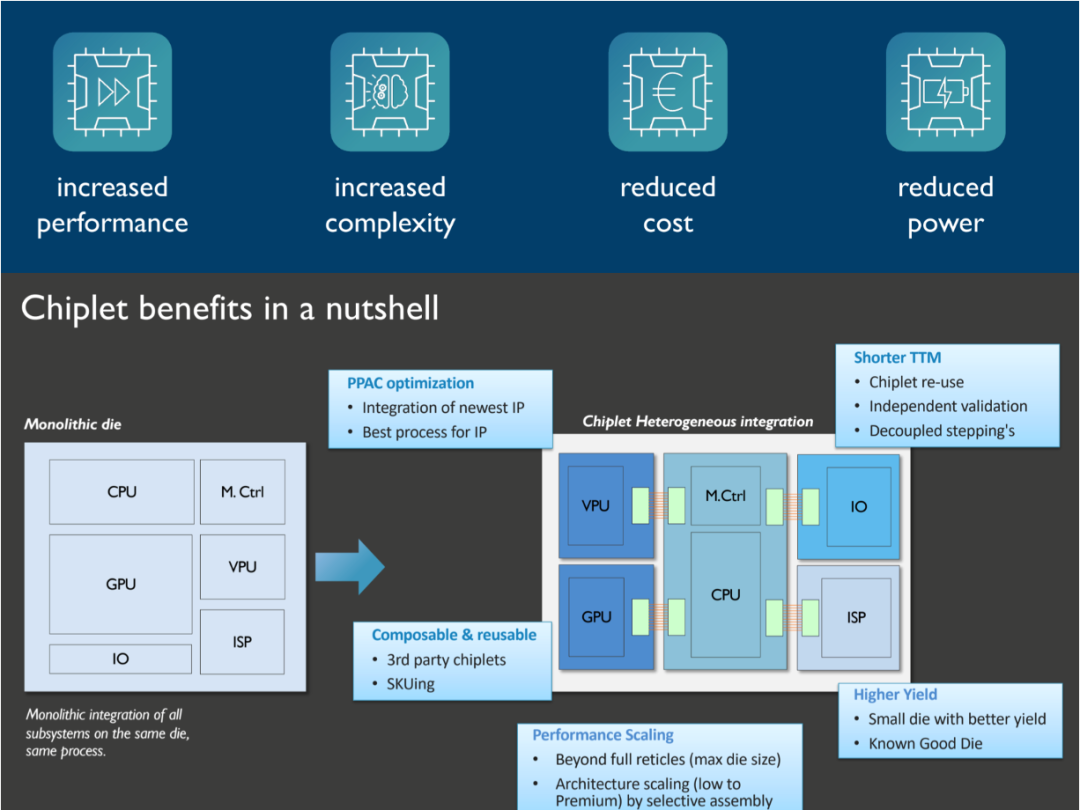

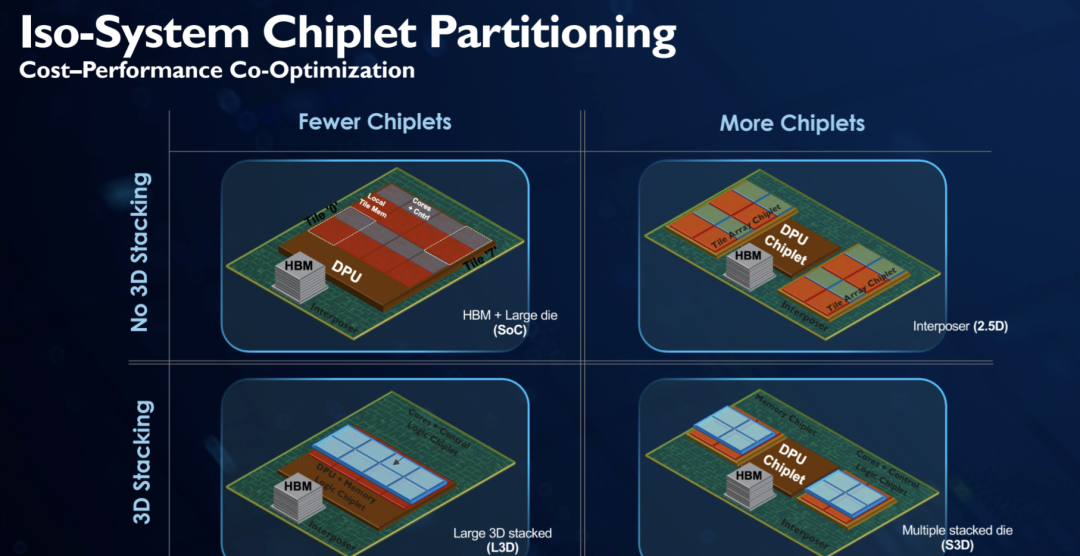

Chiplet,即“小芯片”,将传统单片芯片的功能分解为多个独立模块,每个模块可单独设计、制造和测试,最终通过先进封装技术(如 2.5D 中介层或 3D 堆叠)集成。这种模块化设计不仅降低了制造难度,还提升了设计灵活性和系统性能。

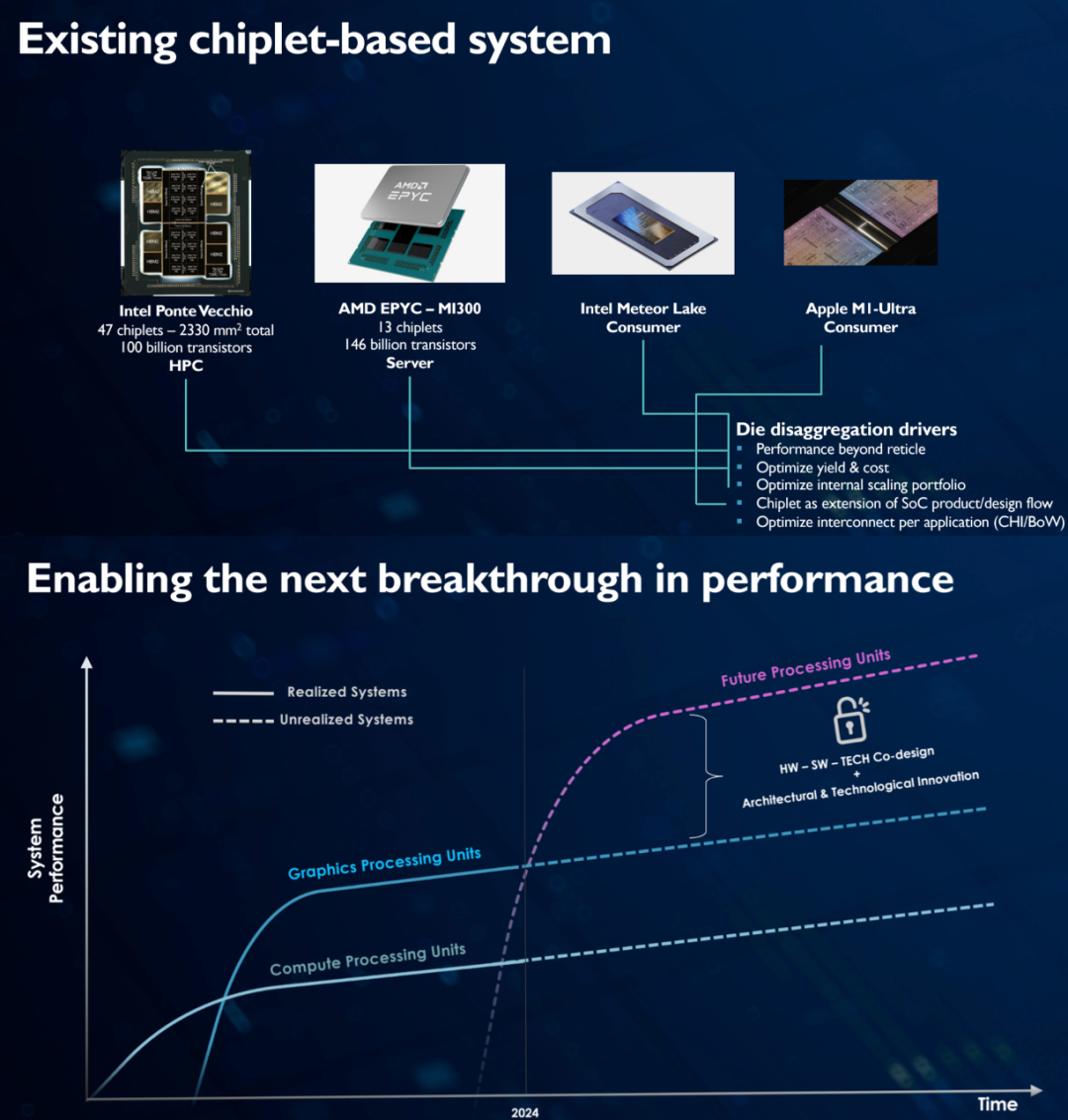

◎ 在性能扩展性方面,通过采用模块化设计,Chiplet 技术成功突破了单片芯片的面积限制,例如英特尔的 Ponte Vecchio 芯片,它集成了多达 47 个模块,总面积达到 2330 平方毫米,容纳了 1000 亿个晶体管,大大超越了传统单片芯片的集成度。

◎ 上市时间(TTM)得到了优化,由于模块可以并行开发,缩短了整体研发周期,如 AMD 的 EPYC 系列利用 Chiplet 设计将产品上市时间减少了大约 30%。

◎ 此外,对于成本与良率优化而言,小尺寸模块制造的高良率相较于大面积单片芯片具有明显优势,以 5nm 工艺为例,100 平方毫米模块的良率可达 85%,而 400 平方毫米的单片芯片良率可能低于 50%,有效降低了生产成本。

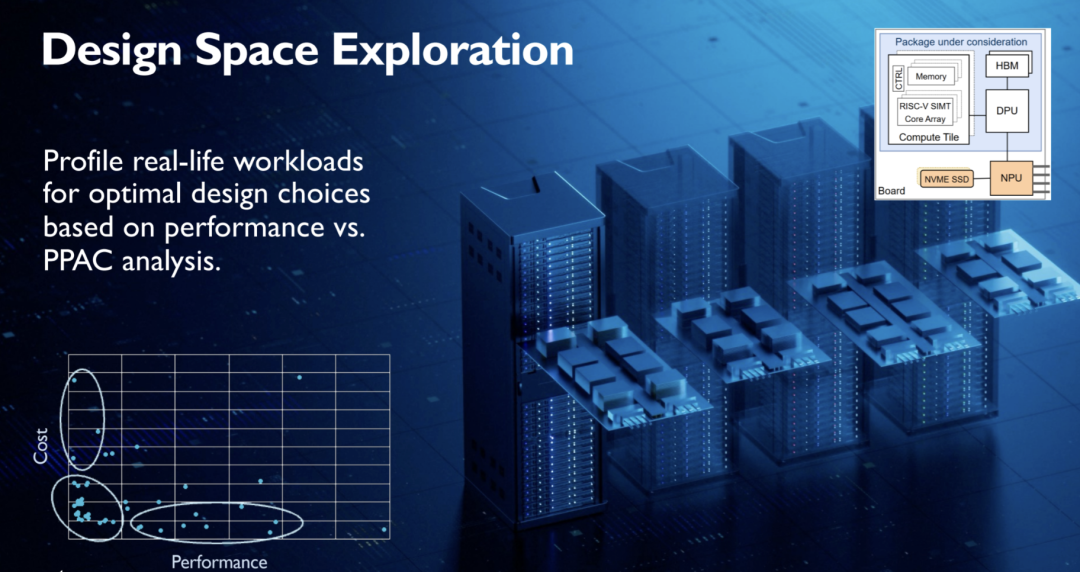

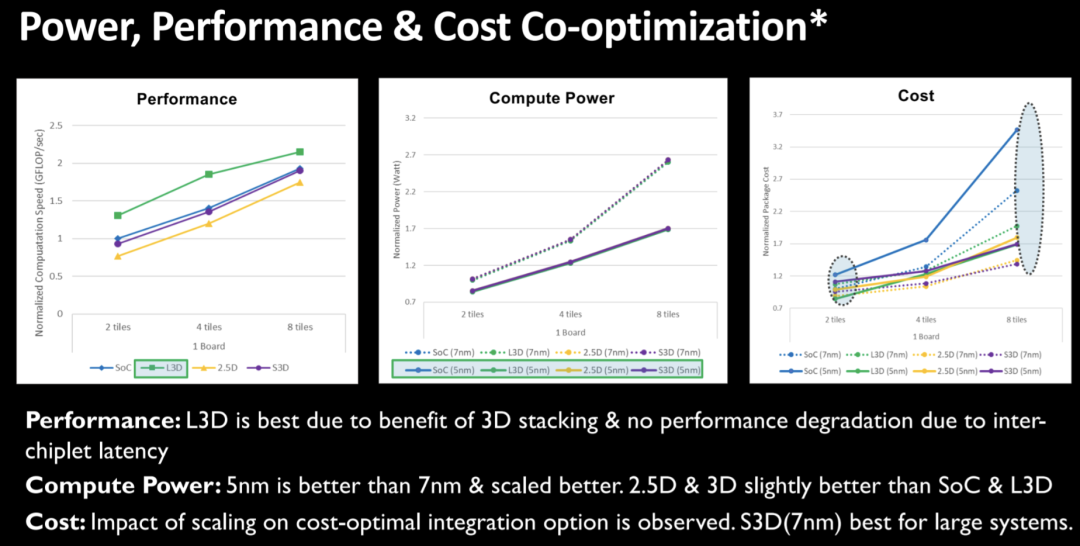

◎ Chiplet 技术在 PPAC(性能、功耗、面积、成本)综合优化上也表现出色,允许不同功能模块选择最适合其特性的工艺节点,比如计算模块选用 5nm 工艺提升性能,I/O 模块则使用更为成熟的 12nm 工艺降低成本。

◎ 最后,设计灵活性与 IP 复用方面,模块化设计使得快速集成最新知识产权(IP)成为可能,并通过标准化接口实现模块间的高效复用,像英特尔的 Meteor Lake 就借助 Chiplet 设计灵活组合了 CPU、GPU 和 I/O 模块。

这些特点让 Chiplet 技术成为应对日益增长的计算需求以及摩尔定律放缓趋势的理想解决方案。

Part 2.Chiplet 技术在 HPC、AI 和汽车行业的应用

● 高性能计算(HPC)与人工智能(AI)

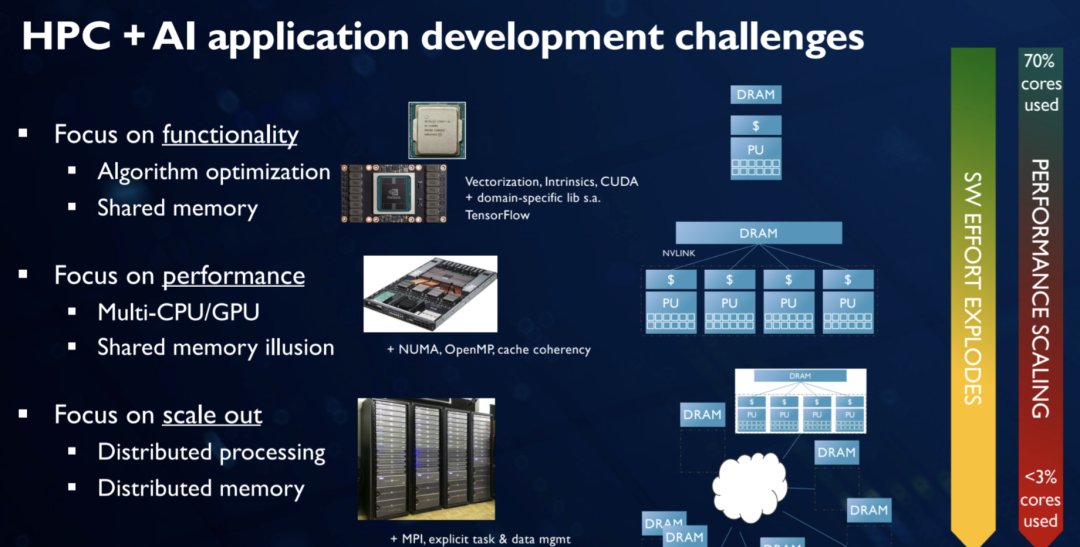

HPC 和 AI 领域对计算性能的需求呈爆发式增长,推动了 Chiplet 技术的广泛应用。传统单片芯片面临内存墙(Memory Wall)问题,即计算单元与存储单元之间的带宽和延迟限制了系统性能。

Chiplet 技术通过功能分区和高速互连有效解决了这一难题。应用案例:

◎ 英特尔 Ponte Vecchio:这款专为 HPC 设计的芯片包含 47 个模块,通过 EMIB(嵌入式多芯片互连桥)和 Foveros 3D 封装技术实现 1000 亿晶体管集成。其计算能力高达 1 PFLOPS,广泛应用于超级计算机。

◎ AMD EPYC-MI300:采用 13 个 Chiplet 模块,集成 1460 亿晶体管,支持 HBM3 内存,提供超过 5TB/s 的带宽,成为数据中心服务器的首选。

◎ 苹果 M1 Ultra:通过 UltraFusion 技术将两个 M1 Max 芯片连接,集成 20 核 CPU 和 64 核 GPU,峰值性能达 21 TFLOPS,展现了消费级市场中 Chiplet 的潜力。

Chiplet 技术在多个方面展现了显著的技术优势,包括内存墙的突破,通过将计算和存储模块分离,并利用高速互连(如 HBM 或 CXL)实现低延迟的数据传输,例如 Ponte Vecchio 的内存带宽就超过了 3TB/s。

此外,架构扩展性也是其一大亮点,从单节点到数据中心级别,Chiplet 支持根据具体需求灵活组装,AMD 的 EPYC 系列便是通过这种灵活性来调整核心数和内存配置,以满足不同客户的需求。

然而,为了充分发挥这些硬件优势,软件优化显得尤为重要,开发者需要运用 CUDA、OpenMP 等技术优化算法,同时管理多核协同和缓存一致性,在高性能计算(HPC)应用中,MPI(消息传递接口)常用于分布式任务分配。

● 汽车行业

随着汽车向智能化、电动化和网联化发展,汽车芯片的计算需求快速增长。

Chiplet 技术为汽车行业提供了高效解决方案。从 2011 年的 40nm 工艺(80 平方毫米,300 GFlops)到 2022 年的 8nm 工艺(455 平方毫米,250 TOPS),汽车芯片面积和性能显著提升。

大尺寸单片芯片的良率下降(从 90%降至 60%以下)增加了成本压力。

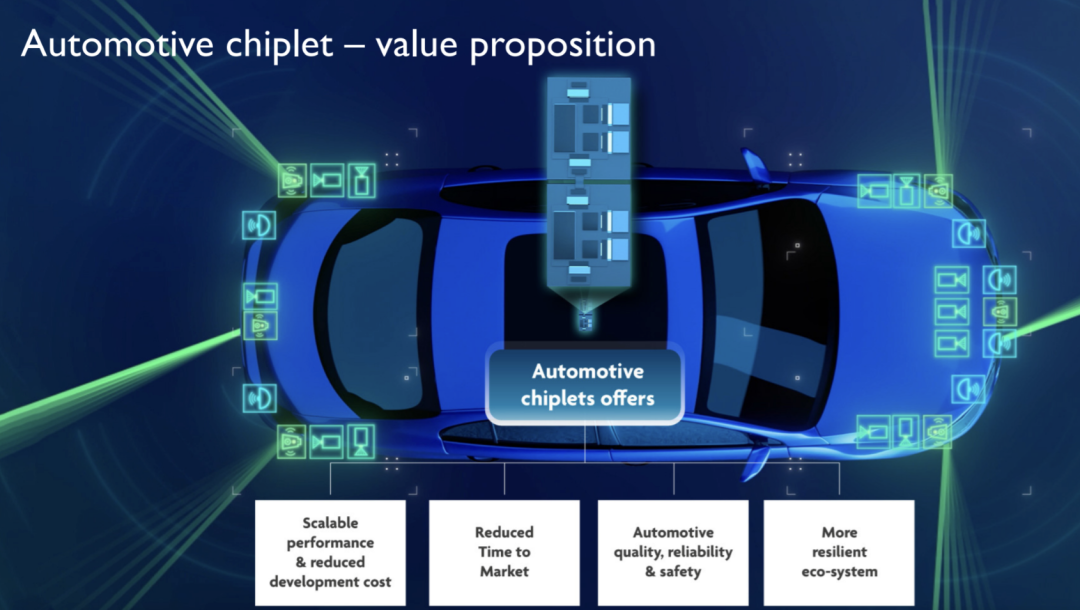

Chiplet 技术通过模块化设计缓解了这一问题:功能分解,将计算、通信和存储模块分开。例如,特斯拉的 FSD 芯片可分解为 AI 加速器和 I/O 模块。可靠性提升,小模块独立验证提高了系统稳定性,满足汽车苛刻的安全标准(如 ISO 26262 ASIL-D)。

◎ 现代汽车 AI SoC:通过 Chiplet 设计将计算模块(8nm)和传感器接口(12nm)分开,面积控制在 200 平方毫米以内,良率提升至 85%以上。

◎ 英伟达 Drive Orin:采用 Chiplet 理念集成多个功能单元,支持 200 TOPS 计算能力,广泛应用于自动驾驶。

Chiplet 技术在汽车行业的应用面临诸多挑战与对策。

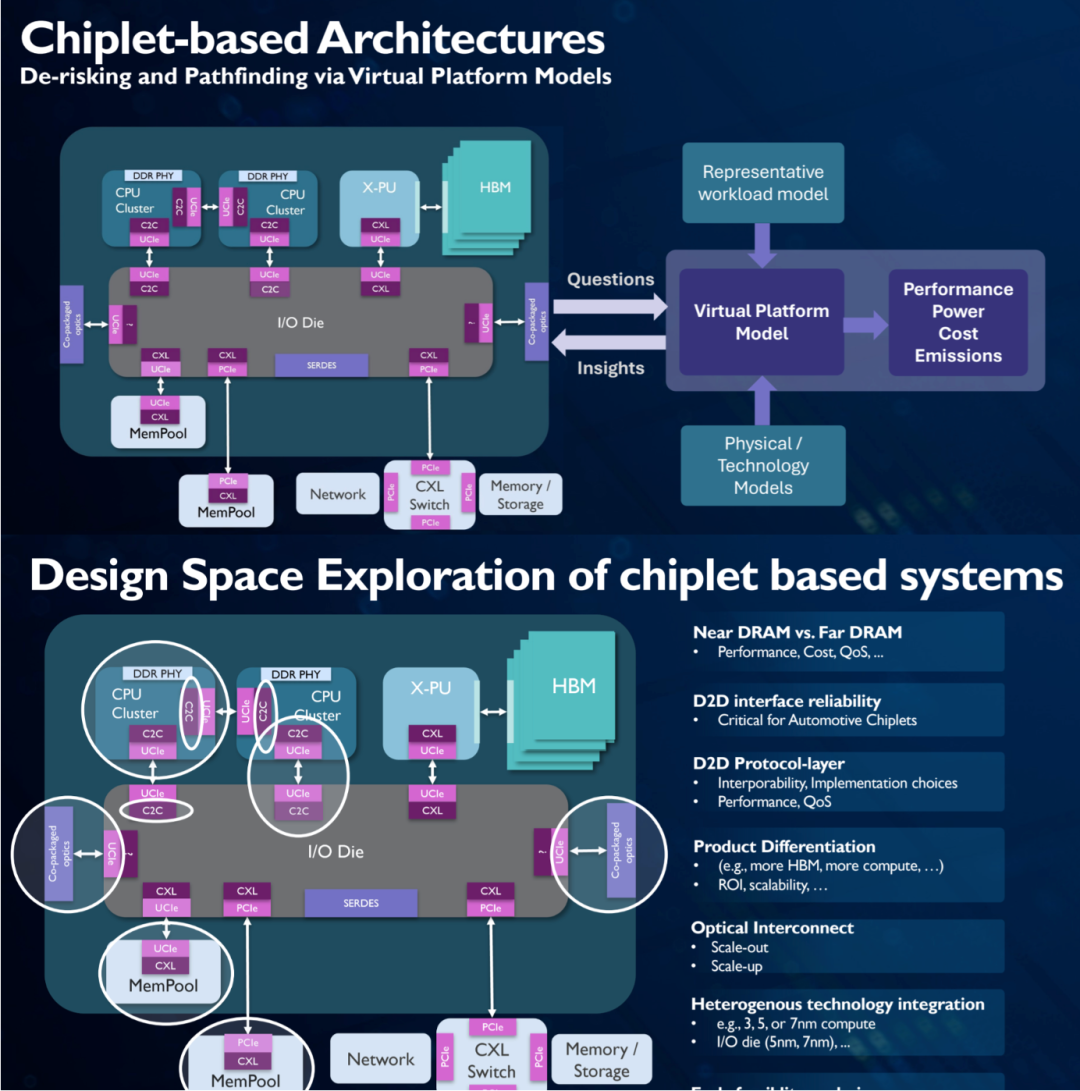

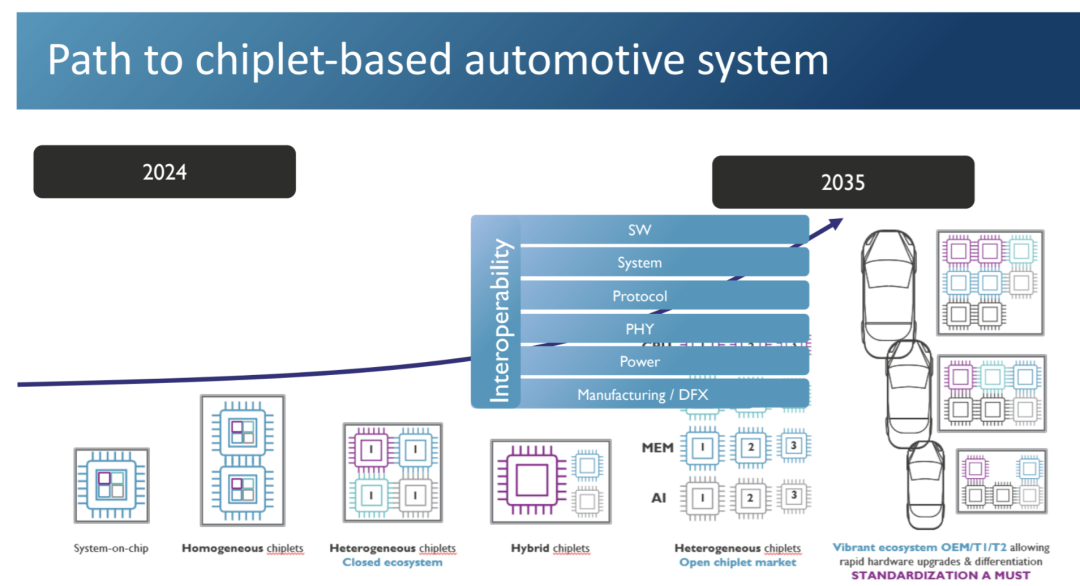

◎ 标准化需求方面,为了确保不同供应商提供的 Chiplet 模块之间的兼容性,汽车行业迫切需要统一的接口标准,如 UCIe,目前这一进程得到了行业协会如 OCP 和 JEDEC 的积极推动。

◎ 环境适应性是另一大挑战,汽车芯片必须能够在-40°C 至 125°C 的极端环境下稳定运行,这对封装技术提出了更高要求,例如系统级封装(SiP)需着重解决热管理及电磁干扰问题,以保证芯片性能和可靠性。

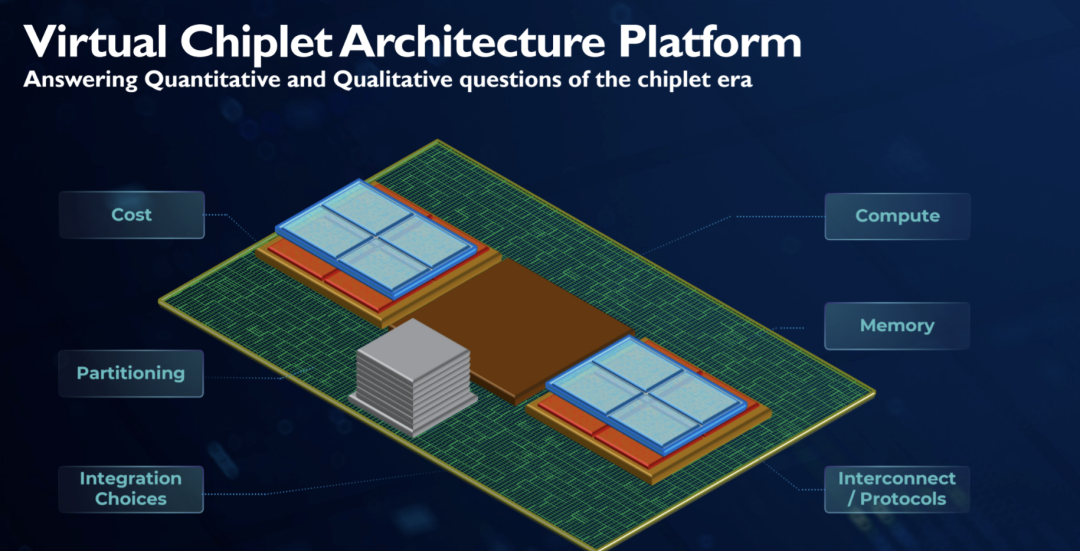

◎ 成本控制同样不可忽视,通过采用虚拟平台模型来优化模块间的交互,可以有效降低设计和验证的成本,Synopsys 等公司提供的虚拟原型工具能够模拟 Chiplet 系统的性能,为开发者提供了便利。

尽管面临这些挑战,Chiplet 技术凭借其灵活性和可扩展性,仍然成为汽车行业实现硬件快速升级和差异化竞争的关键驱动力,对于智能汽车的发展至关重要。

小结

Chiplet 技术作为半导体领域的重大创新,正在重塑计算架构并推动产业变革。在 HPC 和 AI 领域,它突破了内存墙和性能瓶颈;在汽车行业,它提升了良率和可靠性。

Chiplet 技术将推动计算架构向 CMOS 2.0 时代演进,进一步引入异构集成和 3D 堆叠,通过硬件-软件协同优化实现更高性能和能效。

END

作者:芝能芯芯

文章来源:芝能智芯

推荐阅读

- 如何看待「驾驶员状态监控系统」(DMS)在智能驾驶中的作用?

- 2024 年中国市场智能驾驶芯片市场分析:算力与发展趋势

- 汽车以太网:如何平衡性能与可重构性?

- HBM4E 或 HBM5 必须要用到混合键合技术吗?

更多汽车电子工程领域相关技术干货,请关注专栏芝能汽车电子设计 欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。