台积电在目前的汽车领域占了非常重要的作用,围绕“AI 时代的汽车芯片演进”做出重磅趋势研判:预计至 2030 年,汽车半导体市场将达 1500 亿美元,成为 AI 下一个关键增长极。

为了支撑辅助驾驶、电气化与智能座舱的发展,台积电不仅推出专为车用设计的 3 纳米 Auto Early(N3AE)工艺,还积极推动 Chiplet 架构与先进封装技术(InFO-oS、CoWoS)上车,致力于在性能、能效与集成度上达成平衡。

我们将从两个层面展开深度分析:

◎ 为何 AI 将重塑汽车芯片需求;

◎ 台积电如何通过 Chiplet 和 CoWoS 对汽车智能计算平台进行工艺层面的支持。

Part 1.AI 重塑汽车芯片需求:从辅助驾驶到全域智驾的变革逻辑

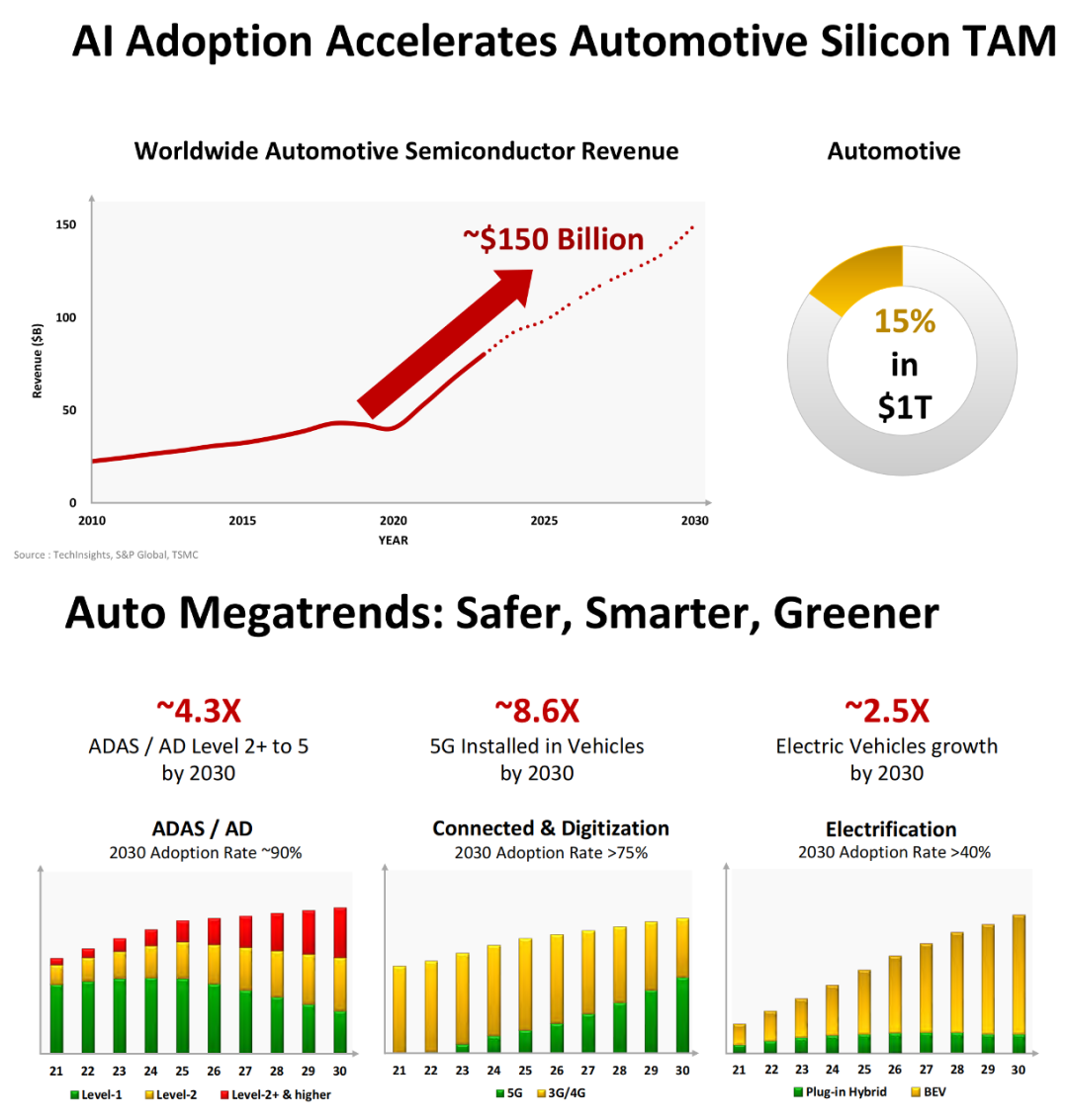

台积电在演讲中给出一个极具说服力的数据:未来五年,AI 将推动整个半导体产业规模迈向 1 万亿美元,其中约 15%——也就是 1500 亿美元——将来自汽车芯片。

这不再是简单的“量的扩展”,而是“质的飞跃”:从传统 MCU 到集成 AI 加速器的复杂系统芯片,自动驾驶、智能座舱和车载互联的演进都需要全新的芯片架构。

随着 ADAS/AD 普及率预计到 2030 年突破 90%,AI 的作用已从图像识别等局部功能向整车级认知与决策推进。

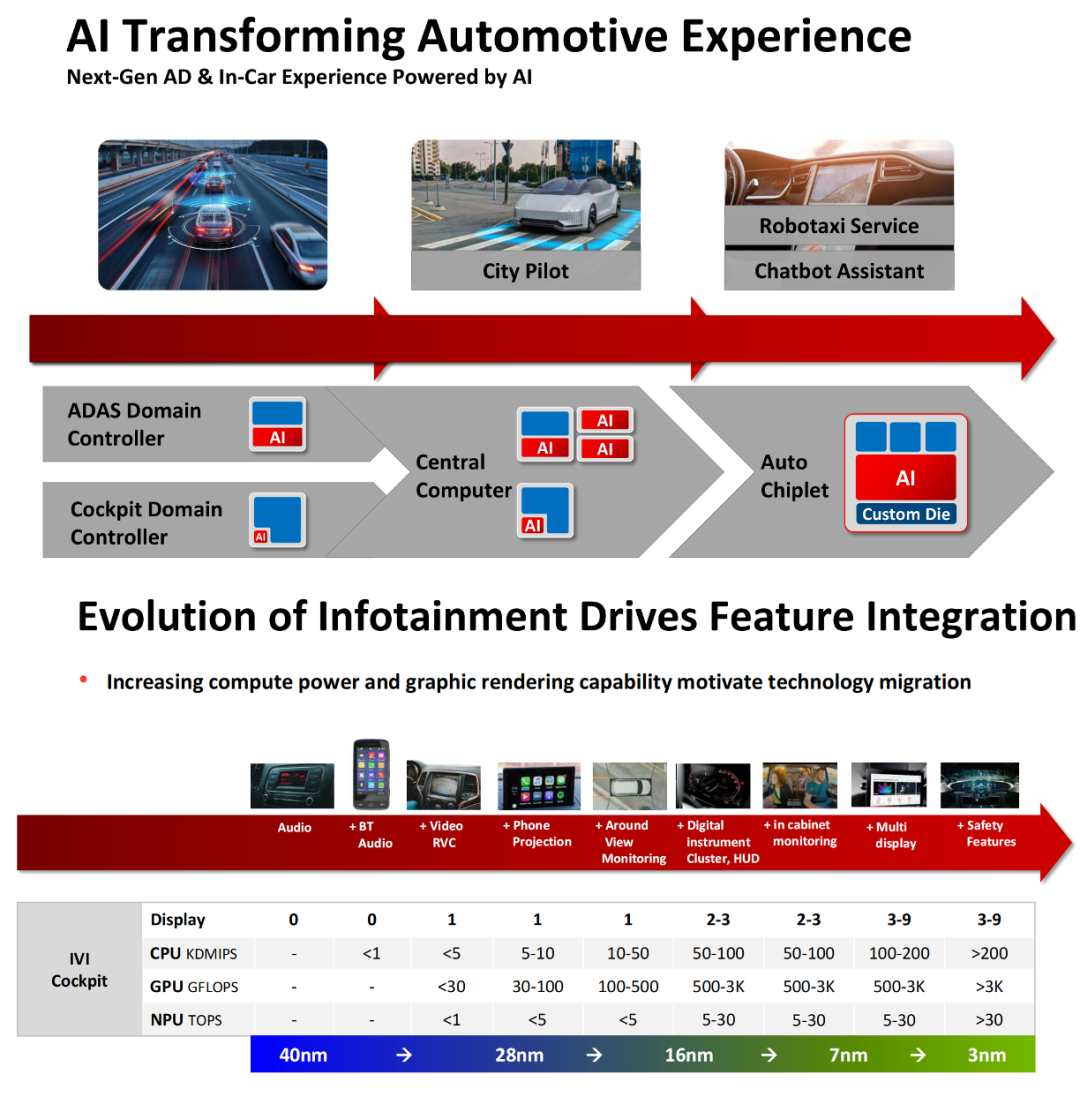

未来 L3-L5 级别的自动驾驶不仅要处理高速行驶中的目标识别、路径规划,还需应对城市路况的复杂决策,甚至实现 Robotaxi 无人出行。

对芯片而言,这意味着:

◎ 实时多传感器融合:摄像头、雷达、激光雷达等数据需在毫秒级完成融合计算。

◎ 大规模推理任务:例如 3D 点云语义分割、BEV 感知、端侧模型运行等。

◎ 语音与自然交互:Chatbot Assistant 等功能对 NPU/TPU 提出需求。

AI 应用的深度介入,倒逼汽车计算平台完成从“分布式”向“集中式”的彻底转型:

◎ 第一阶段:域控制器架构,每个功能域(如 ADAS、座舱)配备独立 AI 引擎,但冗余与成本高。

◎ 第二阶段:中央计算平台,统一多域功能,强调多核与 AI 协同处理。

◎ 第三阶段:Chiplet 架构系统,多个异构功能块通过高带宽连接集成,提升系统灵活性与可扩展性。

Chiplet 结构非常适合车规芯片的“低产量+高定制+高复杂度”特性,既可复用成熟模块降低成本,又能灵活组合应对差异化市场。车端芯片与数据中心最大不同在于功耗容忍度低,尤其对电动车平台至关重要。

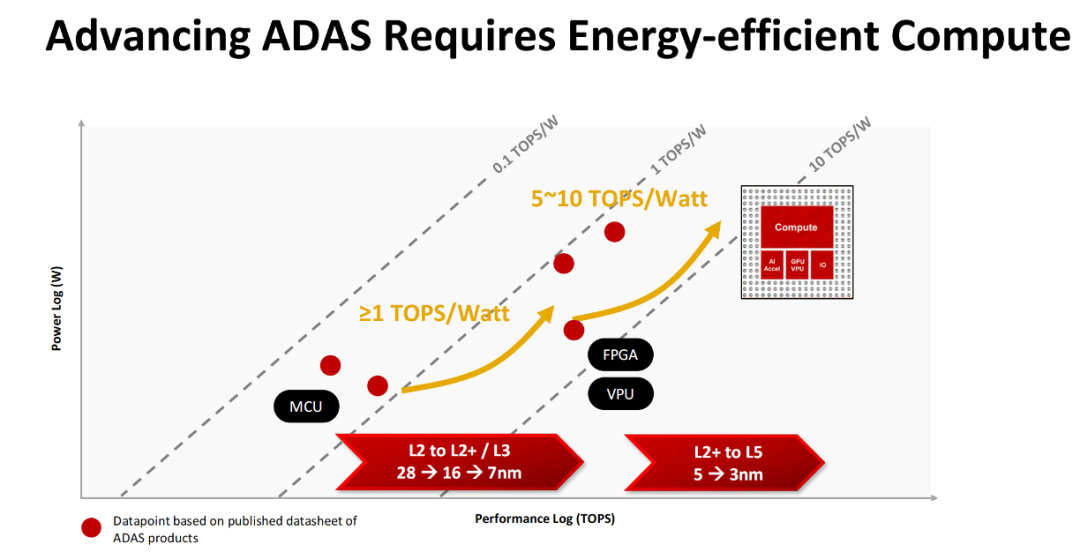

台积电将 ADAS 芯片能效分为三档:

◎ 初级 MCU:≥1 TOPS/W,适配 L1-L2 辅助驾驶;

◎ 中级 FPGA/VPU:5~10 TOPS/W,用于 L2+/L3 场景;

◎ 高级 AI 加速器:≥10 TOPS/W,支撑 L4-L5 智能驾驶。

因此,芯片设计必须在性能与能耗之间找到新的平衡点,这就为先进工艺与封装技术的导入创造了条件。

Part 2.从 N3AE 到 CoWoS:台积电如何为智能汽车打造芯片“终极形态”?

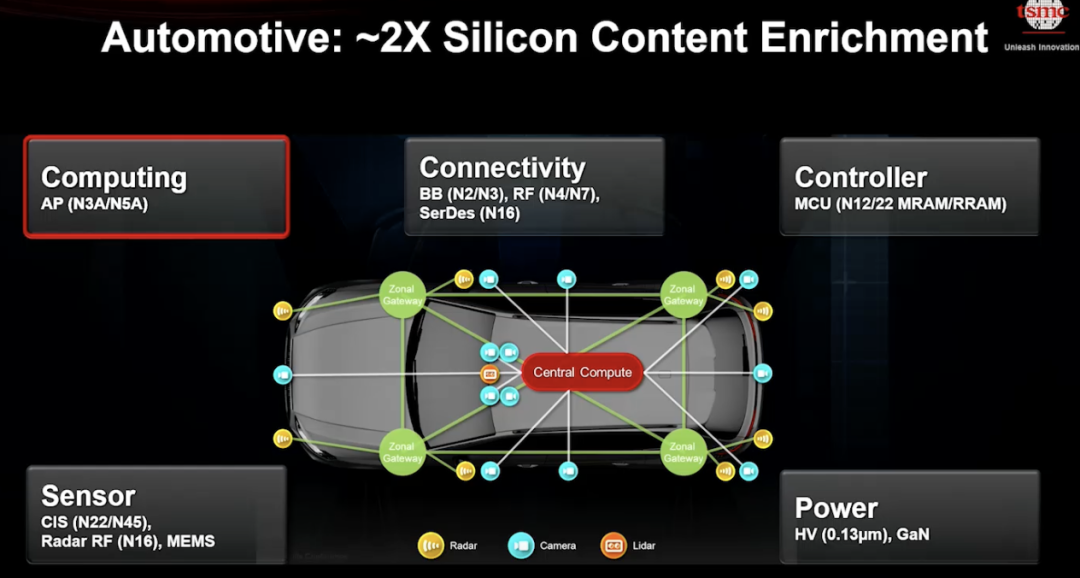

在整个汽车工艺里面,具有下面的工艺特点

◎ 计算:应用处理器(N3A/N5A 工艺节点 );

◎ 连接性:基带(N2/N3 工艺节点 ),射频(N4/N7 工艺节点 ), 串行器 / 解串器(N16 工艺节点 );

◎ 控制器:微控制单元(N12/22 工艺节点,磁性随机存取存储器 / 电阻式随机存取存储器 );

◎ 传感器:图像传感器(N22/N45 工艺节点 ),雷达射频(N16 工艺节点 ),微机电系统;

◎ 电源:高压(0.13 微米工艺 ),氮化镓。

在满足复杂 AI 场景与低功耗双重需求的路径中,N3AE 制程与先进封装技术构成了双轮驱动。

N3AE (3nm Auto Early) 是首款专为车规市场打造的先进制程节点,具备 ISO 26262、AEC-Q100 等认证支持,提供更优的功耗、性能与面积表现 (PPA) ,适用于高复杂度 SoC 与 AI 加速单元。

随着电动化与智能驾驶的发展,N3AE 正从手机和数据中心走向汽车领域,未来将成为高端车载芯片的重要标配。

Chiplet 架构虽非新概念,但台积电为其赋予了车规应用的新价值。

通过模块化设计,可将 AI 核心、ISP、MCU、CAN 控制、Sensor Hub 等功能分别制造并组合封装,既提升灵活性与定制性,又缩短开发周期,同时降低良率风险与生产成本。

鉴于车企和 Tier-1 对 AI 性能、传感器类型及接口协议的多样化需求,Chiplet 架构特别适用于车用芯片,助力实现快速定制与高效量产。

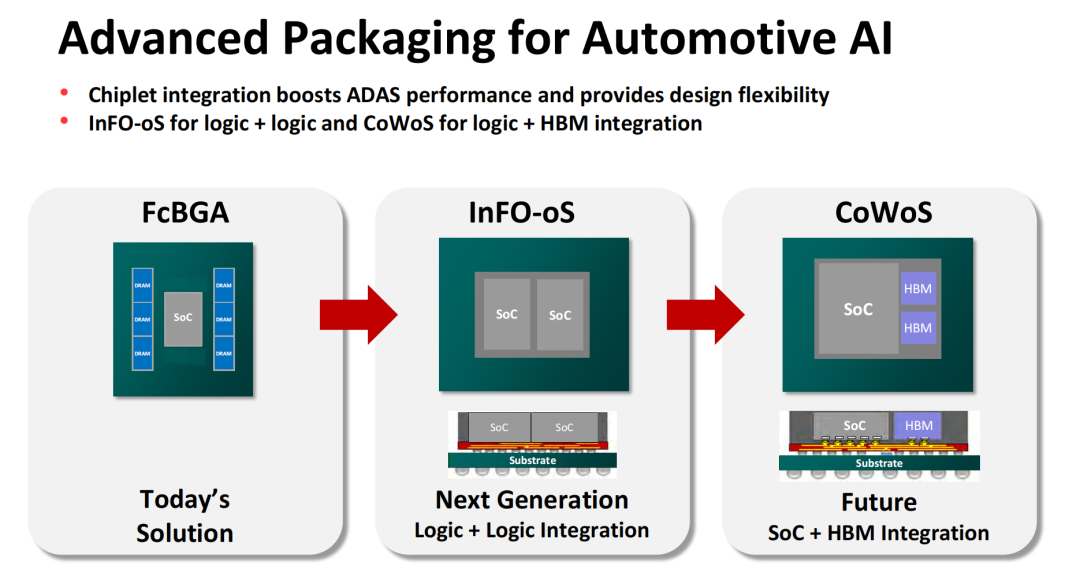

先进封装技术是 Chiplet 架构落地的核心支撑,台积电为此为汽车 AI 提供了三大封装方案:

◎FcBGA 目前为主流,适用于传统 SoC 但整合度有限;

◎InFO-oS 支持多个逻辑芯片整合,带来更高带宽;

◎ 而 CoWoS 则实现 SoC 与 HBM 的高密度集成,具备超强的 AI 推理与内存访问能力。

CoWoS 目前主要用于数据中心 GPU 如 A100/H100,但台积电正积极推动其在智能驾驶领域的应用。

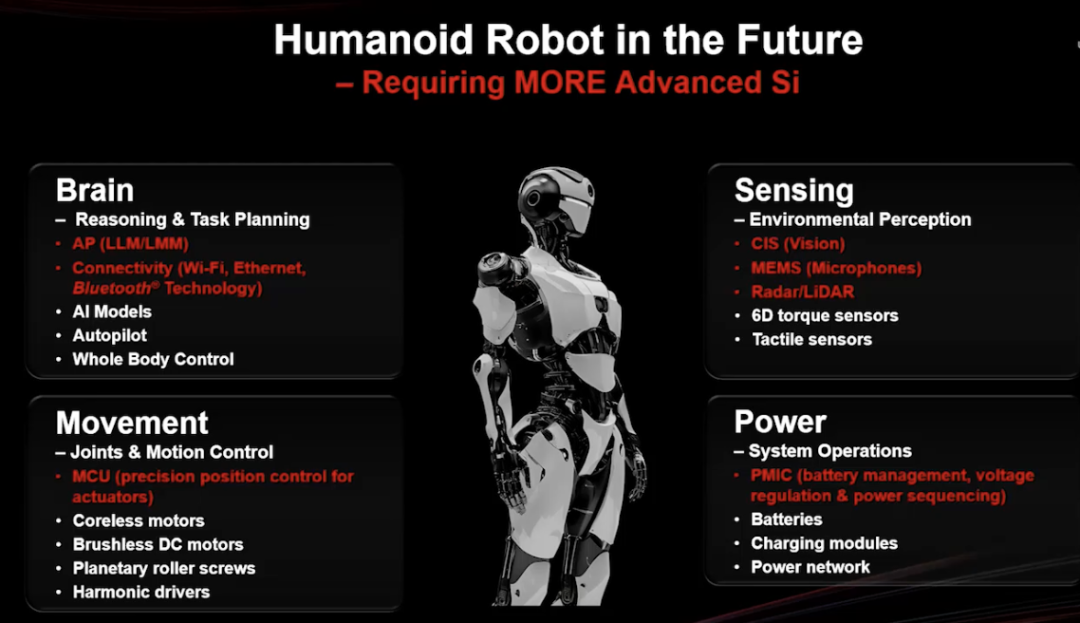

尽管面临功耗、散热及车规环境下震动与热冲击等挑战,一旦成功“上车”,将为 L4-L5 级自动驾驶芯片带来性能飞跃,开启辅助驾驶新纪元。当然车迭代结束以后,继续往人形机器人发展了。

小结

在智能汽车从“功能集成”转向“架构再造”的进程中,Chiplet + 高带宽封装是未来终点。而谁能率先提供可靠、低功耗、高集成度的 Auto Chiplet 平台,谁就能引领下一轮“汽车 AI 芯片革命”。

END

作者:芝能芯芯

文章来源:芝能智芯

推荐阅读

更多汽车电子工程领域相关技术干货,请关注专栏芝能汽车电子设计 欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。