本文章基于极术社区的公开资料整理的,链接如下视频:[链接]PPT:FlagOS在“周易”NPU上的快速部署(见文末附件PDF,登录后即可自行下载)文档:[链接]目录Compass SDK 概览首先大致了解周易NPU硬件架构,然后初步了解其AI软件工具链AIPUBuilder, 最后了解其表示神经网络计算图的IR--Compass IR.Tutorial 0: BackgroundTutori...

2024年AMD发布了变化巨大的一代微架构Zen5,并宣称Zen5微架构是未来几代微架构的基石。相比较Zen4,Zen5的IPC增加了16%,这个增长非常可观,同时还能实现高达5.7GHz的频率,支持AVX512变体以及FP-512,Dispatch宽度为8,6 ALU,取指和解码(Fetch/Decode)均采用双流水线,本代预计采用TSMC 4/3nm工艺,每个核具有2个线...

现代 SoC 设计通常采用多个时钟,并包含多个时钟域。当数据从一个时钟域跨越到另一个时钟域时,由于异步时钟域交叉(CDC),会出现亚稳态问题的风险。

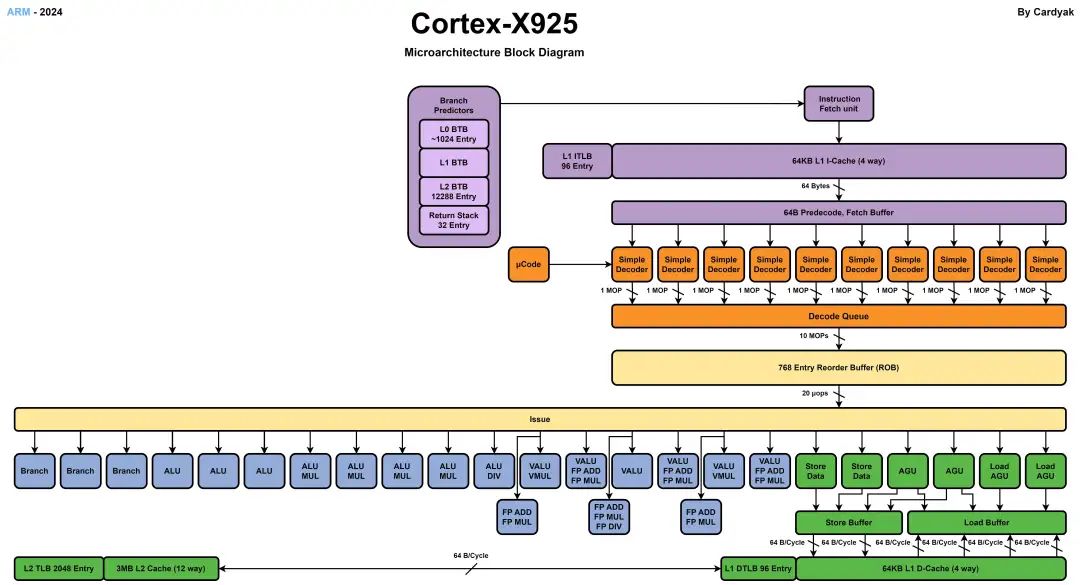

主要是 PC 和移动端,Arm,Apple,Intel,AMD,因为应用场景不同参数不一定有实际的比较价值。目前亦安最关注的是 Arm Server 的 V/N 系列,Arm 的 Server V3/N3 没有拿到什么可靠的数据也没法比,官方还没公开太多信息。后续我会发些 Arm 移动端的核,现在先宏观聊聊,有其它微架构问题可以加我微信讨论。

CPU是一个非常复杂的系统,评估其性能并不好量化,传统上讲,我们(雷总)习惯说“不服跑个分”,这种方式当然也是一个相对靠谱能够对CPU性能进行量化评估的方式,但评估性能对于技术人员来讲,远不是跑个分就能得出结论的,本文将从CPU微架构的角度去讲解当前先进的微架构设计具备特性。亦安不会太过展开微架构的设计细节...

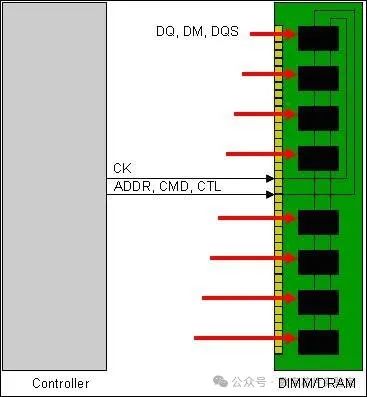

今天和大家分享一下 DDR 内存设计中一个重要的技术 - 写平衡(Write Leveling)。这项技术对于高速 DDR 内存的正常工作至关重要。

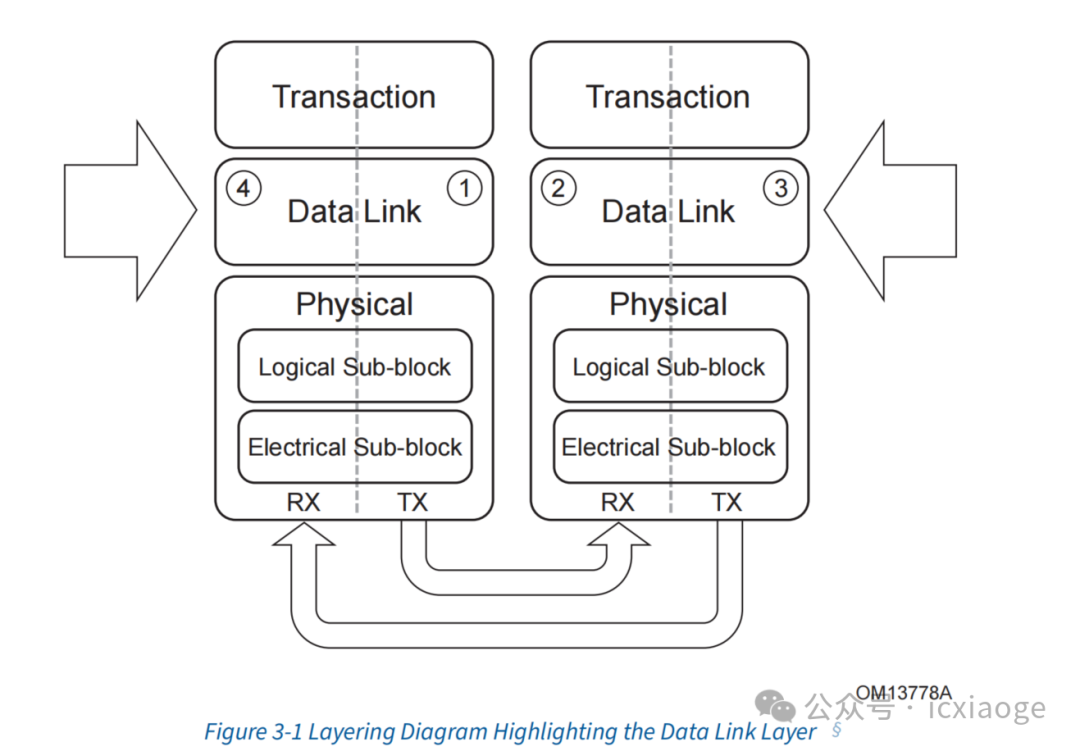

Data ExchangeAccept TLPs for transmission from the Transmit Transaction Layer and convey them to the Transmit Physical Layer

文章修改自: [链接]之前解读过两期 LMDeploy Turbomind 里的源码,针对 Hopper 架构。NV 推出了新的指令集。今天我们就来一起看看 TMA

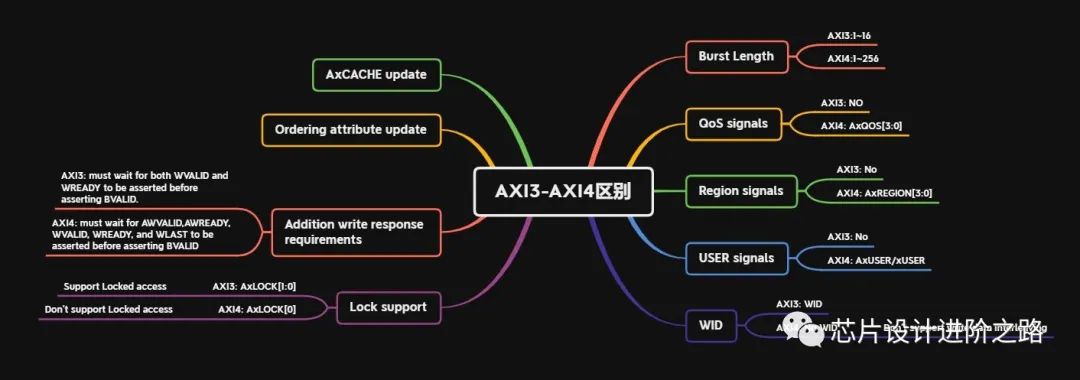

在 SOC 各种总线中,AXI 是最重要的总线,没有之一。不管是在工作中,还是在面试中,AXI 协议是一个必须精通的知识点。ARM 从 AMBA1 到 AMBA5 一共五代的 AMBA 总线中,AXI 有两代,分别是 AMBA3 的 AXI3 和 AMBA4 的 AXI4。AXI3 和 AXI4 的区别在协议里当然可以找到对应的部分,但是真正的理解和总结 AXI3 和 AXI4 的文...

Arm 凭借在技术生态系统中所处的独特地位,对全球半导体供应链有着全盘了解,并在数据中心、物联网、汽车、智能终端等各类市场深入布局。基于此,Arm 对未来技术的发展方向及可能出现的趋势有着广泛而深刻的洞察。我们将分三期内容为你详细列举从人工智能 (AI) 到芯片设计,再到不同技术市场的主要趋势,带你深入了解 2...

“你买的 4090 多少钱?”、“H100 性能真厉害!” ,GPU 的价格性能一直是大家乐于谈论的话题,作者也经常可以在茶余饭后听到这样的讨论。在热火朝天地谈论性能指标、价格以外,本着”知其然也要知其所以然“的道理,作者学习整理了 GPU 本身的工作原理,编程模型,架构设计,在这里将我的学习笔记整理成文与大家分享,希望与...

“每天用手机刷视频、打游戏、扫码支付的你,可能从未意识到:掌心里的这块‘玻璃板’中,藏着一座堪比北京地铁网的超级迷宫——它就是手机芯片(SoC)。

随着芯片设计向异构组装和 3D-IC 技术迈进,提供和管理电力已成为芯片制造中的核心挑战,显著增加了设计复杂性,迫使制造商在性能、可靠性和成本之间进行艰难权衡。

SM8650 平台上,GLES 发送给 KMD(GPU 驱动)的 GPU 命令有两种类型:同步命令和绘制命令。

真空中光速为299,792,458米/秒,目前,Intel的i7频率可以达到4GHz,简单换算一下,可以得出结论:光(电流)在一个Cycle内移动的距离约为0.075米。显然,目前的内存条的芯片(反正两面。约为3.75cm)大大超过了这个长度,换句话说,理论上,在一个Cycle内内存条上总有一个位置是我们无法触摸。

最近浏览文章发现了一个非常棒的开源AMBA代码生成工具:GitHub - adki/gen_amba_2021: AMBA bus generator including AXI4, AXI3, AHB, and APB

2024 年,Marvell 在其分析师日活动中推出了具备革命性创新意义的 Structera A 内存扩展控制器。

DeepSeek R1 的完整训练流程核心在于,在其基础模型 DeepSeek V3 之上,运用了多种强化学习策略。本文将从一个可本地运行的基础模型起步,并参照其技术报告,完全从零开始构建 DeepSeek R1,理论结合实践,逐步深入每个训练环节。通过可视化方式,由浅入深地解析 DeepSeek R1 的工作机制。

今天给大家带来 DeepSeek 推荐的开源项目,因为有些项目已经失效了,所以会替代为一些相近项目。

众所周知,随着芯片越来越大,功能越来越丰富,以及移动市场的切实需求,低功耗的芯片设计,越来越受到推崇。这里,结合多年的低功耗设计经验,把一些理念和方法,分享给各位。 通过一些理论书籍,大家都知道功耗的来源主要分为两种,一种是动态,一种是静态。