今天和大家分享一下 DDR 内存设计中一个重要的技术 - 写平衡(Write Leveling)。这项技术对于高速 DDR 内存的正常工作至关重要。

先了解一下基本需求

在 DDR 设计中,有几个关键的时序参数:tDQSS、tDSS 和 tDSH。不用死记硬背这些参数的具体含义,我们只需要理解一个核心概念:当时钟(clock)和选通脉冲(strobe)信号到达 DRAM 时,它们的上升沿必须在特定的时间范围内出现(通常是 ±tCK/4 左右)。

对于单个 DRAM 的设置,这不是问题。只要时钟和选通信号的长度基本匹配,它们就会几乎同时到达 DRAM。

高速带来的问题

在 DDR2 及更早的技术中,即使有多个 DRAM,这也不是问题。这些设置中,通过树形拓扑结构使每个 DRAM 的时钟长度相互匹配。如果通道中有八个 DRAM,从控制器到每个 DRAM 的时钟长度会被设计成等于选通信号到 DRAM 的长度。

但是,树形拓扑结构充满了反射段。每个分支都会创建一个不连续点,更不用说还有多个端点。随着数据传输速率的提高,树形拓扑结构变得越来越难以管理。

DDR3 的解决方案

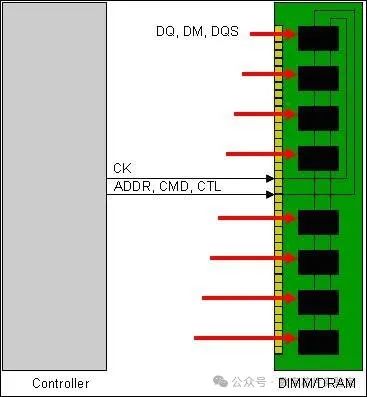

DDR3 引入了"Fly-By"(飞越式)布线。使用这种布线方式,时钟(和地址)信号从控制器开始,为所有 DRAM 创建一个主通道。DRAM 通过一个很短的存根(stub)连接到主路径。这样,存根被最小化,主路径可以在布线末端整齐地终止。

然而,这创造了一个关于 DRAM 处时钟与 DQS 要求的基本问题。使用飞越式布线,靠近控制器的 DRAM 会比布线末端的 DRAM 更早收到时钟和地址信号。因此,数据和选通信号需要更早到达第一个 DRAM,晚一点到达最后一个 DRAM,以便对齐时钟和选通信号。

写平衡:完美的解决方案

解决方案是让控制器自动检测不同 DRAM 之间时钟信号的飞行时间差异,然后适当延迟数据通道,使它们在时钟/地址信号到达 DRAM 时到达 DRAM。检测所需延迟的过程通常在启动时完成,称为"training"。整个系统称为"write leveling"(写平衡)。

同样可以延迟一个通道内的每个 DQ 位相对于其选通信号,以便完美地使选通信号居中于 DQ 信号周围。这个功能在 DDR4 控制器和一些高端 DDR3 控制器中更为常见。它有很多名称,包括"per-bit leveling"、"DQ calibration"或"DQ-DQS deskew"。

写平衡技术看似复杂,但实际上解决了 DDR3 和更高速内存设计中的关键问题,让高速数据传输变得更加可靠。

END

作者:learn vlsi

来源:数字芯片实验室

推荐阅读

更多数字 IC 设计技术干货等请关注数字芯片实验室专栏。添加极术小姐姐(微信:aijishu20)微信可申请加入IC设计交流群。