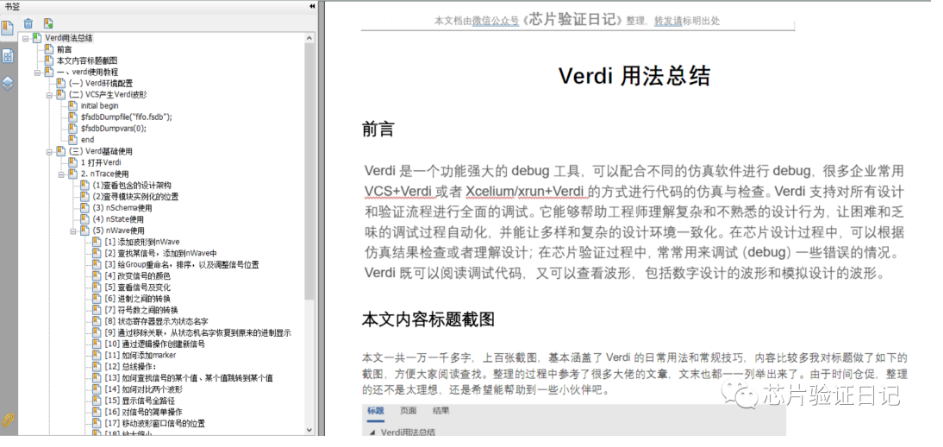

前段时间本公众号发了一篇名为《verdi用法小结》文章,没想到获得了大家的一致好评,好几个大佬的公众号都做了转发,目前这篇一万多字的verdi用法小结在全网的阅读量已经破万,再次非常感谢诸位大佬的转发以及各位读者朋友们的好评。

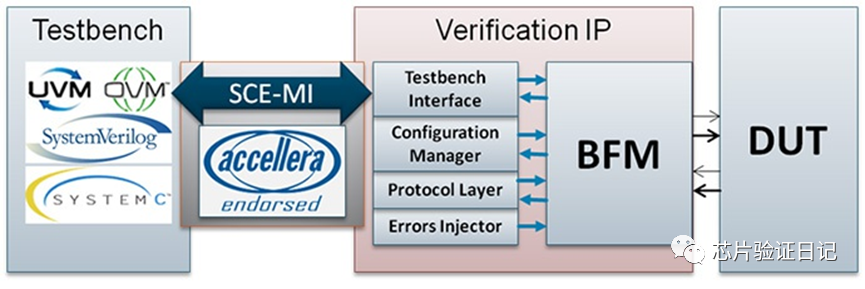

这里所说的VIP指的就是Verification IP(验证IP),做芯片设计和验证的朋友都很熟悉。关于VIP在芯片验证过程中的重要性,我就不啰嗦了,大家都懂。目前VIP的vendor,主要是Synopsys(简称S家)和Cadence(简称C家)这两家占据的份额比较多。目前不管是从市场份额还是用户群体上来说,S家都占据明显优势。事实上从网上公...

在计算机硬件(特别是集成电路)和软件系统的设计过程中,形式验证的含义是根据某个或某些形式规范或属性,使用数学的方法证明其正确性或非正确性。形式验证是一个系统性的过程,将使用数学推理来验证设计意图(指标)在实现(RTL)中是否得以贯彻。

前段时间听了百度技术培训中心章淼博士讲的《代码的艺术》直播课,章老师是业界大牛,课讲得娓娓道来,内容很丰富,很多点都戳到了我以前或现在的痛点,也激发了自己很多反思,总之收获很多,现在简单总结一下,主要分以下几点吧。

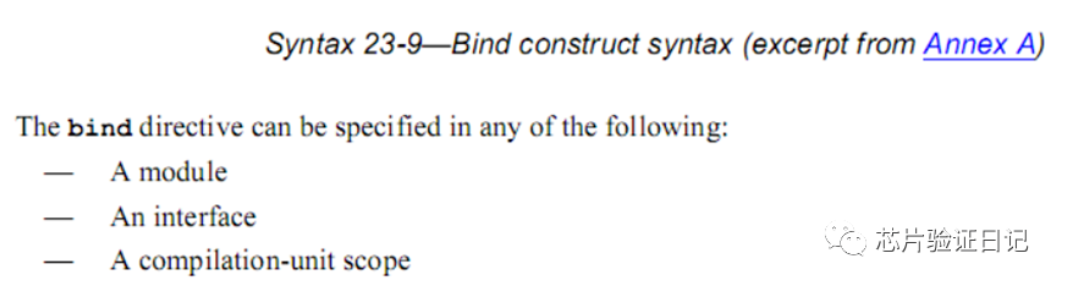

1.前言bind是systemverilog中一个重要的知识点,很多时候能够在验证中发挥重要的作用,今天就针对这个知识点做一个梳理,希望能帮助到大家。

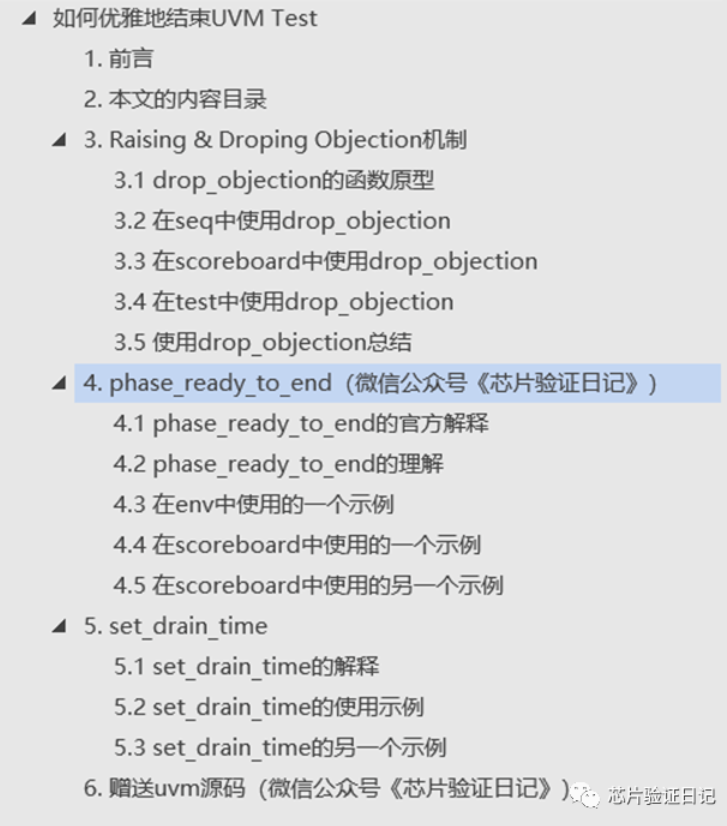

0.本文的内容目录本文一共接近一万一千字,为了帮助大家阅读,我把本文的内容目录截图如下,大家根据需要阅读,或者一次阅读不完,下次再读的时候方便查阅。1.I2C概述I2C是Inter-Integrated Circuit(内部集成电路)的简称,是一种通用的总线协议。它是由Philips(飞利浦)公司,现NXP(恩智浦)半导体开发的一种简单的双向两...

前言众所周知,在传统的测试平台中,通常在完成复位、配置、数据传输和自动检查等所有步骤后,通过调用verilog的系统函数$finish来结束仿真。

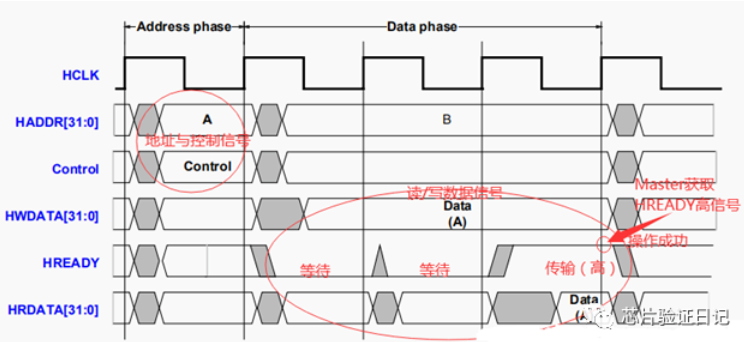

1.前言相信很多朋友对AMBA都比较熟悉了,对AHB总线也不陌生,在AHB总线中,hready这个信号是最难理解,最容易搞错,也是系统调试的过程中出问题最多的地方之一,同时也是很多面试官最喜欢问的知识点之一。本文做一个梳理,帮助大家彻底理解这个知识点。

当今的SoC芯片,普遍包含大量的工业标准接口同外围设备相连。 在验证设计过程中,这些接口被用于和测试testbench相连接。这些沟通桥梁,被称为 Verification IP (VIP) 的模块实现。Verification IP (VIP) 是一种特殊的IP Core。它将一个接口的BFM 和 Test Harness features 结合在一起。VIP在芯片验证中的应用场景众多,...

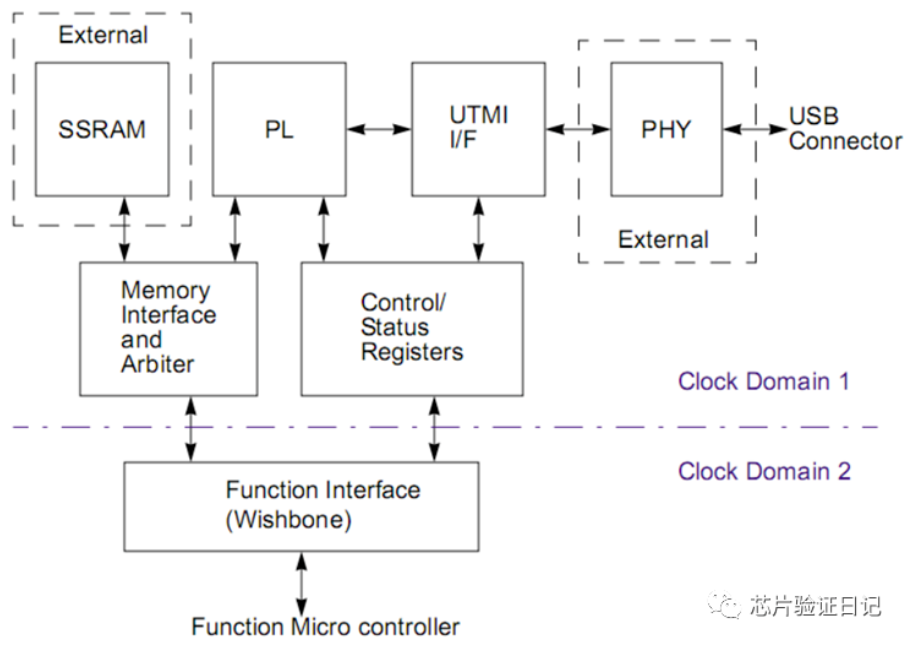

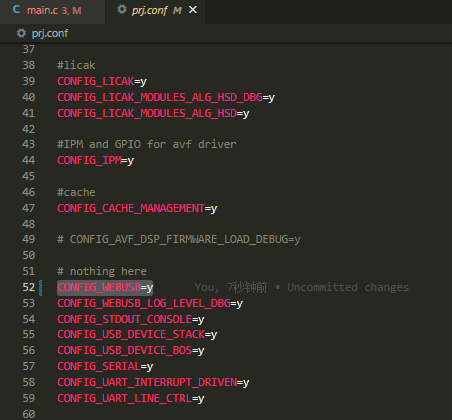

被usb折磨了一段时间了,不写点东西记录一下,都对不起自己的青春。而且以后还将会继续被折磨,所以不写一个系列,真对不起自己的人生呀。希望在记录自己努力学习的过程中,也能给感兴趣的小伙伴儿带来帮助。今天是开篇,先分享一个高质量的usb2.0项目给大家。

对于云计算服务商而言,开发者有一种特殊的魔力,他们就像云上挥毫泼墨的画家,将灵感用代码一一实现,绘出云端生态“全景图”。

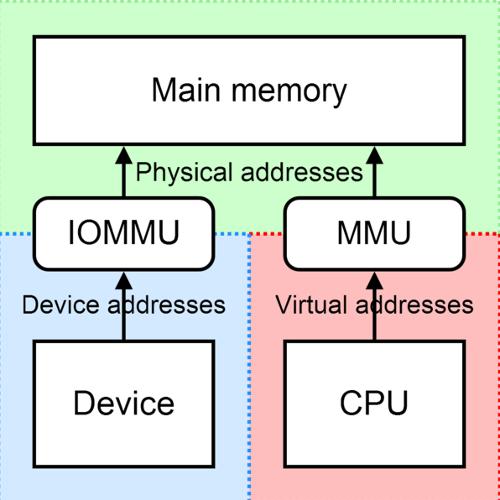

近年基于arm应用处理器的移动,infrastructure SoC平台都包含SMMUv3 IP(MMU-600,MMU-700),用于DMA mapping,VFIO,Shared Virtual Address(SVA)等场景。在这些使用场景中,SMMUv3是这样使用的呢?SMMUv3的硬件设计方面比较灵活,但是软件使用方面是有些限制的。本文不是介绍SMMUv3构架或IP,而是站在应用SMMU的角度...

在访问极术社区时,偶然发现聆思科技的CSK6开发板的评估活动,看CSK6的硬件配置和技术规格,300M的M33核 + 300M的HIFI4 + 128TOPS的NPU,完全有机会在我们公司内部的音视频产品上用上,因此申请了该方案的测评,以便更详细的了解该方案,也期待后续的音频模块,以便集中测试方案的音频部分以及音视频结合部分,确认是否...

今天,云计算正在创造越来越多的终端新形态。手机不再只是通信,是一款手中的计算机;汽车不再只求“马力”,需要比拼“算力”,是一台“四轮计算机”。

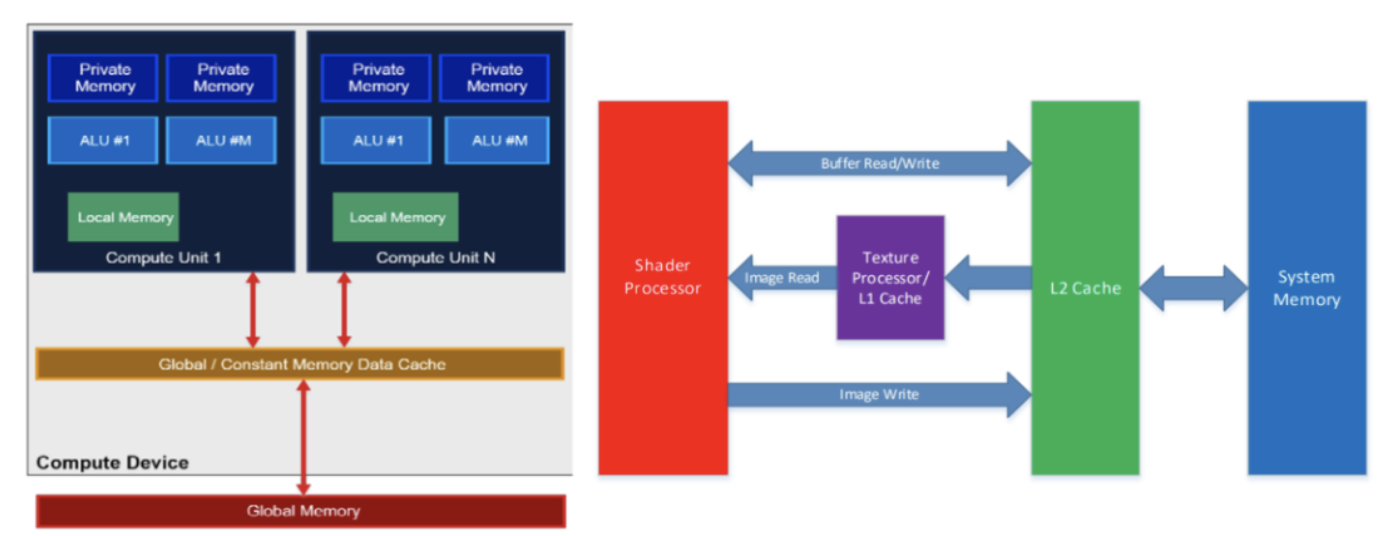

2020年8月TensorFlow Blog关于TensorFlow Lite的文章,就是提到OpenCL后端比OpenGL后端性能好,但事实真的是如此么?前几天我们刚发布有关《ShaderNN推理框架:来自OPPO的着色器深度学习推理引擎》的介绍,其GPU Kernel实现是基于OpenGL的Compute Shader(计算着色器),且性能好于TensorFlow Lite的OpenCL,也有实测的b...

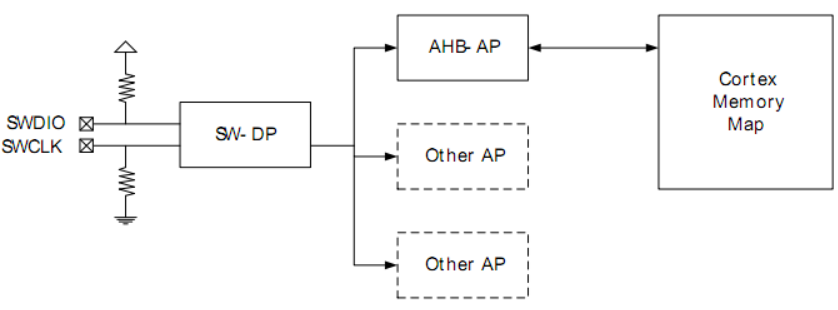

前言ARM的文档写的已经很好了,但是关于上电以后的第一时间应该怎么操作,依然写的不够清晰,导致我第一次用的时候还是费了一些周折。今天做一个详细的梳理,希望能够帮助到更多的朋友。BTW, ARM_Cortex-M0/3 DesignStart系列会持续更新,只是中间可能会穿插其他知识点。

FPGA Logic 二三事

想成为 IC 工程师 / 业余 FPGA,历史学,计算机网络爱好者

早些时候在实验室进行了一次 AXI 总线入门研讨,我作为 “3/16” 个 AXI 专家(笑)也分享了自己制作的一个 AXI 介绍 PPT。这里分享在网络上,欢迎读者们讨论指正。