1.前言

bind是systemverilog中一个重要的知识点,很多时候能够在验证中发挥重要的作用,今天就针对这个知识点做一个梳理,希望能帮助到大家。

- 为什么需要bind

当RTL已经编写完毕,验证工程师有责任添加断言时。RTL设计者不希望验证工程师为了添加断言而修改其RTL,于是SystemVerilog的绑定特性应运而生。bind可以实现验证和设计的分离,将module/interface/program绑定到任意的设计模块或者其特定例化中,可以将interface直接bind到top module中进行例化。bind可以使得验证工程师不改动或最小的改动原有设计代码和文件结构,就能够实现对设计代码的检查。

SystemVerilog断言(SVA)可以直接添加到RTL代码中,也可以通过bindfile间接添加。实践表明,大多数的断言最好是使用bindfile添加。在独立的文件中写入所有必需的断言,使用bind就可以将断言文件的端口与测试代码中RTL的端口/信号绑定。这是多么酷的一个功能。

- bind的语法

bind用于指定module、interface、program的一个或多个实例化,而无需修改目标文件的代码。因此,封装在module、interface、program中的插入代码或断言可以以非侵入方式(non-intrusive manner)在目标模块或模块实例中实例化。类似地,封装在接口中的检测代码可以绑定到目标接口或接口实例。

SVA检验器通过关键字bind可以与设计中的任何模块(module)或者实例(instance)绑定。将SVA检验器可以与模块、模块的实例或者一个模块的多个实例进行bind绑定。实现绑定时,使用的是设计中的实际信号,语法如下:

bind <module_name or interface_name or instance_name> <checker_name> <checker_instance_name> <design_signals>;

这里注意以下几点:

[1] 通过bind语句将SVA的checker与设计模块绑定,等价于将SVA例化到设计模块中。

[2] bind不仅可以将断言与设计module绑定,也可以将任意两个模块之间进行绑定。

[3] bind功能可用于以下位置:

- bind的具体应用实例

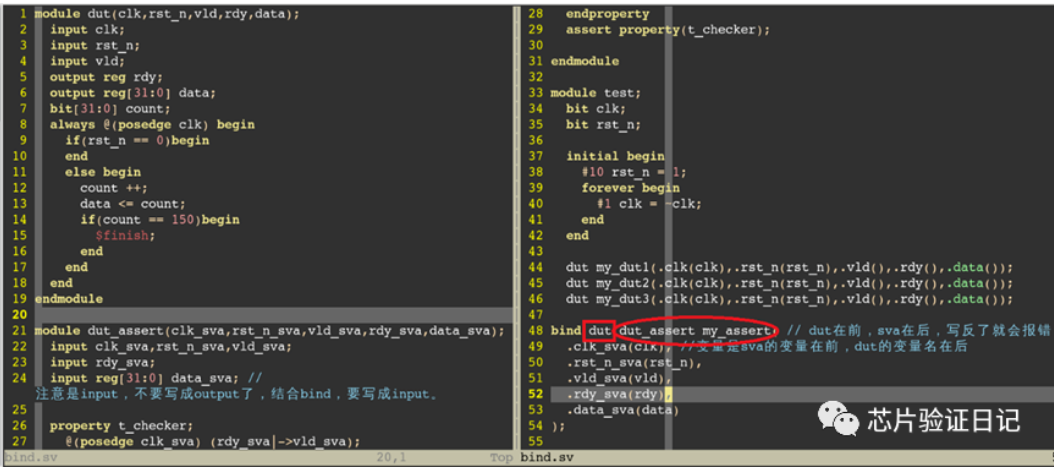

4.1 通过模块名实现绑定

语法:bind module_name sva_name sva_inst;

具体实例的代码如下图所示:

针对上图中代码的一些解释:

[1] dut 是module的名字

[2] dut_assert 是内部包含 property 以及断言的模块,可以是 module 或者 interface

[3] my_assert是dut_assert的实例化名字

[4] 括号中的信号clk/rst_n/vld/rdy是dut的端口信号,并且连接到dut_assert的对应端口

[5] 包含断言的interface/module,其端口信号的方向均为input,也就是说property中包含的信号都是从该interface/module外部给进来的。

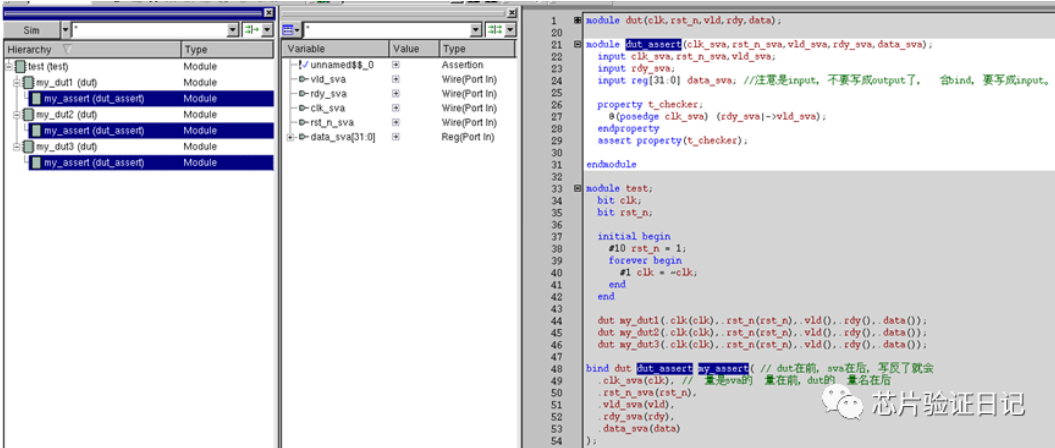

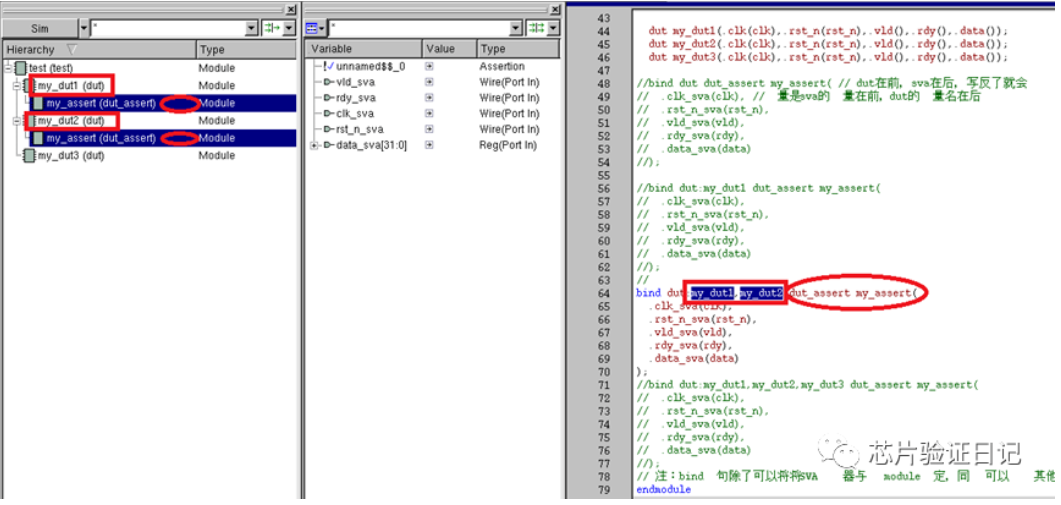

bind成功后,断言会关联到module_name的所有例化示例,sva_inst路径位于rtl_inst下一层,参考下面仿真器中的hierarchy结构:

具体的实验源代码和脚本,请参考分享的网盘链接中的basic目录。

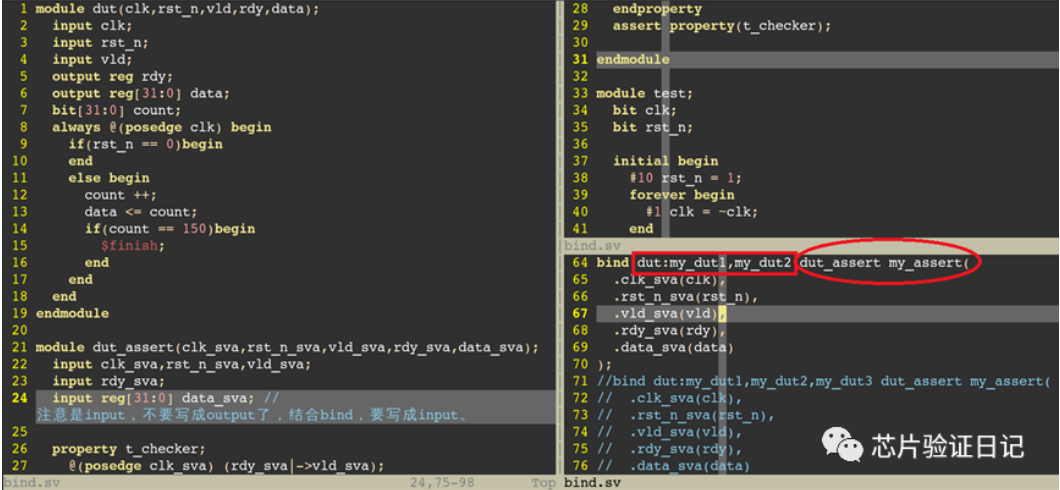

4.2 通过模块实例化名实现绑定

语法:bind module_name:mudule_inst_name sva_name sva_inst;

具体实例的代码如下图所示:

注意跟4.1的区别:

上图中第64行中,对dut的实例化my_dut1和my_dut2进行bind。

下图中的hierarchy结构图和上图中的代码是正确对应的,这也很好理解。

具体的实验源代码和脚本,请参考分享的网盘链接中的basic目录。

4.3 通过模块名实现bind的另一个例子

前面的例子对bind的基本用法已经讲的很清楚了,下面的例子只是想说明下面这一点:可以将需要的所有断言写入独立的文件中,使用bind也可以将断言文件的端口与测试台代码中RTL的端口/信号绑定。下面是这个例子的详细代码截图。

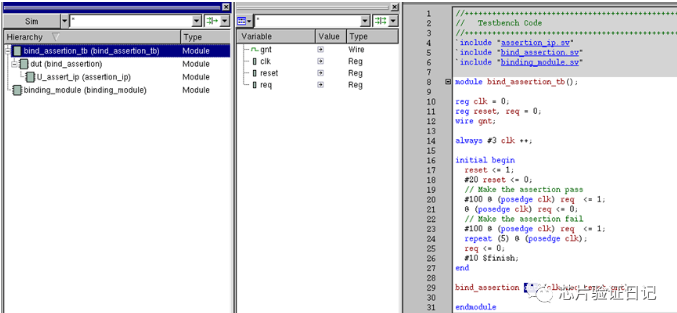

下图是testbench(最大的module)的代码截图:

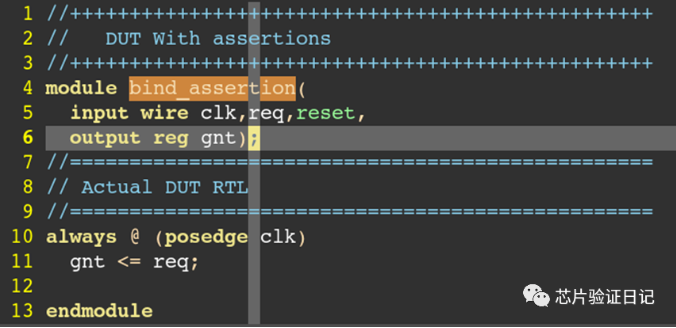

下图是DUT代码的截图:

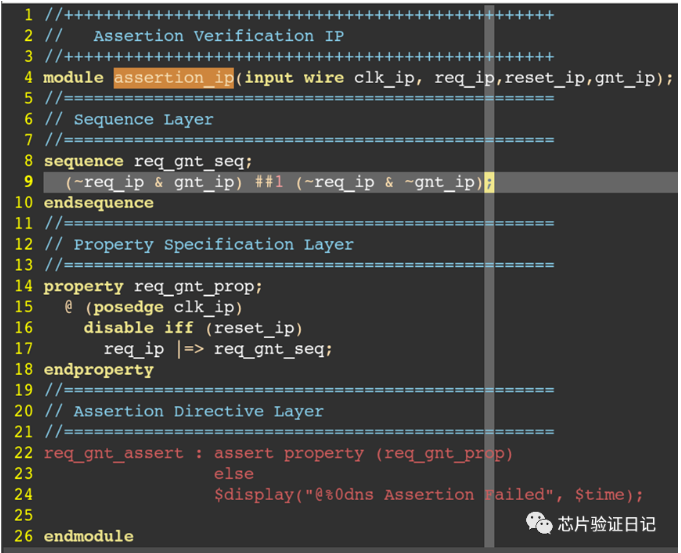

下图是断言模块:

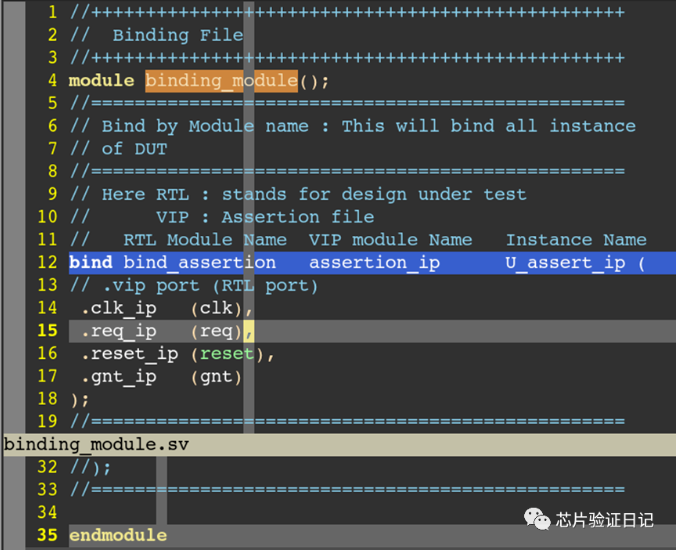

如下图所示,bind功能单独写在一个独立module中,这种用法EDA工具也是支持的,这是这个例子跟上面例子的最大区别。

注意理解下图中的hierarchy结构,

具体的实验源代码和脚本,请参考分享的网盘链接中的asic-world目录。

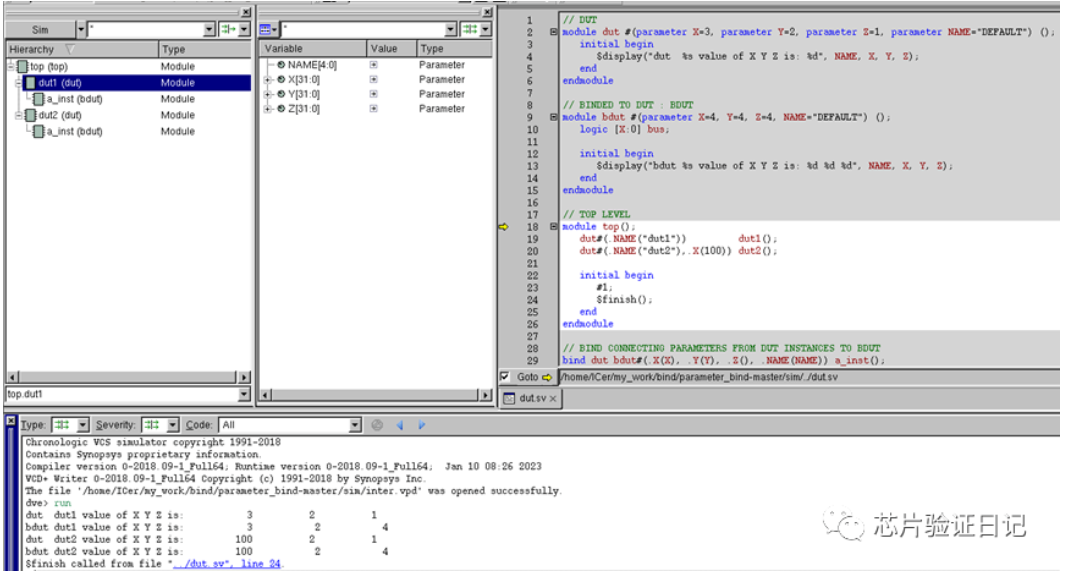

4.4 参数化bind的实例

从前面的例子,我们可以很好的理解SV中的绑定命令允许向模块添加新功能,通常用于向RTL模块添加新的检查。再往深里研究一下,bind还可以继承参数,绑定模块可以根据其使用位置参数化自身。

下面的代码用于演示bind的参数化特性,该特性允许绑定模块(bdut模块)根据其使用位置参数化自身。

当查看bind语句(下图中第29行)时,它使用的所有参数都没有在第29行定义,但当绑定被激活时,它就有了参数化自身的作用域。其实也很好理解,我们可以想象把第29行粘贴到“dut”中;在那里所有的定制参数都将流到“bdut”的实例化中。

需要注意的一个特殊情况是,第29行的“.Z()”参数化为空。这允许“bdut”的默认值接管。第10行根据参数化在“bdut”中创建“逻辑[X]总线”。这可用于生成参数化覆盖点或其他需要参数化的功能。

具体的实验源代码和脚本,请参考分享的网盘链接中的parameter_bind-master目录。

- 通过interface实现bind功能

这在用法上跟上面模块的例子一模一样,只是把module换成interface即可,这里就不再赘述了。 - 赠送实验源码和Makefile脚本

关注微信公众号《芯片验证日记》,后台回复”bind”,可得本文所有的源码和Makefile脚本对应的百度链接,目录如下图所示,这样你就可以在本地复现本文中的所有。 - 参考文献

[1] http://www.sunburst-design.co...

[2]http://www.sunburst-design.co...

[3] IEEE Std 1800™-2017(IEEE Standard for SystemVerilog),23.11;Syntax 23-9 Bind construct syntax (excerpt from Annex A);A.4.1.1 Module instantiation;

[4] Cliff Cummings的著作合集:http://www.sunburst-design.co...

[5] https://blog.csdn.net/lc_2418...

[6] https://www.cnblogs.com/csjt/...

[7] https://asic-world.com/system...

[8] https://tenthousandfailures.c...

写文章不易,如果觉得对您有帮助,麻烦一键三连,或者赏个鸡腿也行!