当设计中使用了多个时钟时,这些时钟域之间的关系可能是synchronous、asynchronous或者exclusive的。如下所示:

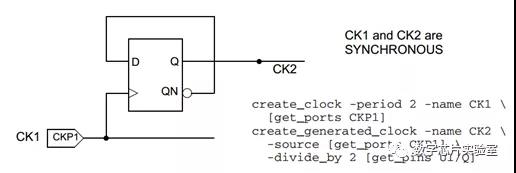

Synchronous:

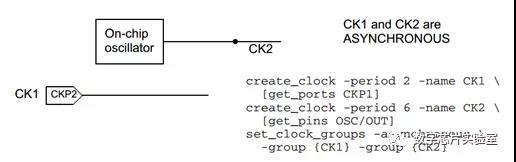

Asynchronous:

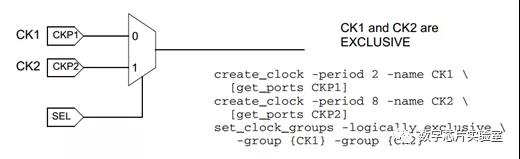

Exclusive:

需要人为地指定设计中时钟之间的关系,EDA工具才能正确地分析不同时钟域之间的路径。

Synchronous Clocks

如果两个时钟共享一个时钟源,并且有固定的相位关系,则两个时钟相互同步。除非特别指定,否则EDA工具会假设任意两个时钟是同步的。

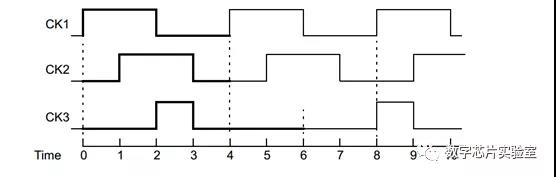

`create_clock -period 4 -name CK1 -waveform {0 2}

create_clock -period 4 -name CK2 -waveform {1 3}

create_clock -period 6 -name CK3 -waveform {2 3}

`

以上三个时钟CK1,CK2,CK3在时间0时刻同步。

在实际的设计阶段,需要通过set_clock_groups -logically_exclusive或set_false_path命令指定不同时钟之间的非同步关系。

Asynchronous Clocks

如果在设计中两个时钟域不相互通信,则它们是异步的。例如,片上振荡器产生的时钟与从外部进入芯片的系统时钟异步。两个时钟域中的时钟边沿可以在任何时间发生,没有任何关系。

在这种情况下,EDA不会检查由一个时钟触发并由另一个时钟捕获的时序路径,就像在两个时钟之间声明false path。

要声明两个时钟之间的异步关系,使用set_clock_groups -asynchronous命令。

Exclusive Clocks

如果两个时钟不会交互,则它们是exclusive的。 例如,电路可能将两个不同的时钟信号复用到一个时钟线上,其中一个是用于正常操作的快速时钟,另一个是低功耗运行的慢速时钟。

在任何给定的时间,只有两个时钟中的一个被使能,所以两个时钟不会交互。

为了防止EDA工具花时间去检查exclusive clocks时钟之间的时序关系,你可以声明时钟之间的false path或使用set_clock_groups -logically_exclusive命令将时钟声明为exclusive。否则,你可以使用case analysis来禁用您不想包含在当前的时钟分析。

声明时钟CK1和CK2是exclusive的:set_clock_groups -logically_exclusive -group {CK1} -group {CK2}

这会使EDA工具忽略从CK1时钟域开始到CK2时钟域结束和从CK2时钟域开始到CK1时钟域结束的任何时序路径。

这就类似于,在CK1至CK2和CK2至CK1之间设置了一个false path。

可以在每个组中指定多个时钟。例如,声明时钟CK1、CK2和CK3、CK4之间是exclusive的:set_clock_groups -logically_exclusive -group {CK1 CK2} -group {CK3 CK4}

如果指定两个以上的组,则每个组相对于另一个组是exclusive的:set_clock_groups -logically_exclusive -group {CK1 CK2} -group {CK3 CK4} -group {CK5}

如果仅指定一个组,则该组对于所有其他时钟是exclusive的:set_clock_groups -logically_exclusive -group {CK1 CK2}

也可以选择为时钟组指定一个名称:set_clock_groups -logically_exclusive -name EX1 -group {CK1 CK2} -group {CK3 CK4}

时钟组可以是物理exclusive,也可以是逻辑exclusive。物理exclusive时钟之间没有串扰,也没有逻辑互动。在这种情况下,使用-physically_exclusive选项而不是-logically_exclusive选项。这可以防止工具执行时钟网络之间的串扰分析。

使用get_clock_relationship命令报告时钟之间的关系:get_clock_relationship {CK1 CK2}

要删除时钟分组声明,使用remove_clock_groups命令:remove_clock_groups -logically_exclusive -name EX1

删除使用set_clock_groups命令进行的所有exclusive时钟分组声明:remove_clock_groups -logically_exclusive -all

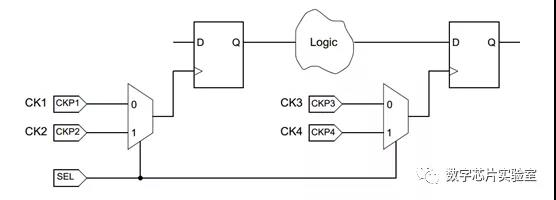

例1:四个时钟和一个选择信号

考虑具有四个时钟CK1,CK2,CK3,CK4的电路示例。默认情况下,EDA工具分析所有时钟组合之间的相互作用。但是,SEL逻辑在任意时刻只会选择两个时钟,CK1和CK3或CK2和CK4。

防止在无关时钟之间进行检查的一种方法是设置false path。例如:

`set_false_path -from CK1-to CK2

set_false_path -from CK2 -to CK1

set_false_path -from CK3 -to CK4

set_false_path -from CK4 -to CK3

set_false_path -from CK1-to CK4

set_false_path -from CK4 -to CK1

set_false_path -from CK2 -to CK3

set_false_path -from CK3-to CK2`

在这种情况下,EDA工具会分析所有时钟的有效组合,而忽略无效的组合。

另一种方法是使用case analysis,在SEL输入上设置逻辑值0或1,

它检查SEL = 0或SEL = 1的特定情况的时间。例如:set_case_analysis 0 [get_ports SEL]

SEL = 0时,只有CK1和CK3有效,CK2和CK4被忽略。

如果你想分析两种情况下,需要进行两次分析:一次SEL = 0,另一次SEL = 1。

另一种实现相同效果的方法是使用set_disable_timing命令。例如,禁用从CKP2和 CKP4端口开始的时序路径检查:set_disable_timing [get_ports {CKP2 CKP4}]

另一种方法是指定哪些时钟可以同时有效,以便EDA工具分析所有有效路径。例如:

`

set_clock_groups -logically_exclusive -name E1 -group {CK1 CK3} -group {CK2 CK4}

set_active_clocks [all_clocks]`

如果您只想考虑SEL = 0的情况,可以使用下列命令:

`set_clock_groups -logically_exclusive -name E1 -group {CK1 CK3} -group {CK2 CK4}

set_active_clocks {CK1,CK3}`

设置时钟CK1和CK3有效,意味着CK2和CK4无效。

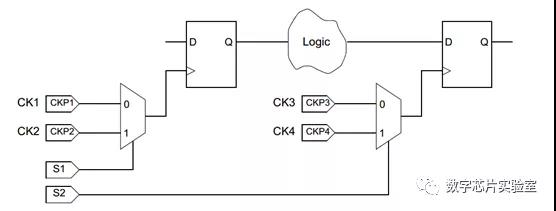

例2:四个时钟和两个选择信号

下面考虑一个电路示例,其中包含两个独立的时钟选择输入S1和S2:

CK1和CK2之间以及CK3和CK4之间的路径无效,但所有其他路径组合都是可能的。

要检查所有有效路径,同时避免无效路径,可以声明false paths:

`set_false_path -from CK1-to CK2

set_false_path -from CK2 -to CK1

set_false_path -from CK3 -to CK4

set_false_path -from CK4 -to CK3`

另一种方法是使用case analysis并在S1和S2上设置逻辑值来检查特定的情况:

`set_case_analysis 0 [get_ports S1]

set_case_analysis 0 [get_ports S2]`

如果使用case analysis分析所有四个案例,则需要进行四次分析,

使用S1-S2 = 00,01,10和11.

另一种方法是使用set_clock_groups和set_active_clocks命令。 例如,

`set_clock_groups -logically_exclusive -name mux1 -group {CK1} -group {CK2}

set_clock_groups -logically_exclusive -name mux2 -group {CK3} -group {CK4}

set_active_clocks {CK1,CK2,CK3,CK4}`

EDA工具分析从CK1到CK3和CK4和从CK2到CK3和CK4的所有有效路径(反方向也是有效的)。

如果只想考虑S1-S2 = 00的情况,可以使用

set_active_clocks命令:

`set_clock_groups -logically_exclusive -name mux1 -group {CK1} -group {CK2}

set_clock_groups -logically_exclusive -name mux2 -group {CK3} -group {CK4}

set_active_clocks {CK1,CK3}`

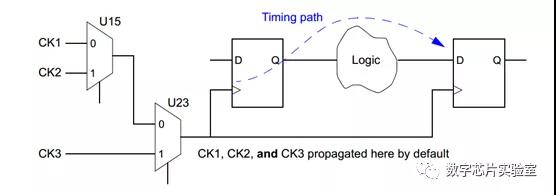

多路复用时钟Exclusivity点

芯片设计通常在不同的时间,对于不同的电路会复用不同的时钟。例如,有时候在工作在高性能模式,有时候降低工作频率节省功耗。 多路复用器(MUX)单元用于选择这些时钟,如下图所示:

默认情况下,EDA工具会考虑触发和捕获时钟的所有组合,例如由CK1触发数据并由CK2捕获数据。 但是,对于如图所示时钟复用器,在任何给定时间,三个时钟中只有一个可以在路径上运行。它们是exclusive 时钟。

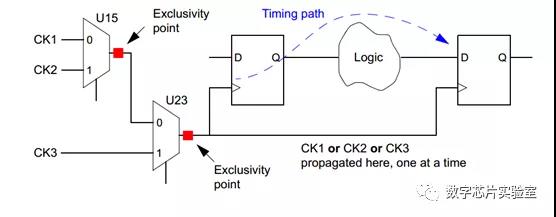

指定exclusive时钟的一种方法是设置“exclusivity points”以标记引脚,在引脚上一次只能传播一个时钟,如下所示:

对于复杂的时钟MUX,此方法更加方便。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/t6pNOcJ-gBsZtNwbuyVw4w

未经作者同意,请勿转载!