本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。

19.1.23 debug:修改关于读回复信号的错误表达,修改细节。

19.5.20 edit:为什么只有写回复通道。

声明:如果没有特别标注,大部分时序图和部分语句来自 ARM AMBA 官方手册(有的时候感觉手册写得太好了,忍不住就直接翻译了。。)

声明2:AXI 总线是 ARM 公司的知识产权

五个独立通道

AXI4 总线的一大特征是它有 5 个独立的传输通道,这些通道都只支持单向传输。作为类比,SPI 总线有 2 条传输通道:MISO, MOSI。SPI 输入输出的数据,大路朝天,各走一条;而作为对比, IIC 协议则只有 SDA 一条通道,输入输出数据只能在这一条通道上分时双向传输。

单向传输的通道意味着通道两端的终端节点是有身份差距的,好比水只能从上游流到下流。在 AXI 总线传输中,通道两端分为 Master 主机与 Slave 从机,主机总是发起读写请求的一方,而我们五大通道的读/写定义就都是根据主机来定义的。

那么五个通道都有谁呢:

- 读地址 read address

- 读数据 read data

- 写地址 write address

- 写数据 write data

- 写回复 write response

5 个是不是很奇怪,你看读/写怎么也得是个 2 的倍数不是,那为什么不是 6 条,为什么没有读响应?其实,读响应借用了读数据通道。至于为什么没有独立的读回复通道,我们之后再讲。

五个独立通道在读写操作中的角色

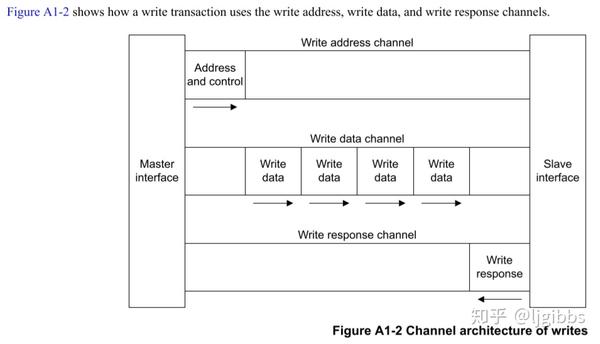

首先是写操作,主机在写地址通道上写地址和控制信息。

在写地址操作结束之后,即主机确保从机已经获得了此次传输的地址和控制信息后,才开始在写数据通道上写数据。

从机在写回复通道上,将此次写传输的状态回复给主机。

一般来说,写数据都发生在写地址操作之后,但也不是绝对的,在有些情况下,可以先写数据。但是,所有情况下,写回复必然是在写数据之后,是对此次写数据的状态回复。

接下来看读操作:

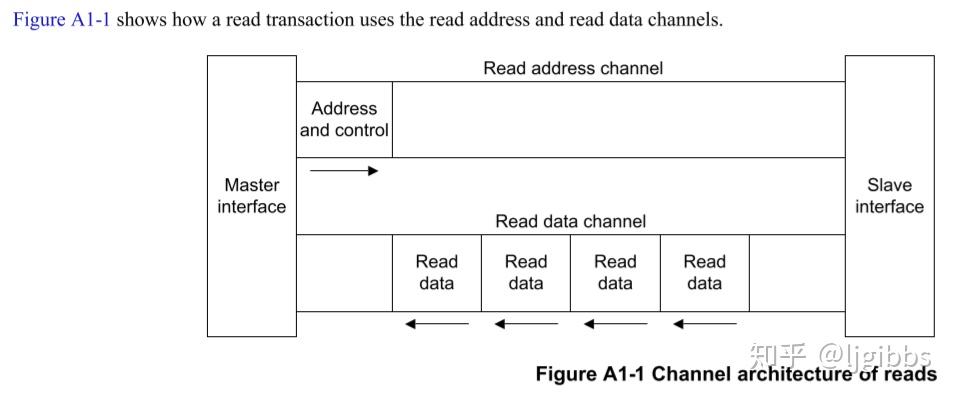

读操作只涉及两个通道,首先主机在读地址通道上写入想要读取的数据的地址以及控制信息。

从机在接收到地址后,将该地址上的数据通过读数据通道发送给主机。

有两点值得注意:一是 AXI 总线支持突发传输,主机可以写入起始地址以及突发传输的字节数,从机将发送起始地址开始,突发传输个数的多个连续地址上的数据。

二是虽然名字为读地址通道,但实际上仍由主机写入地址,只不过是写入要读取数据的地址。读地址通道,这个名字确实有点歧义,主机读操作地址通道表达得更贴切一些。

通道定义

五个通道有一些共同的定义:

每个通道都使用 VALID/READY 握手机制,详情可见:

在读数据以及写数据两条数据通道中,传输一次突发传输中的最后一个数据,必须要给出 LAST 信号,来标识这是此次突发传输中的最后一个数据。如果缺少 LAST 信号会破坏 AXI 总线的工作状态。

突发传输又称猝发传输,详情可见:

读地址通道与写地址通道:

在这两条通道上传输地址和控制信息,读写操作都拥有各自的地址通道。地址位宽一般限制为32位。

读数据通道:

读数据通道上包括从机发送给主机的读数据以及读操作完成状态回复,具体的读操作状态回复情况会在之后讨论。数据的宽度可以是8,16,64,128,256,512 或者是 1024 比特。

写数据通道:

写数据的宽度和读数据通道的数据位宽相同,写通道有一点读通道所不具有的特性是有 STROBE 信号,用于标识写数据中有效的传输字节,即有些无效的数据,出于减少主机工作量的目的,或者在读写宽度不对称时,被放到写数据通道上和有效数据一起发送。而 STROBE 的信号的作用就是标识出这些无用的数据,告知从机不需要接收无用数据。(Master:我太懒,以至于把所有信号都送过来了)

写回复通道:

用于从机将写完成情况回复给主机。所有的写传输操作都需要在写回复通道上接收此次写传输操作的完成情况。值得注意的是写回复是针对一次突发传输的,而不是针对每一次的写数据操作的。(一次突发传输包括了多次写操作)

那么问题来了,为什么只有写回复通道而没有读回复通道呢?

这个问题可以从数据流向看出来,主机在读取数据时,数据在读通道上传输,流向为从机到主机。而读回复由从机向主机报告读操作的情况,信号的数据流向也是从机到主机,所以读回复可以合并在读数据通道中。

但写回复通道的数据流向就和写数据相反。写数据是从主机到从机,而写回复为从机报告写操作的完成情况,流向为从机到主机,无法合并到写数据通道中,另一方面,写回复又是不可或缺的,所以就有了一条独立的写回复通道。

通道上的信号们

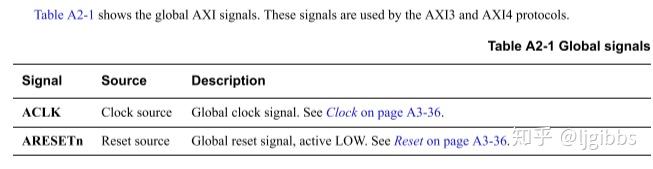

全局信号

AXI 总线中有两个全局信号:ACLK,全局的时钟信号,所有的传输操作都发生在 ACLK 的上升沿。ARESETn,全局复位信号,低电平有效。在复位问题上,AXI 规定了一些细节,会在后续的文章中讨论。

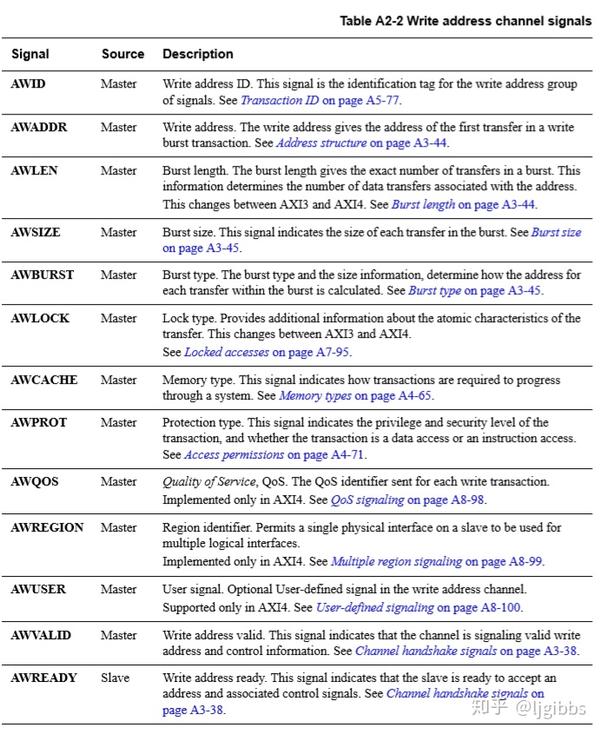

写地址通道

写地址通道的信号可以分为 3 部分:经常用到的基础信号,突发传输有关的信号以及和内存访问相关以及其他的在基础阶段不是很常用的信号。

基础信号即 AWADDR:你想要写入的地址,AWVALID 以及 AWREADY:所有通道都使用的握手信号。

突发传输指的是传输一次起始地址后,进行多次地址上连续的读写操作。突发传输有关的操作包括:AWLEN:突发传输的长度,即在一次突发传输中数据传输的个数。AWSIZE:每次突发传输中的数据传输的位宽。AWBURST:突发传输的类型。

其他信号包括和内存原子操作有关的 AWLOCK,AWCACHE,AWPROT 以及用于用户自定义的 AWUSER 信号,都将在以后的文章涉及。(等我自己先用到再说)

读地址通道

读地址通道和写地址通道的信号十分类似,就不再从 specification 中截图以及介绍了。

写数据通道

值得注意的是 AXI4 不再支持 WID 信号,这和 AXI4 的乱序机制有关,AXI4 规定所有数据通道的数据必须顺序发送。

WDATA 与常见的握手信号不再赘述,WDATA 的可使用位宽可以见上文。WSTRB 信号用于标记传输数据中有效的字节,每个 WSTRB 位对应一个字节的位宽,比如数据位宽为 64 位,那么 WSTRB 信号的位宽就是 1 个字节,共 8 位。(感谢评论区纠正)

WLAST 标识一次突发传输中最后一次数据传输,如果没有正确的 WLAST 的信号,就会造成写入地址的混乱,导致从机无法正确接收写数据,从而造成从机不再拉高 READY 信号的现象。

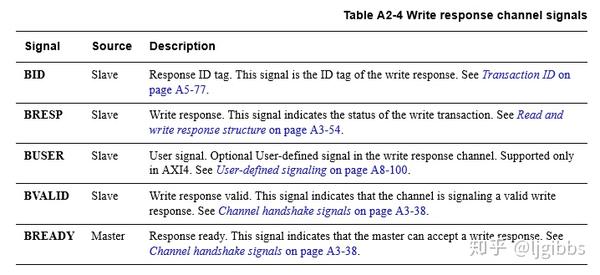

写回复通道

与写数据通道不同,写回复通道支持 BID,即支持乱序的写回复,关于乱序的问题,我们稍后再谈。BRESP 回复上一次的写状态。

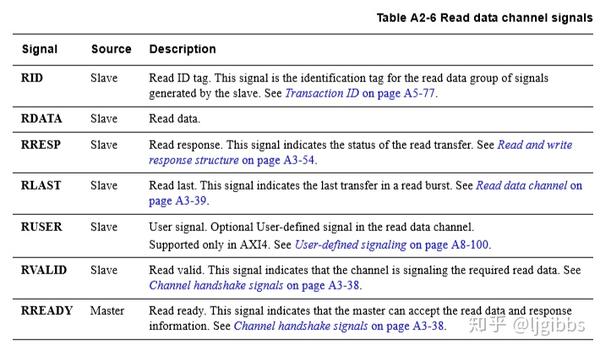

读数据通道

读数据通道与写数据通道类似,区别有两点:一,支持 RID 信号。二,因为读回复信息在读数据通道上传递,所以集成了 RRESP 信号,用于返回读状态,值得注意的是读回复信号和读数据一样,发送方(source)为从机(slave)。

结语

本文中我们了解了 AXI 总线的架构,它的五大通道以及各自的信号,最简单的读写操作流程。在接下来的文章中,我们会更加深入到:各通道的握手机制以及传输细则,突发传输以及乱序传输的规则与实例中。

更多AMBA协议相关文章请关注极术专栏Arm AMBA 协议集

| 文件名 | 大小 | 下载次数 | 操作 |

|---|---|---|---|

| IHI0022E_amba_axi_and_ace_protocol_spec.pdf | 1.92MB | 495 | 下载 |

| hello_axi.pdf | 2.15MB | 128 | 下载 |