作者:LJgibbs

来源:https://zhuanlan.zhihu.com/p/110037596

依稀记得从 ISE 切换到 Vivado 时的蒙蔽

比如仿真修改源文件或者 testbench 时,不能通过重新 run do 文件来 relaunch 设计。需要基于生成的 xx\_compile.do 制作一个 do 文件来 relauch 设计。可以参考下方文章。

https://zhuanlan.zhihu.com/p/36952401

本质上,re do 文件重新编译了所有源文件和 testbench 来把修改后的设计添加到 Modelsim 中,并重新仿真。但其实,我们可以直接在 Modelsim 中操作,来重新编译某个文件。

使用 vlog 命令,比如

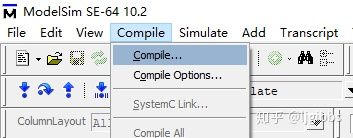

vlog -reportprogress 300 -work work D:ipsec_inbnd_auth_hdr_set_zero.vvlog 命令用于编译 Verilog 文件。这条命令也对应 GUI 操作,Compile-Compile

-在文件框中选择修改过或者新添加的源文件,Compile 即可

-然后重新运行仿真

这种方法适合修改单个文件的情况,相比 redo 文件适合多个文件都经过修改的情况下,重新载入整个设计。

可以使用命令来快速操作

vlog -reportprogress 300 -work work D:ipsec_inbnd_auth_hdr_set_zero.v

restart -f;run 55usrestart -f 选项可以摆脱这个对话框哦,学到了

推荐阅读

关注此系列,请关注专栏FPGA的逻辑