集微直播间自开播以来获得了大量来自行业的关注与好评。其中“集微公开课”栏目联合行业头部企业,通过线上直播的方式分享精彩主题内容,同时设立直播间文字提问互动环节。集微网希望将“集微公开课”栏目打造成中国ICT产业最专业、优质的线上培训课程,深化产教融合,助力中国ICT产业发展。

5月13日(周三)上午10点,第十一期“集微公开课”邀请到北京亚科鸿禹电子有限公司市场总监白建东,带来以《加速您的SoC/ASIC验证》为主题的精彩演讲。

近年来,随着国家加快发展集成电路、出台相关扶持政策,市场涌现IC热潮。不过在集成电路发展过程中,SoC的设计规模和复杂程度急速膨胀,加上芯片制造失败风险率高,使得功能性验证的重要性与日俱增,检测芯片是否存在设计缺陷或是工艺缺陷对于提高IC设计效率、日后能否成功流片意义重大。

作为专注于“SoC/ASIC仿真验证实现”的创新型公司,北京亚科鸿禹电子有限公司在《加速您的SoC/ASIC验证》为主题的精彩演讲中详解了这一问题答案。此次公开课观看人数破万,干货满满!

如何进行有效的验证

FPGA原型验证为什么可以进行有效验证呢?亚科鸿禹市场总监白建东指出,FPGA原型验证系统可以帮助客户尽早地完成软、硬件集成与软件(操作系统、app)等开发工作,具体可归纳为以下四点原因。

首先,FPGA是速度和精度的结合。通过FPGA原型验证系统,将底层硬件建立完毕,从而搭建起真实的软件世界;其次,在物理接口测试方面,可以通过环境搭建,从而实现例如HDMI2.0接口的真实数据的输入和输出,进而看到真实的编解码效果;第三是可以进行概念验证,即早期的项目结果设想验证;最后因为FPGA可以通过FLASH实现独立配置,也就是脱离开服务器环境进行验证。

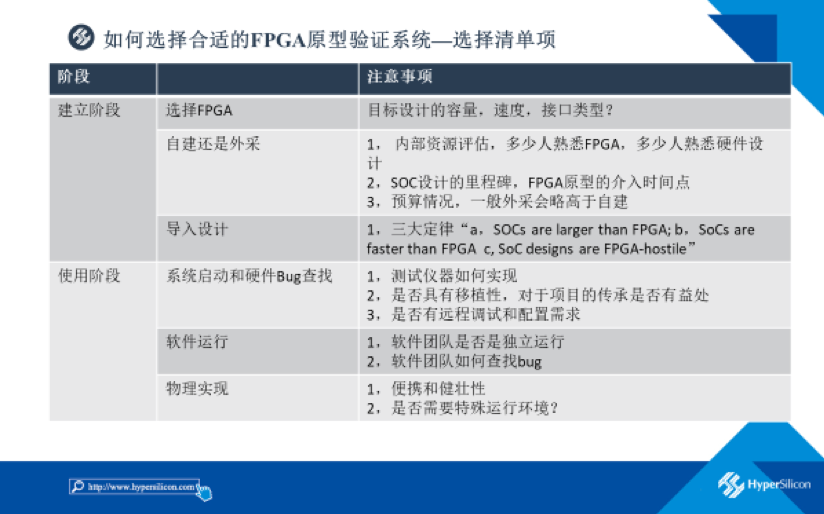

FPGA如描述般奏效,而选择适合自己产品的FPGA原型验证同样关键。对此,白建东提醒在建立与使用FPGA原型阶段都要着重关注。

在已有ASIC的前提下,需先确定FPGA原型,而后确认FPGA是自建还是外采,接下来是了解产品验证预期。白建东解释说,一直以来SoC/ASIC都遵循着三大定律(如图),这意味着单个FPGA可能无法完成验证,即需要进行设计分割,最后再导入设计。

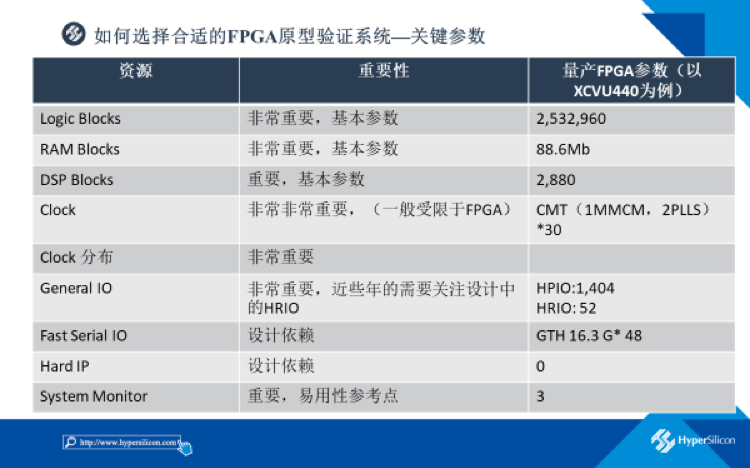

与此同时,进行FPGA原型验证时关键参数也很重要。

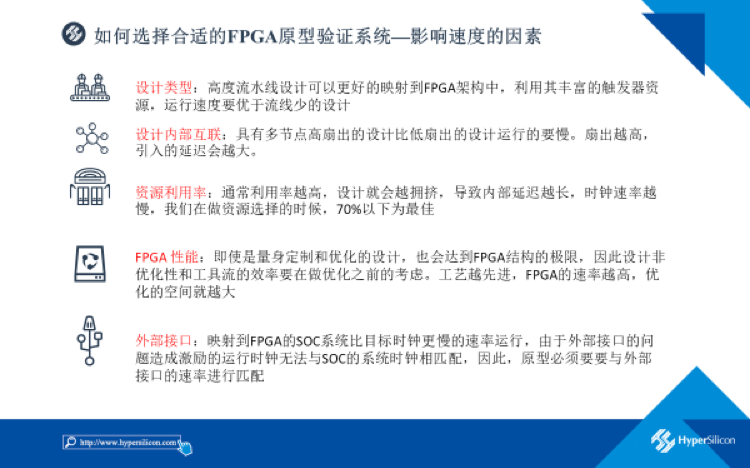

另外,白建东还分析指出,设计类型、设计内部互联、资源利用率、FPGA性能以及外部接口均会影响到FPGA原型验证系统的验证速度。

FPGA验证中的代码优化

在选择了合适的FPGA原型验证系统后,便需要对代码进行优化。

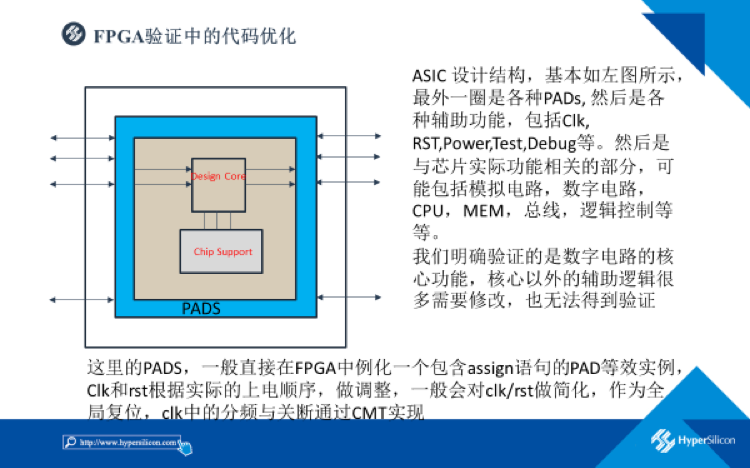

白建东强调,在ASIC中,明确验证的是数字电路的核心功能,而核心以外的辅助逻辑有很多是需要修改的,因此无法得到有效验证,所以这时候一定要对PADs进行替换。

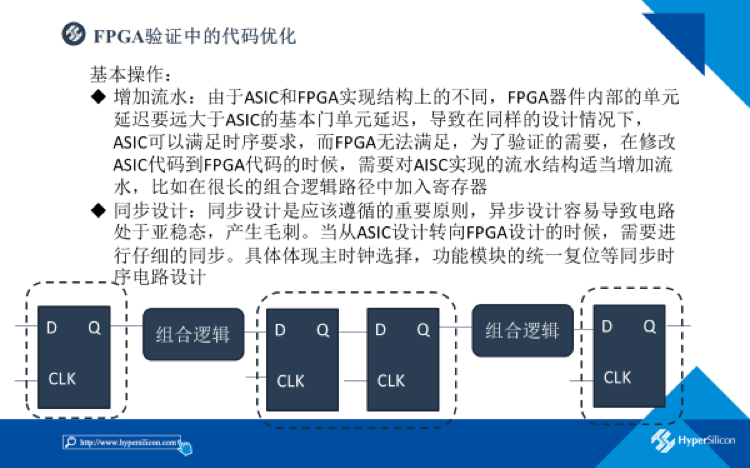

此外,在进行代码优化时,一方面要增加流水,另一方面要同步设计。

FPGA验证中的设计分割

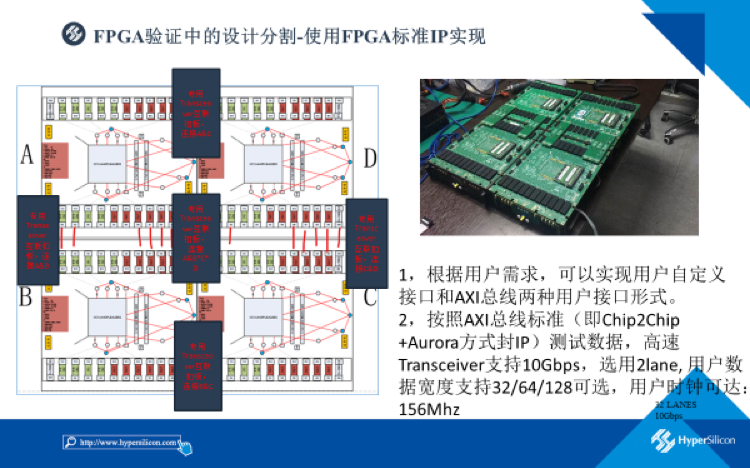

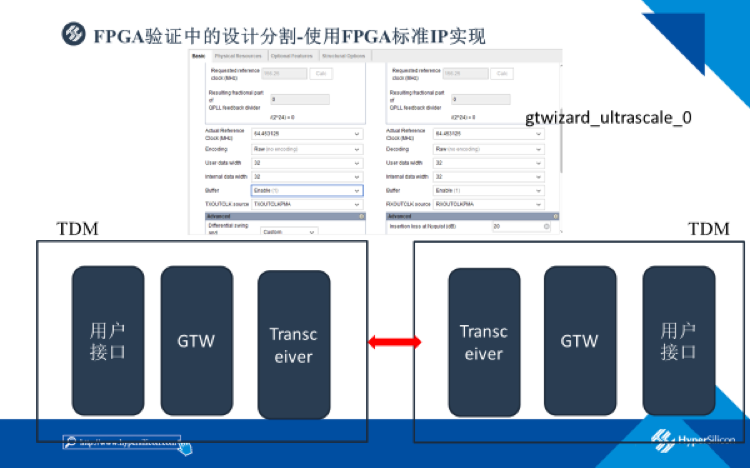

需要注意的是,当单个FPGA无法完成验证,则需要使用FPGA标准IP实现分割。以亚科鸿禹的产品为例,白建东指出,根据用户需求,可以实现用户自定义接口和AXI总线两种用户接口形式。

基于FPGA的硬件仿真加速器

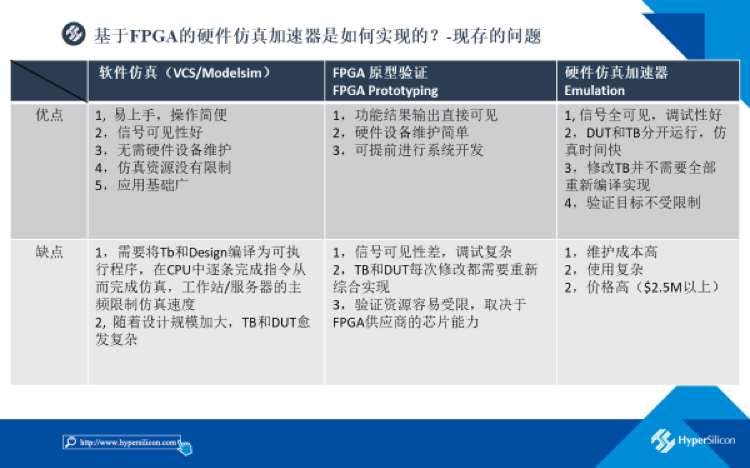

除了FPGA原型验证,硬件仿真加速器也是最为有效的验证手段。尽管硬件仿真加速器维护成本高、价格高,且使用较复杂,但该验证方法具备信号全可见、调试性好;DUT和TB分开运行,仿真时间快;修改TB并不需要全部重新编译实现;验证目标也不受限制的优点。

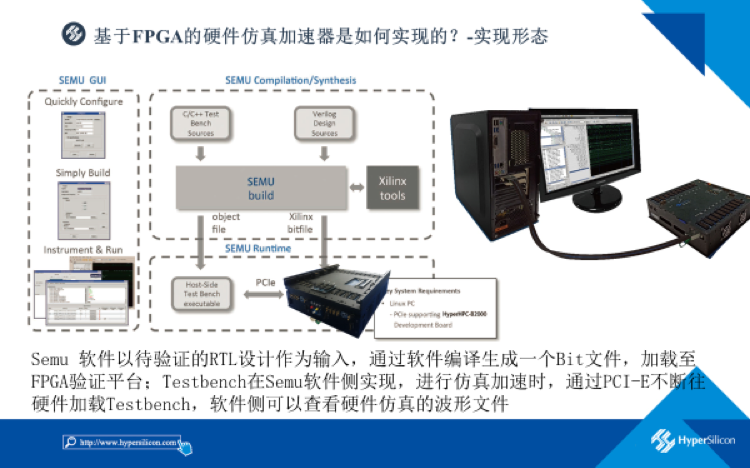

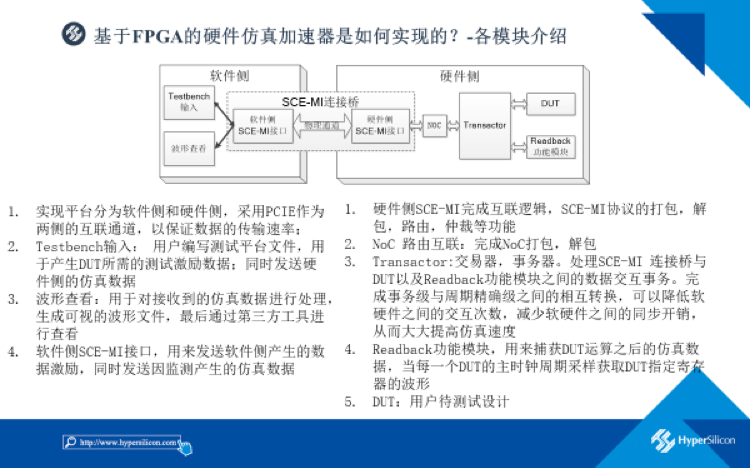

那么基于FPGA的硬件仿真加速器是如何提供实时的验证环境,增加验证的可调试性的呢?

最后白建东介绍,Semu软件以待验证的RTL设计作为输入,通过软件编译生成一个Bit文件,加载至FPGA验证平台;Testbench在Semu软件侧实现,进行仿真加速时,通过PCI-E不断往硬件加载Testbench,软件侧可以查看硬件仿真的波形文件。