By the way,MicroSemi 的全球客户支持不错,在他们网站留下问题,会有专门的工程师邮件联系你帮助解决问题。比某 X 家的论坛发帖效率高多了。而且只需要你用企业邮箱,也不需要你提供购买凭证什么的。

SignalTap, Chipscope ,Hardware debug Manager 对于 FPGA 工程师来说都是很熟悉的名字。他们作为 Altera(Intel)/Xilinx 集成开发环境中的在线调试组件,能够实时地分析芯片中的信号状态,为工程师定位解决问题提供了很大帮助。

作者:李凡

来源: https://zhuanlan.zhihu.com/p/88314552

在这里我想说,Synospsy Identify 也配拥有姓名,特别是你在使用 MicroSemi 这一相对小众的 FPGA 品牌时,MS 的集成开发环境 Libero 中没有自家的综合器以及在线调试组件,其使用的是 Synospsy synplify / Identify, 前者是综合器,后者是其配套的调试组件。

本文将结合 Identify 提供的文档来讲解在线逻辑分析调试组件的原理,部署步骤以及再 MicroSemi 中的使用方式。

Debug 系统构成

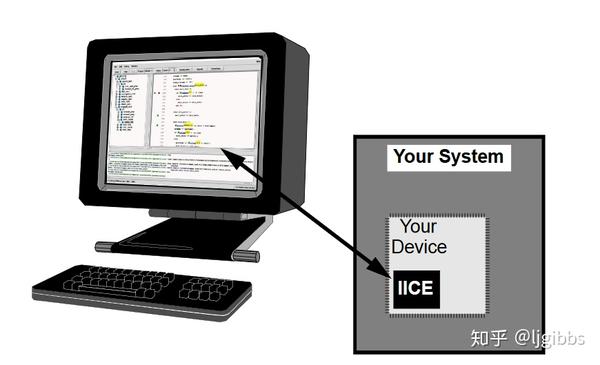

Debug 系统由上位机(说人话:你运行调试环境的电脑),FPGA 设备以及两者的 JTAG 线缆构成。

Identify 系列软件运行在你的电脑中,右边的方块中的方块代表你的 FPGA 设备,其上运行着你的用户逻辑。小的黑色方块代表 Identify 在你的逻辑中插入的逻辑信号分析核 IICE。逻辑分析核相当于一个信号采集器,捕捉并存储信号后传输到上位机中运行的 Identify 软件中。上位机和 FPGA 通过 JTAG 调试线连接。在软件中可以查看捕捉到的信号及其波形。

Debug 流程

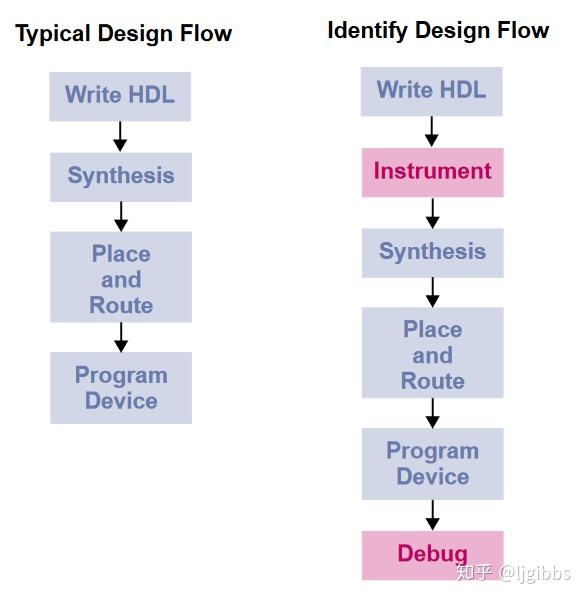

典型的,未插入调试核的设计流程如左图所示,编写 Verilog 代码,综合,布局布线之后将生成的比特流编程到器件中。

如果要使用在线逻辑分析仪进行调试,只需要比原本的流程增加一步,插入逻辑分析核,在 identify 中,这步被称为 Instrument。插入逻辑分析核该步在综合之前,在将含有逻辑分析核的比特流下载到设备后,就可以在电脑上通过软件进行逻辑分析 Debug 了。

在其他平台,比如 xilinx 的 vivado 环境中,也可以在综合之后插入逻辑分析核。

Debug 组件构成

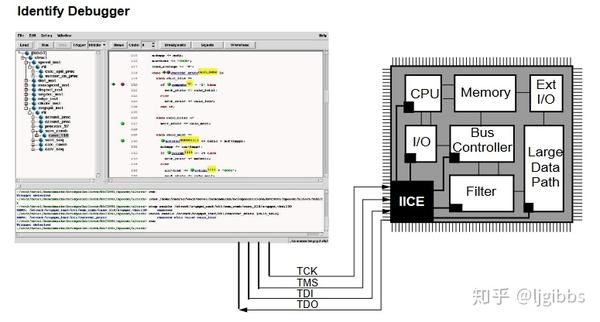

Identify 调试组件共有三项,其中两项为软件,一项为插入用户逻辑的 IP 核。

IP 核 IICE,用于捕获信号,会像上图所示那样插入到用户逻辑中,它用于采集其他用户逻辑的信号,并将采样的信号返回到上位机软件。

IICE 由控制器和采集器构成,采集器采集信号,控制器负责通过 JTAG 与上位机通信。IICE 内部有信号缓存 RAM,可以在采集信号触发后采集一定的采样点数。使用 IICE 时会消耗板上的 RAM 资源,越大的 RAM 也就可以支持更多的信号以及更深的采样深度。

另外两项是软件 Identify Instrumentor ,用于分析 HDL 代码,查看哪些代码中的变量可以被设为待观察信号,也可以设置采样的特性,比如采样深度,采样模式等等。工具会根据用户的设定以及观察信号的数量自动生成对应的 IICE 采集核并插入到用户的设计中去。

Identify Debugger 是另一项软件组件,如果说上面那个软件用于在综合之前的 instrument 阶段插入调试核,那么 debugger 就可以在编程芯片之后,在程序运行期间,观察前一步中设定的信号,即 debug 步骤。

debugger 可以设置捕捉信号的触发条件,假设需要观察一个上升沿有效,持续若干周期的信号,就可以将触发条件设为这个信号的上升沿。信号上升沿到来后,IICE 会开始采集若干周期的信号,这样就可以观察信号上升沿到来之后的变化了。

如何进行一次调试

那么问题来了,如何具体地在 Microsemi 的环境和平台中进行一次在线调试呢。那么我们可以根据先前那张 Flow 图,分为两个步骤来做:instrument 和 debug

instrument

instrument 阶段是指在当前的 HDL 代码基础上,使用 Identify Instrumentor 插入调试核。

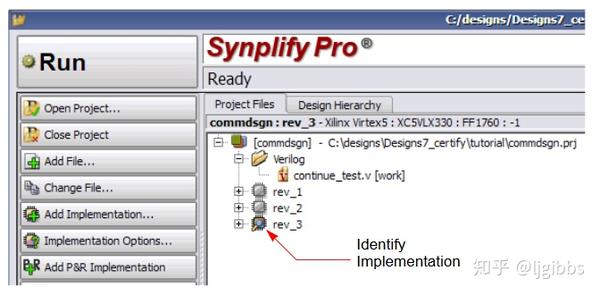

在 MicroSemi 的开发环境 Libero 中,我们首先完成代码和工程的开发,在进入综合阶段时,在软件左侧的 Design Flow 栏中 右键选择 Synthesis - open inactively 在外部打开 配套 Libero 使用的综合器,Synplify ,得到这样一个界面。

在外部打开的 Synplify 界面

图中箭头指向小图标被称为一个 implementation,一般地,当你在添加 identify 调试核之前,你有一个图标,但你的图标上没有那个放大镜,这就需要在图标右键选择新增一个 Identify Implementation,得到一个图中箭头所示那样的图标。

Identify Implementation

右键新的,带有放大镜的图标,选择 Identify Instrumentor 打开软件。

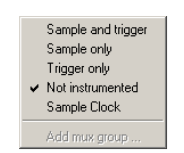

这左侧能看到自己的 Verilog 代码层级,打开代码后我们发现变量之前都出现了一个眼镜图标,眼镜代表可观察的信号。空白的眼镜代表未添加观察的信号,在信号上右键菜单中我们可以将信号设置为 sample, trigger, sample clock。

sample clock 表示采样时钟,所有在 IICE 中添加的信号都会在 sample clock 的边沿进行采样,设为 sample clock 的信号前会出现一个时钟状的图标。

设置为 sample 和 trigger 的信号都将作为被采样信号,区别在于 sample 信号只能被采样,而 trigger 信号可以作为触发采集的条件,当然你可以把一个信号同时设置为 sample 和 trigger 。

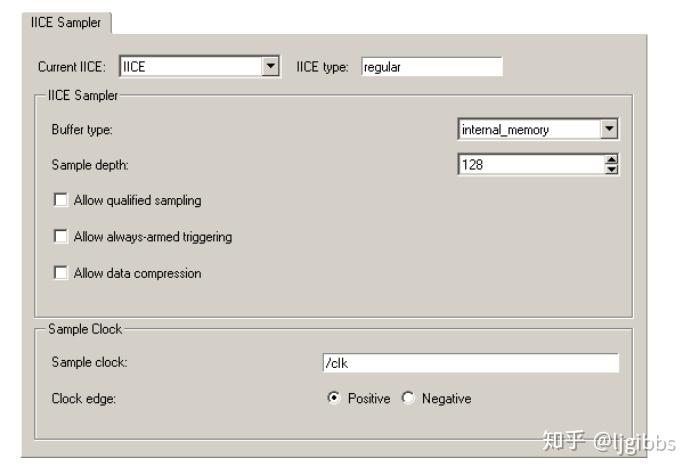

在设置待采集的信号,采样时钟之后,可以在 IICE 中设置采样深度等采集属性,在窗口上方可以找到这个图标

一般我们也就会设置一下采样深度,值得注意的是要量自己剩余的 BRAM 资源而行,采集一时爽,一直采集一直爽。但 BRAM 用光可就没办法。(最好不要超过 80% 资源)

在完成所有设置之后,就可以选择上述图标,保存设置,然后就可以关闭 Identify Instrumentor ,返回到 Synplify 的界面,这边根据我的使用经历建议做两件事。一是把除了正在使用的 implementation (带有放大镜的那个)之外的 implementation 统统删除;二是在菜单中选择 Save All 保存一下这个工程。

之后就可以关闭 Synplify ,回到 Libero 中,按照之前的流程,综合,P&R,生成比特,下载即可。

Debug

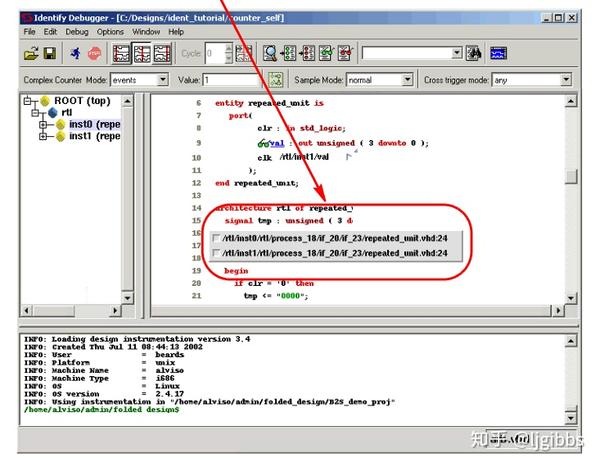

下载比特之后,同样在左侧的 Flow 界面,选择 Identify Debugger 打开如下界面。

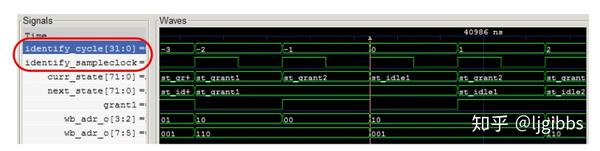

我们可以在不设置任何触发条件的情况,进行一次强制触发,捕获当前的波形。直接选择 Run

在等待软件和硬件通信后,(这个过程可能有点长),并将采样结果下载到电脑后,就可以查看信号的值以及信号波形,信号的值会显示在信号边上,选择如下的图标可以在外部窗口打开一个工具查看波形。

那如果我们不想强制触发,而是想在某个条件之后捕获波形该怎么做?

如下在信号上右键,选择设置 trigger 表达式。

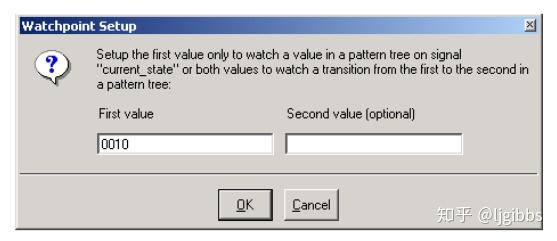

设置在何值的情况下触发,可以只设置 First Value,也可设置可选的 Second Value,这样可以在信号变化的时刻捕获。比如要捕获上升沿,就可以分为设为 1'b0,1'b1。

结语

本文简单介绍了下 MicroSemi 平台上的在线调试工具,及其使用流程。MicroSemi 相对于 X/I 来说小众很多,笔者也是最近做一个项目用到这个平台,所以做了一些了解。这里非常欢迎有使用经历的朋友一起交流哈(真的有么-\_-||)

PS:可能会有后续文章介绍一些使用中的小技巧。

PSS:如果有读者感兴趣,我可能多加一些自己截的图片,把这个教程做仔细。

参考资料

MicroSemi 提供的关于 Identify 的文档,本文大部分图片来自这份文档。

https://www.microsemi.com/document-portal/doc\_view/132760-synopsys-identify-me-h-2013-03m-sp1-user-guide

想了解 Xilinx 平台上的 ila,vio,可以看这篇专栏文章:

叽叽喳喳:https://zhuanlan.zhihu.com/p/72402743

推荐阅读

关注此系列,请关注专栏FPGA的逻辑