ICG(Intergrated Clock Gating)作为low power的设计手法之一,已经在实际中得到广泛应用。它们能够在某些时候将某些clock关断从而达到降低功耗的目的。然而从时序的角度,经常会发生ICG的setup难以收敛的情况。

为什么会出现这种情况呢?

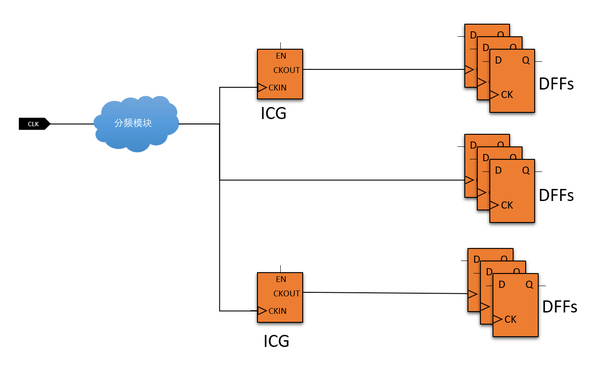

下图展示了一种简单的带ICG的clock tree结构:

一般每个ICG会控制一个或多个DFF,通过某个DFF传递过来的控制信号控制ICG的开启或者关断。

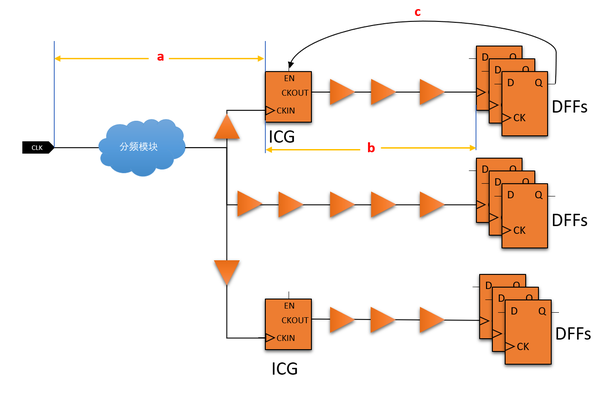

然而,在CTS(clock tree synthesis)工具或者命令综合时钟树的时候,ICG不会被看作sink因此并不会作为balance对象,因此就会出现如下这种结果:

由上图可以看出,在分析setup时:

launck clk delay = a + b

capture clk delay = a

因此,对于ICG的setup path,天然存在clock skew:b ,而skew的大小完全取决于ICG距离sink DFF有多远。

在出现setup violation的ICG path上,比较多见的就是因为ICG和sink DFF的clock之间存在较多逻辑或者物理上距离较远,从而导致skew较大而发生setup violation。

针对这种现象,在实际设计中,我们可能会考虑将出现setup violation的ICG尽量放在sin DFF附近以减小skew。与此同时,EDA工具也提供命令来收紧ICG的timing constraint来迫使工具来优化这些path,比如set\_clock\_gating\_check命令。

往期问题答案:

fix hold violations时,插入buffer或者delay cell的位置,是靠近launch端还是capture端,还是并无任何要求呢?

在逻辑和物理上都应该尽量靠近capture端,也就是endpoint。在逻辑上更靠近endpoint能够保证插入的cells只会影响到有violation的path,物理上更靠近endpoint能够有效避免DRV,因为修hold时加入的cell普遍驱动能力较弱。

相关文章

如果大家有任何后端技术与职业发展方面的问题,抑或关于数字后端感兴趣的技术话题想要了解和探讨,欢迎关注我的知乎专栏: 数字IC后端设计工程师修炼之路同时欢迎关注微信公众号:数字后端芯讲堂,一起探讨技术,共同提升!

本极术专栏也会同步更新芯片设计后端的技术干货,也请关注数字IC后端设计工程师修炼之路。