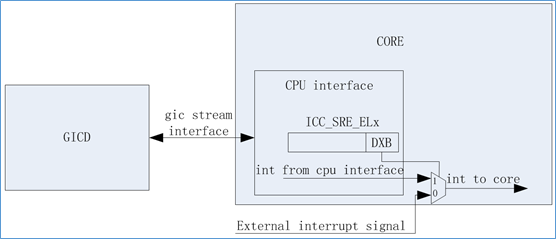

在GICv2架构中,GIC与core之间,是直接通过irq,fiq管脚,传递中断信号。但是在GICv3架构中,GIC通过gic stream接口向cpu interface传递中断信息,然后由cpu interface向core传递中断信息,而且,cpu interface被设计在了core当中。

GICv3支持中断bypass功能,以下是我画的一个框图:

对于core而言,中断有2种(不考虑虚拟中断),分别是IRQ和FIQ。

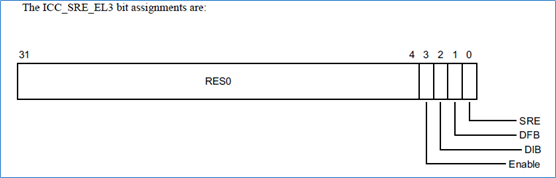

在ICC_SRE_ELx寄存器,有DFB和DIB bit,分别控制FIQ,IRQ是否bypass。

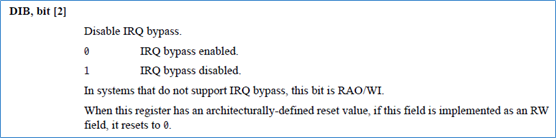

对于DIB bit的描述:

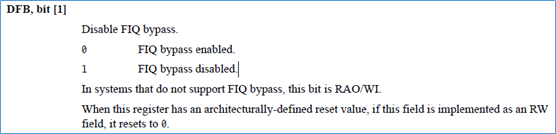

对于DFB bit的描述:

这2个bit,复位值都是0,表示系统在复位后,中断bypass功能是开启的,此时外部的中断信号,是直接输入到core中的。

当软件,关闭中断bypass后,此时,才是由cpu interface给core发送中断,而忽略掉外部发送的中断。

在gicv3架构描述中,提到了中断bypass功能,会受到下面几个配置的影响:

一个是,是否运行系统寄存器访问icc寄存器,也就是ICC_CTLR.SRE bit是否为高,如果允许系统寄存器访问icc寄存器,那么中断bypass功能是禁止的。

一个是,ICC_SRE寄存器,由当前设计中支持的最高EL级的ICC_SRE寄存器的DFB和DIB bit来控制。

最后一个,就是中断分组使能,也就是ICC_IGPREN0_EL1和ICC_IGRPEN1_EL1的enable bit。

如果需要开启中断bypass功能,那么需要将中断分组使能给关掉。

以下是FIQ中断bypass的伪代码:

IRQ的处理,和FIQ是一致的。

系列其他篇

原文首发于骏的世界博客

作者:卢骏.

更多Arm技术相关的文章请关注Arm技术博客极术专栏,每日更新。