首先介绍下indago工具,也就是debug analyzer app。

在debug uvm验证环境时,我们一般是通过增加打印,然后仿真,根据仿真打印的log,来确定问题。如果打印加得不够,还得修改源代码,增加代码代码。

有了indago工具之后,就再也不需要在环境中,增加额外的打印代码。因为indago工具,可以查看仿真时刻的任意状态。

那indago是如何实现的了?其中的关键,就在于,使用irun工具仿真的时候,需要产生indago database,将仿真过程中的信息,给记录下来。最后使用indago工具,载入这个database,实现信息的回看。

下面,就说一下,如何生成这个indago database。

一、编译阶段

在编译阶段,要加入如下三个选项:

◾-ida: 使能indago debug analyzer。 如果使用xrun工具,不需要加该选项。

◾-linedebug:支持代码行调试,必加

◾-uvmlinedebug: 支持uvm库代码行调试,可选

二、仿真阶段

在仿真阶段,需要加入 +UVM_HYPERLINKS=ON 选项,和-input run.tcl 选项,来指定仿真所需要的tcl文件。

在run.tcl中,可以精细化的控制indago database生成。因为产生indago database会降低仿真速度,因此需要使用run.tcl,来精细化控制,database的生成过程。

下面是一个参考的run.tcl脚本。

1. ida_probe -log -sv_flow -uvm_reg -log_objects -sv_modules -wave -wave_probe_args="top_tb -depth all –all memories"

2. run

3. exit

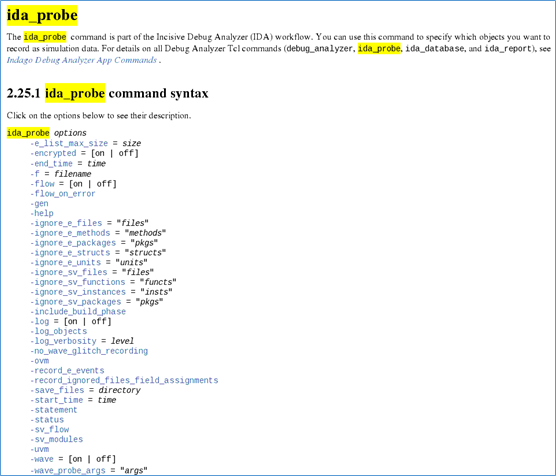

三、ida_probe命令

ida_probe,指定database中记录产生的数据。

这个命令很重要,因为后面indago能回看的数据,完全是由这个命令,来指定的。比如,ida_probe,指定了database要记录波形,那么将来在indago工具中,才可以看到波形。

下图,是ida_probe命令的说明:

这里,说明一下这个命令的一些常用选项:

1、-start_time/-end_time

指定database记录仿真状态的起始时间和结束时间。主要用来,记录关键一段仿真过程的状态。

2、-log

记录打印的信息

3、-log_objects

记录打印信息中的,动态对象。

4、-uvm

记录uvm package信息。如果使用这个选项,需要编译带上 –linedebug 选项。

开启这个选项,会将uvm的基类,比如uvm_test,uvm_env等这些基类进行记录,这样将来在indago工具中,可以在这些基类中,回看仿真过程。

如果不关心uvm基类的底层过程,可以不用加这个选项。

5、-uvm_reg

记录uvm_reg的信息,需要在编译选项,加入 –uvmlinedebug。当uvm环境中,有uvm寄存器模型,需要将该选项加上。

6、-wava/-wave_probe_args=xxx

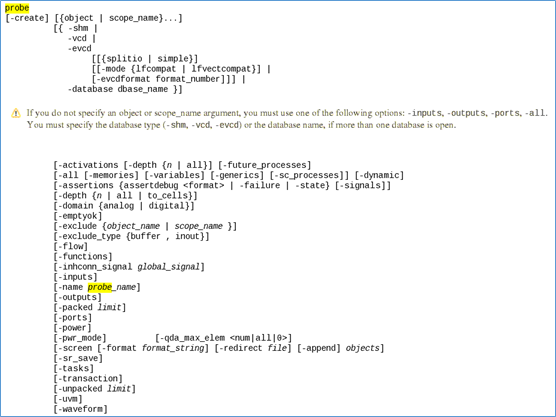

-wave开启波形记录。 -wave_probe_args,指定波形记录的形式。xxx参数,是传递给probe的参数。

对于probe命令,其说明如下:

如-wave_probe_args= "dut_top -depth all –all memories",表示记录dut_top模块的内部信号波形,以及该模块之下所有模块的内部波形。因为还有-all选项,因此还会记录memory的波形。

7、-sv_files

允许记录systemverilog文件

8、-sv_flow

允许记录systemverilog信息

9、-sv_modules

允许记录systemverilog的module信息。默认为是不记录systemverilog的module信息的。

10、-sv_packages= "pkg"

记录指定systemverilog package的信息

11、-include_build_phase

记录systemverilog flow中,build phase的信息。默认为uvm,不记录build phase的信息,如果想要记录,需要加入这个选项。

12、-ignore_sv_files= "files"

不记录,指定的sv文件。可以使用匹配表达式

13、-ignore_sv_instances= "insts"

不记录,指定的sv的模块。

-ignore_sv_instances= "top.router",不记录top下router模块的信息。top.router必须是module,而不能是动态对象(比如class对象)。

14、-ignore_sv_packages= "pkgs"

不记录,指定的systemverilog package信息。

15、-ignore_sv_functions= "functs"

不记录,指定systemverilog的function和task。

例如,-ignore_sv_functions= "bar*" ,不记录bar开头的函数和任务

16、例子

ida_probe –log –sv_flow –ignore_sv_packages="cdn_gpio cdn_mem"

表示,记录log,以及systemverilog,但是不记录cnd_gpio和cdn_mem这2个package。

ida_probe –log –start_time=100ns –end_time=20000ns –wave –wave_probe_args="dut_top –depth all"

表示,记录从100ns开始,200000ns结束,在这一段时间中,记录log,和波形,波形记录dut_top模块以及这个模块之下的所有信息。

17、ida_probe命令小结

因为使用ida_probe之后,会降低仿真速度,因此需要合理的使用提供的选项,记录关键的信息。而不是全记录。

比如不需要记录RTL波形,那么就不要加-wave选项。

比如,关心一段时间的仿真状态,那么就要使用-start_time/-end_time,这两个选项。来限定记录的时间。

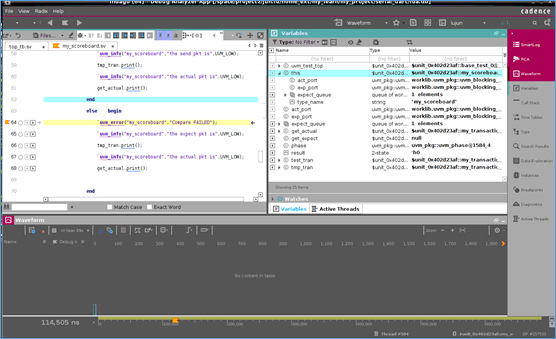

四、indago启动

通过run.tcl脚本,指定产生database的信息。irun工具仿真完毕后,会在当前目录下,生成ida.db文件夹。

直接使用indago命令,启动indago工具,indago会自动载入ida.db文件夹内容。

界面如下所示:

之后,就要介绍下,该软件,如何使用。

更多相关阅读

vcs回退交互式仿真

交互式仿真下dve和verdi中查看二维数组值

cadence indago征程(一)indago系列工具介绍