四、channel interaface

channel interface是用来使不同coresight组件之间传递event使用。使用两个组件来实现:

◾CTM: cross trigger matrix, 接收CTI的channel信号,然后广播给其他CTI

◾CTI:cross trigger interface, 接收trigger信号,发送trigger信号,接收channel信号,发送channel信号

channel interface的典型应用。

每个coresight组件和对应的CTI相连,那这个CTI就可以采集组件的trigger信号,或者发送trigger信号给组件。

CTI将接收的trigger信号,发送到channel interface上,或者从channel interface上接收trigger信号,发送给和自己相连的coresight组件。

所有的CTI的channel interface和CTM相连,这样各个CTI就可以通过CTM,相互传输trigger信号。

1. channel interface信号

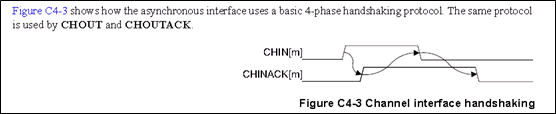

channel interface上传递的信号,使用握手机制进行信号的传递。不同CTI运行的时钟是不一样的,因此需要握手机制,来保证不同CTI之间能够相互传递event。

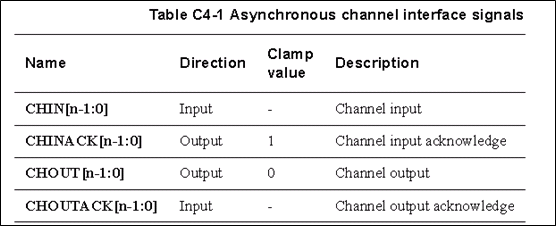

信号总共有以下4个,direction是相对CTI而言的。

clamp value,是指设备power down或者disable,output上的固定值。

以下是时序图:

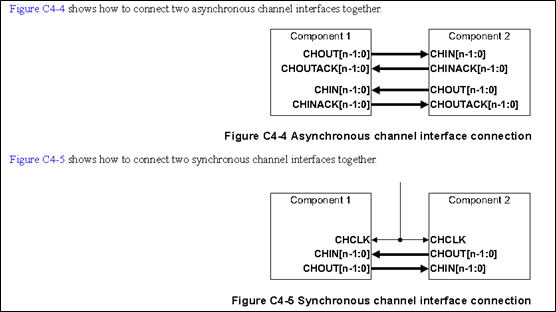

两种连接方式,异步的和同步的。

同步与异步接口之间的转换。

2. CTI

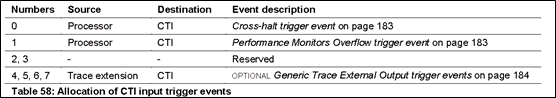

CTI有input trigger和output trigger。ARM对这些trigger均有定义:

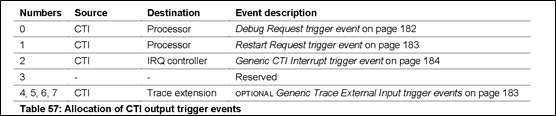

以下是output trigger:

trigger0: 连接CPU,debug request请求,当这个信号有效,表示使连接的CPU进入debug state。

trigger1: 连接CPU,restart request请求,当这个信号有效,可以使连接的PE退出debug state。

trigger2: 连接中断控制器,CTI interrupt, 当这个信号有效,会发出CTIIRQ信号,给中断控制器发送中断。

以下是input trigger:

trigger0: 连接CPU,cross-halt trigger,当这个信号有效,表示连接的PE进入debug state。

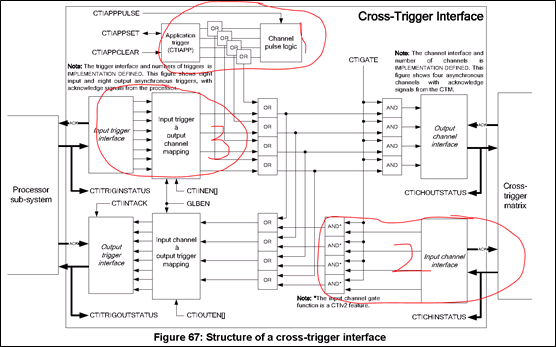

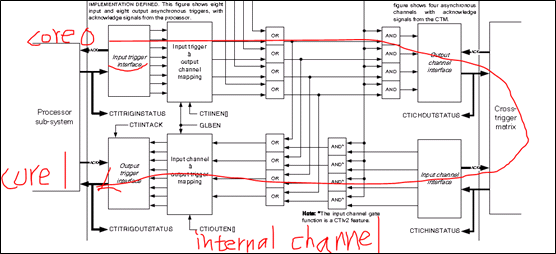

以下是CTI的内部结构:

CTI左边连接CPU,有2个通道,一个是接收CPU发送的input trigger,一个是发送给CPU的output trigger。

CTI右边连接CTM,用于发送output channel,以及接收input channel。

CTI接口信号共有4种:

◾Input triggers: trigger event inputs from the processor to the CTI。trigger信号从PE发出给CTI。

◾Output triggers: trigger event outputs from the CTI to the processor。trigger信号从CTI发出给PE。

◾Input channels: channel event inputs from the CTM(cross-trigger matrix) to CTI。channel信号从CTM发出给CTI。

◾Output channels: channel event outputs from CTI to CTM。channel信号从CTI发出给CTM。

input trigger & output channel mapping:根据CTIINEN信号,将input trigger,连接到指定的output channel上。

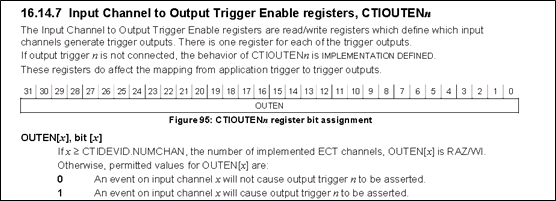

input channel & output trigger mapping: 根据CTIOUTEN信号,将input channel,连接到指定的output trigger上。

对于每一个output trigger,有单独的寄存器和其对应,如CTIOUTEN0,就和output trigger0对应,控制该寄存器,就可以将指定的input channel连接到output trigger0上,这样指定的input channel上的trigger就可以传递到output trigger0上。

寄存器有32位,表示可以从32个input channel中选择一个(armv8的输出trigger最多32个)。如果寄存器的值为0x1,就表示将output trigger0连接到input channel0,如果寄存器的值为0x4,就表示output trigger0连接到channel2。

对于CTI,可以接收三种输入信号,一个是core的trigger inputs,一个是CTM的input channel,另一个就是外部debugger通过APB访问的寄存器从而产生的trigger信号。

总共有3个来源:

◾CTI内部逻辑的CTIAPP,外部可以通过APB总线访问

◾外部的CTM

◾CPU发送的input trigger

2.1 对于CIT内部逻辑的CTIAPP

这部分提供了若干个寄存器,外部通过APB总线可以访问这些寄存器,从而控制发生,取消trigger信号。

外部的debugger可以控制这些寄存器,从而使对应的internal output channel有效,然后控制CTIOUTEN[],就可以使internal output channel的数据输出到指定的output trigger上。

以下是trigger走向图。

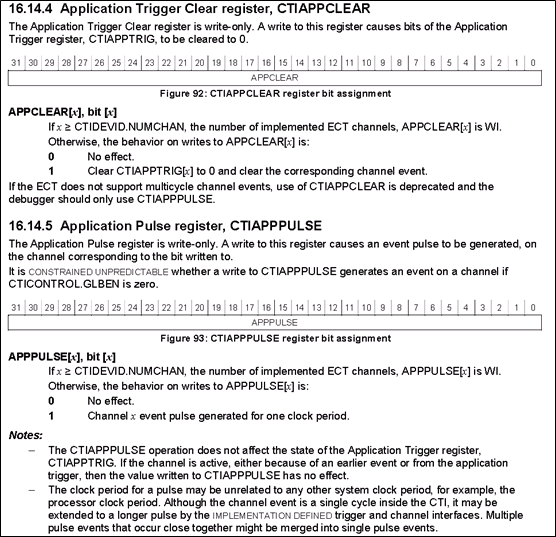

armv8定义了3个寄存器,CTIAPPSET,CTIAPPCLEAR,CTIAPPPULSE。

◾CTIAPPSET:指定的internal channel上产生channel event

◾CTIAPPCLEAR:指定的internal channel上取消channel event

◾CTIAPPPULSE:指定的internal channel上产生只持续一个周期的channel event

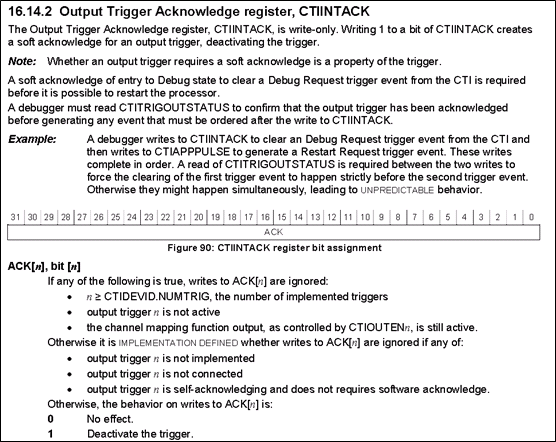

CTIINTACK。这个寄存器,是用来控制将output trigger上的信号给无效掉的。比如,当前output trigger0是 有效的,表示debug request,那么如果要将这个debug request给无效掉的话,那么就可以往这个寄存器写0x1,就无效掉了。

寄存器的每一位对应相应的output trigger。

◾CTIINTACK[0] 对应 output trigger0

◾CTIINTACK[1] 对应 output trigger1

◾CTIINTACK[2] 对应 output trigger2

◾。。。

◾CTIINTACK[31] 对应 output trigger31

因为ARMv8规定了,output trigger的最大数目是32,因此也就用一个32位的寄存器就可以表示所有了。

2.2 外部的CTM

从core0发出的input trigger信号,通过output channel,然后通过CTM到达其他所有core的output trigger信号上的。

从core0发出input trigger信号,然后通过input trigger mux(通过CTINEN[]选择),到相应的internal input channel上,如果后面的AND与门打开,也就是CTIGATE信号有效,那么channel上的trigger信号就会通过output channel interface传输到CTM。

CTM将trigger,发送给其他core(这里是core1)的CTI外部input channel上,如果其他core的AND与门打开,也就是CTIGATE信号有效,就会传递到CTI的internal input channel上,通过output trigger mux(通过CTIOUTEN[]选择),通过output trigger,发送给core1。

以上就是CTI的不同core之间的trigger信号传递的机制。通过该机制,可以使一个core给另外的core发trigger信号,从而可以控制使其他core进入debug state,退出debug state等。

2.3 CPU发送的input trigger

接收CPU的input trigger,通过内部的output channel,发送给内部的input channel上,然后在发送到output trigger上。

系列其他篇

原文首发于骏的世界博客

作者:卢骏.

更多Arm技术相关的文章请关注Arm技术博客极术专栏,每日更新。