在本系列的第一章和第二章中,我探索了如何设计可靠电源传输网络和这些网络各个要素的作用以及Arm Research如何集中精力利益最大化此类网络。在第三章也是最后一章节中,我将更详细地讨论这项工作。

在Arm Research中,我们设计了一种可以直接对电源轨进行采样的片上数字存储示波器。示波器提供的内省功能可以使系统设计人员探测到任何由于电源传输劣势导致的潜在运行缺陷。此外,示波器的读数也可以用来驱动学习算法,自动生成电压噪声矢量用于保护频带生成系统。

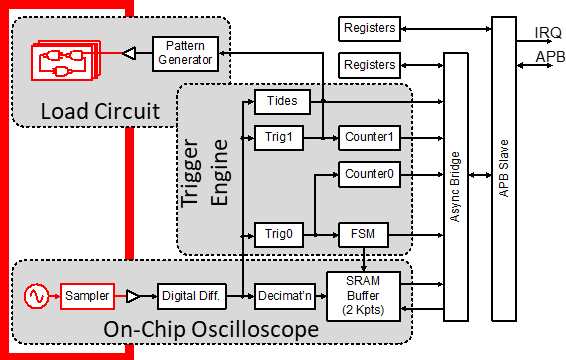

图1:片上数字存储示波器

图1显示了片上示波器的结构。它由一个基于VCO的电压采样电路组成,通过采样环形振荡器(RO)的频率来计算电源电压。额外的触发逻辑可以将电压“欠冲”或“过冲”与预先设置的阈值进行比较,并将产生的电压波形存储到芯片上的SRAM缓冲区中。事件计数器和潮汐标记可以提供关于电源噪声条件的额外统计信息。此外,示波器提供的一种负载电路可以利用已知的刺激(stimulus)作用于片上PDN。通过测量刺激的响应,可以表征PDN并测量其一阶共振频率等参数。

在动态运行期间,电源噪声条件的可见性对解决电源输送问题大有帮助。不幸的是,这种专门的电路还不是大多数高端Arm系统的标准功能。在我们最近与塞浦路斯大学的合作研究中,我们成功地开发了一种更通用的方法来监测处理器中的电压噪声。这种技术依赖于使用外部天线和频谱分析仪的处理器发出的电磁(EM) 辐射中的传感调制。由于程序活动导致的时变电流消耗,每个CPU都充当一个辐射天线。因此,这种方法可以扩展到目前不支持直接测量电压噪声的任何平台。

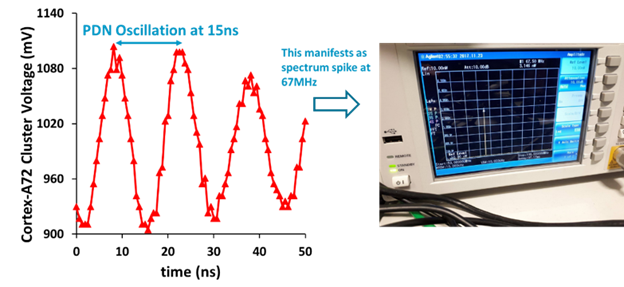

在图2中,我们在频谱分析仪上捕获了Arm Juno-R2平台的电磁辐射轨迹。果然,电磁辐射的频率与芯片上传感器捕获的电压噪声的主频率相匹配。

图2:用片上传感器捕获的电源噪声轨迹显示在左图。轨迹的频率(67MHz)完全符合使用外部频谱分析仪捕获的电磁辐射。

我们的研究表明,如何捕捉这些调制的辐射能量可以揭示系统的关键动态特性,如确定其固有共振频率。系统谐振频率是计算集群电源门控状态的强大函数。例如,在多核配置中,功率门控对应的核心大大降低了电网中可用的片上电容量。这导致了系统共振频率的急剧变化—一个可以在电磁频谱中捕捉到的强信号。

该技术是非侵入性的,因为它不会与被监视的CPU进行物理交互。因此,它为计算机体系结构开辟了一种全新的方法来表征和基准化高端系统。这项研究的论文发表在IEEE计算机体系结构快报(CAL,December Issue)上,被公认为2017年CAL出现的三大论文之一。我们应邀在2018年高性能计算机体系结构大会(HPCA)上介绍了这项研究,并在大会上获奖。

论文直达链接:http://cs.ucy.ac.cy/carch/xi/papers/micro\_web.pdf

该作品的一个扩展版本在日本福冈的MICRO 2018上发布并由Zacharias Hadjilambrou介绍。Zacharias是塞浦路斯大学的一名博士生,自2013年以来,他已在Arm Research实习了5年。

演讲直达链接:https://www.youtube.com/watch?v=h8ffKZZ\_KEI&feature=youtu.be

EM研究是由Project UniServer资助的EU H2020项目。Project UniServer研究电源噪声对企业级Arm系统的影响,并寻求开发低开销的缓解方法。如果你想要关于这个项目的更多信息,请直接联系我。

作者:Shidhartha Das

翻译:Khorina

原文链接:https://community.arm.com/developer/research/b/articles/posts/power-noise-introspection-for-accurate-margining-2

欢迎大家点赞留言,更多Arm技术文章动态请关注极术社区Arm技术专栏。