加紧学习,抓住中心,宁精勿杂,宁专勿多。

-- 周恩来

作为目前全球最大的IP供应商,ARM在芯片功耗控制方面也是做了很多的工作。刚好最近在看相关内容,今天就来扒一扒。

凡事都要师出有名,ARM先是起了一个听着就高大上的名字“功耗控制系统架构(power control system architecture,以下简称PCSA)”。在PCSA里面,主要规范的是逻辑实现,物理实现部分并没有在文档中过多的体现。换句话说,PCSA是给芯片架构师和前端设计师看的。至于物理实现,遵循S家和C家的流程。

在大规模的SoC设计中,可以设计一个硬件模块来完成顶层的功耗控制逻辑,好处是可以针对芯片的应用领域或者使用场景,做一些定制化的方案。但是,这种做法存在一些问题,首先是灵活性不高;其次,还要考虑该模块如何配合操作系统的功耗管理软件/驱动(OS power managent,以下简称OSPM)。

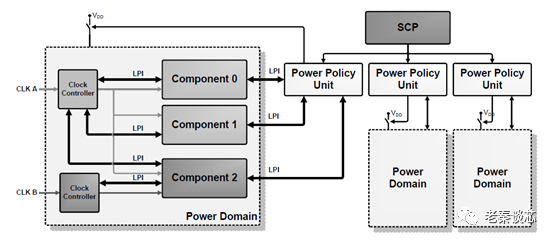

ARM推荐的做法是用一个微控制器加上一些外围逻辑,做成一个独立的单元--系统控制处理器(system control processor,以下简称SCP)。既然是ARM家的,这个微控制器就是M或R系列的了,你懂的。在SCP中完成SoC的功耗管理(当然,SCP不仅仅完成这个工作)。为此,ARM又定义了一大堆的接口,组件和协议来配合,统称为“功耗控制框架(power control framework,以下简称PCF)”。

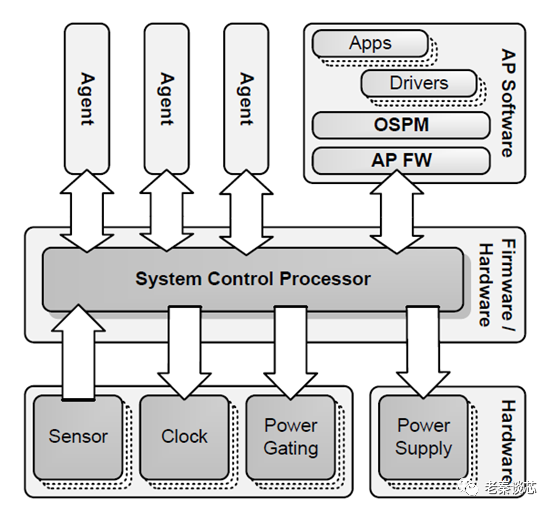

图1 SCP概念示意图

上图是ARM给出的一个带SCP的手机SoC系统方案。整个架构清晰明了,上层的应用处理器(application processor,简称AP)可以通过软件来给SCP发起服务(service)请求,左边Agent我们可以理解为其它子系统或者IP。作为中间层的SCP是由一个M系列的处理器构成的子系统,负责运行固件软件(firmware),向上可与AP通过设定好的接口/协议通信,接收服务请求,向下控制硬件单元,监控传感器,控制时钟和复位,管理电源等等。有了SCP,就能把一些任务从OSPM中抽离出来,更好的把软件和硬件隔离,增加了灵活性和安全性。SCP可以设计成层级式,分布式的,主SCP负责与上层通信,并控制子SCP。每个子SCP各司其职,控制不同的子系统或者是完成不同的任务。在实际项目中还没有见到这种分级SCP的设计方法,可能在异构中有用。

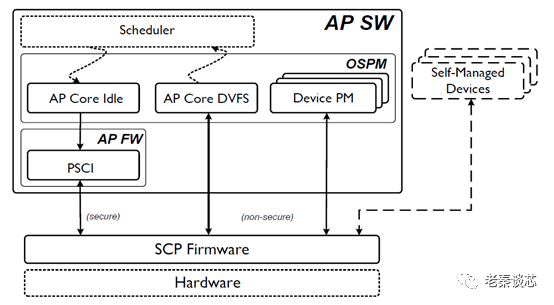

图2 简单功耗管理软件栈

上图是ARM给出的一个简单的功耗管理软件栈示意图,主要分为两部分,AP的功耗管理和设备的功耗管理。其中AP的功耗管理又分为idle管理和DVFS两部分。首先看idle管理,当AP处于idle状态时,OSPM可以根据需要关断时钟,下电且retention,或完全断电等多种操作。此时要保证断电的内核仍然可由操作系统进行调度,并且可以被中断唤醒。还有另外一种技术hot-plug。在这种情况下,AP核心将从操作系统可用于调度的池中移除。通过这种技术,内核被关闭,所有中断和软件线程被迁移到其它内核。这种技术既可以按需求比例使用,也可以在计算能力因功耗或散热受到限制的情况下使用。DVFS的基本概念就没啥可说的了,看过之前文章的同学应该都知道啦,《SoC设计之功耗 -- DVFS》。

设备的功耗管理可以是操作系统来控制(需要有驱动支持),也可以是自己控制,取决于具体的设计需求。

关于SCP固件的编写,可以参考ARM的官方文档,这部分留待以后再扒。

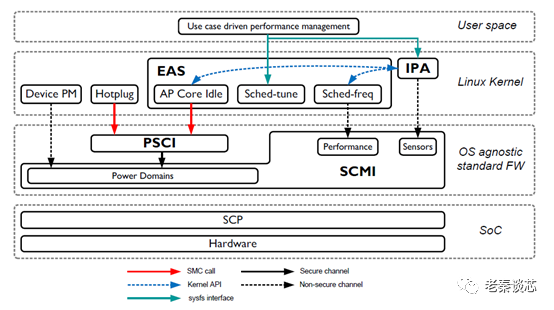

图3 Linux电源管理软件栈示例

在Linux内核中,EAS(energy aware scheduling)为内核调度提供了与内核空闲和集成频率控制的紧密联系。EAS还与使用IPA(intelligent power allocation)的热管理解决方案相关联。最后,EAS和IPA都与用户空间性能管理界面相关联。

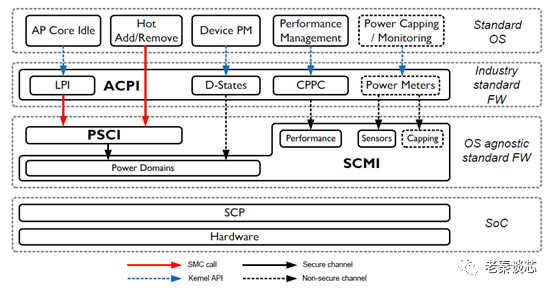

图4 系统基础电源管理软件堆栈示例

系统的一个理想特性是操作系统独立于特定于平台的细节。这使得操作系统能够在不修改平台固件的情况下进行更新,甚至更改。类似地,这使得新的硬件平台能够运行未经修改的操作系统。高级配置和电源接口(advanced configuration power onterface, ACPI)是一个标准接口,在固件中实现,支持这种抽象。

估计很多人看到这里有点懵,一大堆的概念和名词,ARM到底想干什么?其实说白了,就是ARM配合着操作系统定义了一套自己的SoC功耗控制架构。如果是前端逻辑设计师,这块看看就好;如果是往系统架构设计方向发展,建议补一补操作系统的知识(别瞅别人,说的就是我)。

图5 PCF概念

根据ARM的定义,功耗控制框架(PCF)是标准基础设施组件、接口和相关方法的集合,可用于构建SoC功耗管理所需的基础设施。标准的基础设施组件包括电源、时钟和接口组件。上图中的LPI(low power interface)主要是指ARM的Q-channel和P-channel,前面有文章详细分析过Q-channel,忘了的同学可以往前翻翻,《SoC设计之功耗 -- Q channel》。

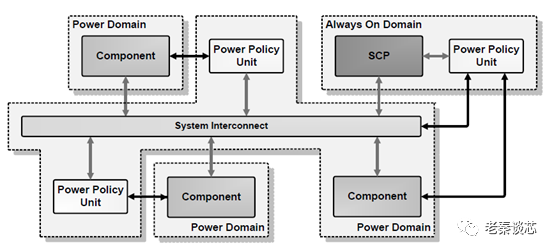

PPU(power policy unit)是一个硬件组件,支持SCP通过软件接口编程。

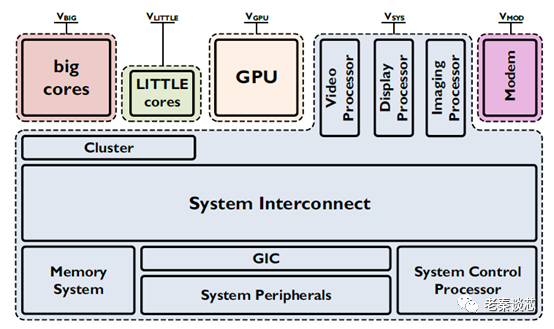

为了便于描述具体技术,ARM又区分了两个概念:电压域(voltage domain)和电源域(power domain)。电压域是指使用同一个电压源的模块合集,也就是说,如果几个模块使用相同的电压源,就认为这几个模块属于同一个电压域。ARM给出了几个系统电压域作为参考:

- 系统逻辑(System logic)

- 常开逻辑(Always-on logic)

- 处理器集(Processor Clusters)

- 图形处理器(Graphics Processor)

- 其它

图6 高端移动SoC电压域示意图

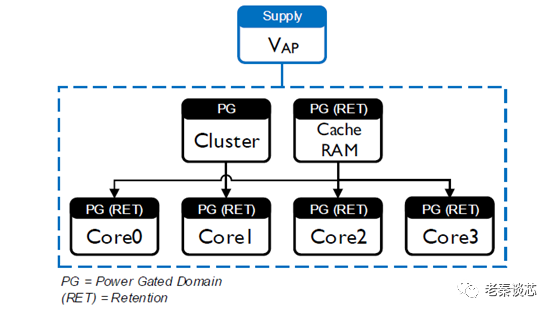

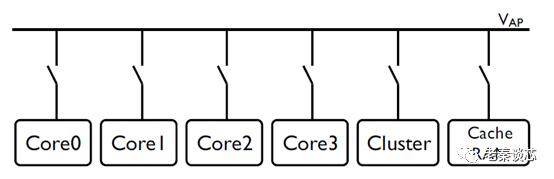

电源域是在同一个电压域内,共享相同电源开关逻辑的模块合集。就是说,在同一个电源域的模块被相同的电源开关逻辑控制,同时上电/下电(相对时间内)。一个电压域内的模块,可以根据设计需求,拆分到不同电源域。可以看出来,电压域的概念对应的是DVFS;而电源域的概念对应的是power gating。关于处理器的电源开关设计,可以参考下图:

图7 处理器电源域示例 – 逻辑视图

图8 处理器电源域示例 – 物理视图

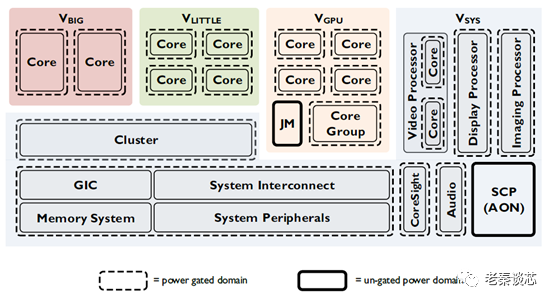

最后,放一张ARM的SoC电压域和电源域划分示例作为参考。不同颜色表示不同的电压域,比如VBIG是大核处理器的电源供电,VGPU是图形处理器的电源供电,VSYS是系统电源。虚线框包围的模块表示可以做电源开关处理,比如处理器核;实线框包围的模块表示不能做电源开关,比如SCP。

图9 SoC电压域和电源域划分示例

这套PCF看起来一大堆的东西,其实跟前端设计相关性大的只有SCP(如果UPF不用前端设计师出的话,哈哈)。SCP处于AP和底层硬件模块之间,起到了承上启下的作用。当然,再强调一下,SCP的作用不仅仅是为了功耗控制。

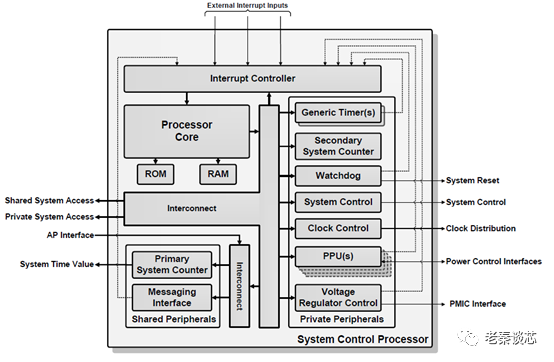

图10 SCP架构示意图

从上图可以看出,SCP是一个完整的小系统,该有的组件一个都不少。首先,SCP里面要有一个处理器,并且要具备足够的处理能力。比如要能够管理AP在idle状态下的功耗;要能支持中断,以及中断优先级排序;要支持调试功能;要能够可信操作,等等。既然有了处理器,那就要有ROM,用于安全启动,还要有RAM,运行固件时需要。如果要支持DVS,就要有图中的Voltage Regulator Control单元。为了配合DFS,还要有时钟控制单元,用于管理PLL以及输出时钟信号。Messaging interface适用于OSPM和SCP之间通信的接口,常用的有mailbox和doorbell两种方式。关于AP与SCP通信,有一套完整的协议来支持,以后有时间慢慢分析,先记住有这么一个接口就好。

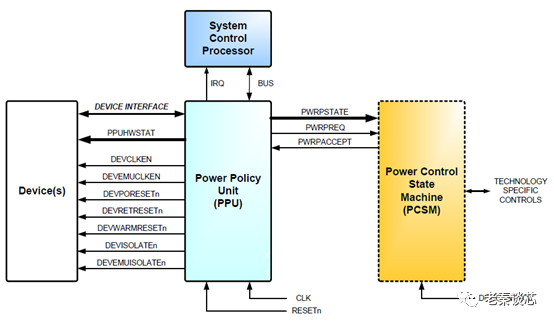

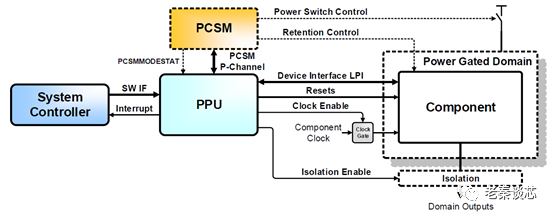

重点说一下PPU。PPU是为了控制SoC电源域用的,具体的数量和位置可以根据实际需要来定,比如可以做成分级式的或者分布式的。首先,PPU要提供一个配置接口给SCP,用于功耗策略控制和配置,目前用的是APB。其次,PPU与设备之间的控制接口,包括低功耗接口(low power interface,简称LPI),若干组Q-channel和一组P-channel,还有时钟/复位控制。最后,还有一个与功耗状态机之间的接口,P-channel。

图11 PPU接口

PPU在系统中的集成方式可以参考下图,虚线框包围的部分表示该模块依赖具体实现。

图12 PPU在系统中集成示意图

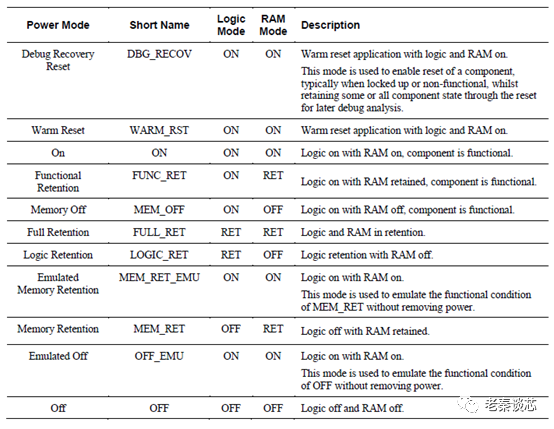

PPU支持的power mode如下,其中ON/OFF/Warm Reset是必须支持的,其它备选。各种mode之间的切换,PPU配置,寄存器说明等细节请参考PPU的文档。

其实个人感觉,PPU设计的有点复杂了,完全可以根据项目需要设计一个相对简洁的版本。

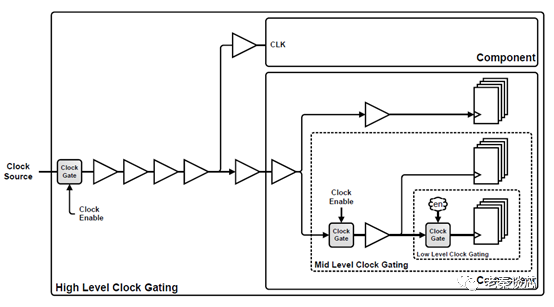

关于时钟,电源和复位的控制,ARM有如下的建议。先看时钟门控部分,首先分为三级控制,high,mid和low。这个理念并不是ARM提出的,忘记基本概念的同学可以翻看前面讲clock gating的文章,《SoC设计之功耗 -- Clock Gating》。

图13 clock gating设计层级示意图

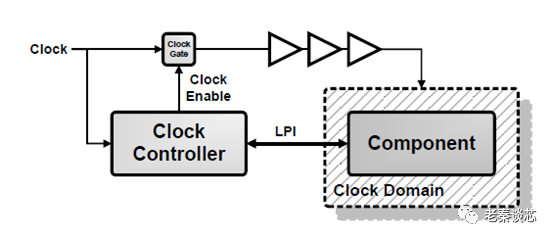

我们只看high level的,受控组件通过Q-channel与时钟控制器进行握手,一旦握手达成,时钟控制器给出控制信号,决定是否要关断时钟。这里再次强调一下,Q-channel和P-channel就是一组用于时钟/功耗控制的握手接口,必须要有其它控制逻辑。

图14 clock gating逻辑设计示意图

电源控制部分和时钟部分类似,就是多了一个上面提到的PPU。多提一句,PPU可以与被控制部分放在一起,也就是分布式设计,如下图。

图15 分布式PPU设计

好了,现在闭上眼想一下,如果你的SoC里面同时有异步时钟,clock gating,DVFS,power gating,顶层设计和物理设计是不是会很复杂?你品,细品,慢慢品。

其实ARM也给了一些相关的设计建议,一方面这些建议基本都是现阶段业内的标准做法,并没有太多的新奇东西,另一方面图也比较多,所以就不贴了。想了解这部分细节的同学请去翻ARM的文档吧,哈哈。

今天先扒一半,还剩下一半内容,主要是关于ARM的IP在PCSA里面怎么考量,以后再扒。

作者:老秦谈芯

来源:https://mp.weixin.qq.com/s/r_lGWX_pT52f5kWkKUzolg

作者微信公众号

相关文章推荐

欢迎大家点赞留言,更多Arm技术文章动态请关注极术社区Arm技术专栏。